近些年随着锂电池技术的成熟,低压BLDC 控制器的应用需求显著增加。因为MOS 的开关特性较好,开关损耗低,所以低压BLDC 控制器更容易实现高开关频率,驱动高速电机。

本人一直从事BLDC 的软硬件开发工作,除了FOC 控制,对硬件设计也有一点积累。分几篇文章,来谈一谈大功率控制器的设计。

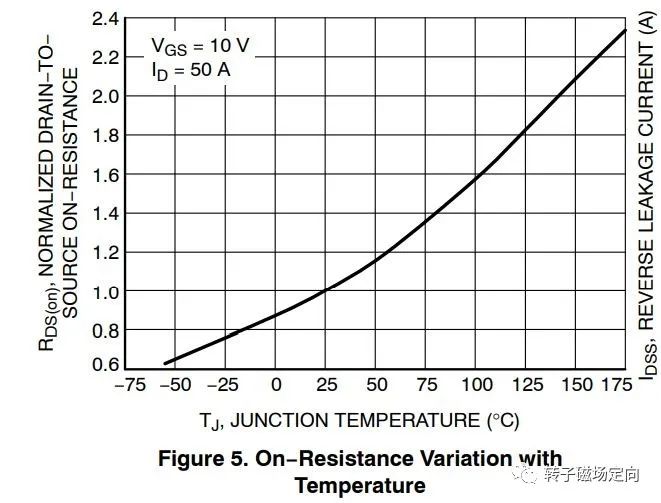

因为MOS是正温度系数,导致其适合并联的特性,所以低压BLDC 控制器可以用多MOS 并联实现大功率输出。当MOSFET 的结温Tj 逐渐上升,其DS 等效导通电阻Rdson 逐渐增大,那么并联中电流大的MOS 的导通电阻增大,让电流自动流向导通电阻小的MOS,进而实现了自动均流。

根据现在的市场热点,BLDC控制器包含以下应用:

12V: 3S 吸尘器、风扇、汽车水泵油泵;一般不超过300W

18V: 手持式电动工具,一般不超过1kW

24V~36V:吸尘器、扫地机、风扇、消费级无人机、滑板车等E-bike,割草机,工业风机、轴流风机、吊扇、水泵;功率一般不超过1kW

48V: 14s农业无人机、AGV、机械臂,植保机最大做到48V 7kW,机械臂做到48V 2kW,AGV最大做到48V 3kW

72V: AGV

108V~144V: Mini-EV 控制器,一般10kW以上

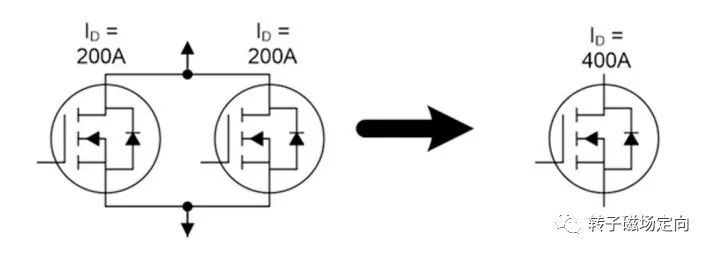

常见的大功率驱动器,常见多个MOS并联的拓扑。

并联的MOSFET 不可能有完全一模一样的参数,所以对驱动电路的设计以及MOSFET 的批量一致性存在较大的挑战。并联存在的最大问题便是均流,如果并联MOSFET 有一个承担了过大电流,极有可能造成的MOS 的失效。

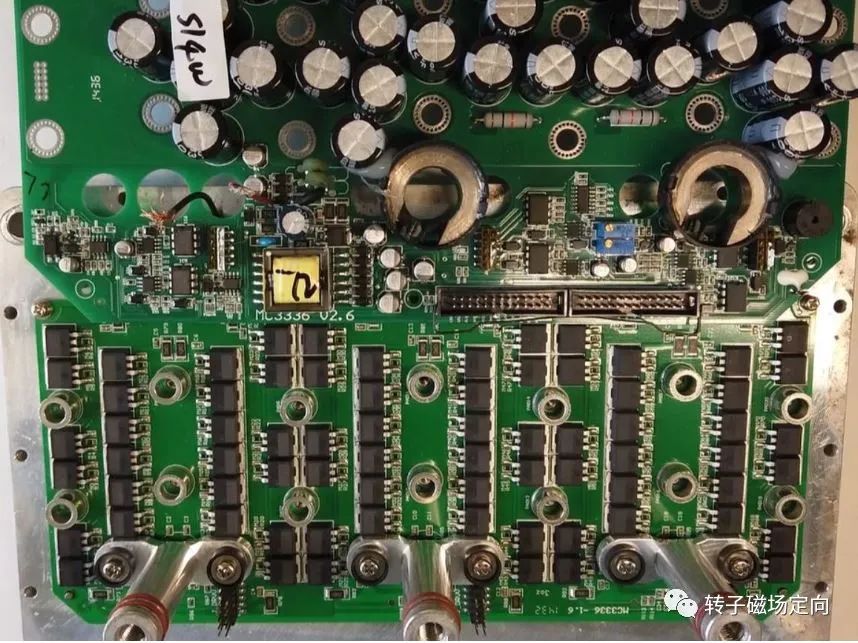

以下图为例:

上图即为某大功率电机控制器,采用MOSFET 并联方案,最多实现了12pcs MOSFET 并联。实际来说,本人见过最大实现14pcs MOSFET 并联的控制器。其均流就显得相当有技术含量。

MOSFET 的并联,公开的资料并不多,本人查阅了MOSFET 巨头英飞凌的官网,找到了一些相关的技术材料。

MOSFET 的并联如设计不当,可能会导致电流不均衡,损耗增加甚至失效。

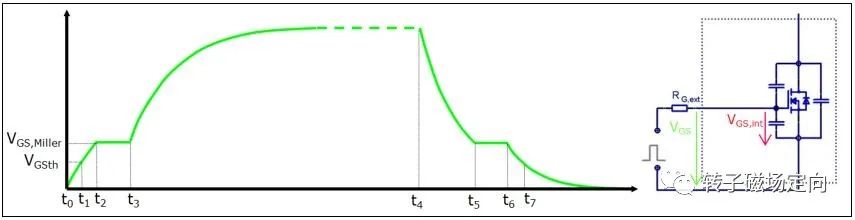

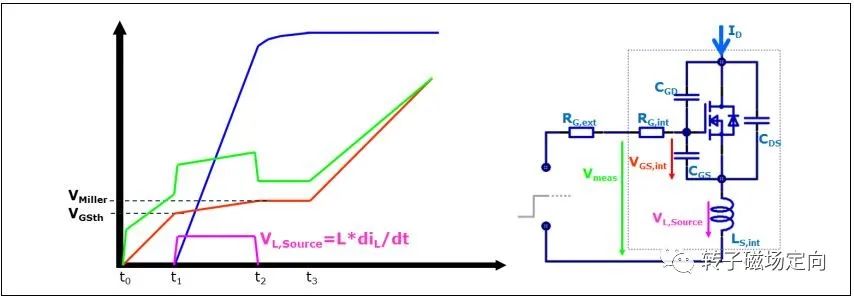

首先分析MOSFET 的开通过程:

t0:MOSFET 驱动电平从低翻转为高

t1: 驱动电平达到门槛电压Vgsth,漏极电流Id 开始上升

t2: 漏极电流Id接近最大值,驱动电平上升到了米勒平台

t3: 经过米勒平台,Vgs 继续上升到最大值

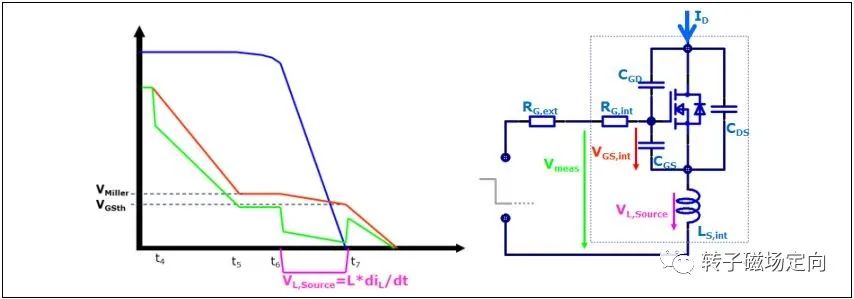

t4:MOSFET 驱动电平从高翻转为低

t5: 驱动电平下降到米勒平台

t6: 米勒平台结束,Id 开始下降

t7: Vgs 下降到门槛电压Vgsth,Id 降低到0

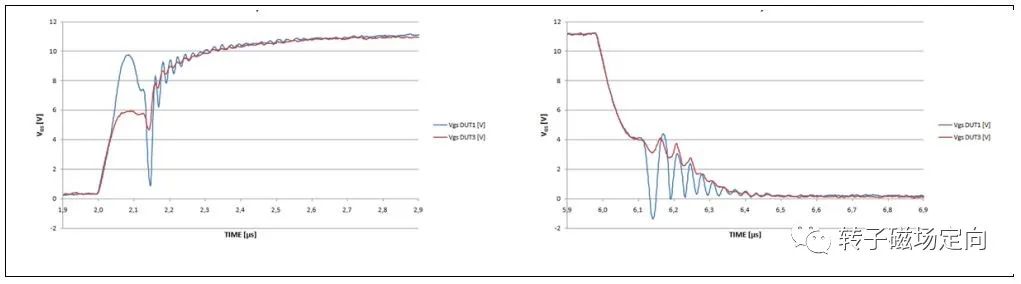

实际上,在MOSFET 并联的时候,并联的MOS 的Vgs 是不同步的,实际波形如下:

要分析原因,首先得详细的分析MOS 开通和关断的每个详细过程。

t0:驱动电平从低翻转到高,排除内阻RG,int,MOS内部驱动电压VGS,int (红色)开始缓慢升高。包含内阻部分的驱动电平 VGS,ext(绿色)存在突然上升和下降的过程。根本原因是RG,ext和RG,int的分压导致。

t1:VGS,int 达到门槛电压 VGSth,漏极电流 Id (蓝色)开始以一定的 di/dt 上升。di/dt在寄生电感上产生的源极电感(紫色)产生的电压叠加到了 VGS,ext 之上,从而产生了额外阶跃。

t2:漏极电流 ID 达到(接近)最大值,米勒平台开始出现。di/dt 降至零,所以叠加到VGS,ext的电压部分降到0,导致 VGS,ext 下降。

t3:越过米勒平台,VGS 继续升高至最大值。MOSFET 现在完全导通,完全上升到最大值的VGS 会导致 RDS(on)进一步降低。

t4:驱动电平从高翻转到低,VGS,int (红色)开始缓慢下降。VGS,ext(绿色)出现突然下降,根本原因是RG,int和RG,ext的分压。

t5:VGS,int 达到米勒平台,MOSFET 开始关断。

t6:漏极电流 Id(蓝色)开始以一定的 di/dt 减小。由寄生源极电感(紫色)产生的电压从 VGS,ext 中减去,从而产生了突变。

t7:VGS,int 达到阈值电压 VGSth,漏极电流 Id 降至0。di/dt 也为降至0零,叠加电压降到0,导致 VGS,ext 突然增大。MOSFET 完全关断。

所以说,为什么非平衡电路中,两个并联的MOSFET会出现较大差异的Vgs?是不同的源极寄生电感导致不同的感生电压叠加到Vgs上导致的。

MOSFET生产时,内部绑定线的组装,以及PCB走线,共同组成了源极的寄生电感。

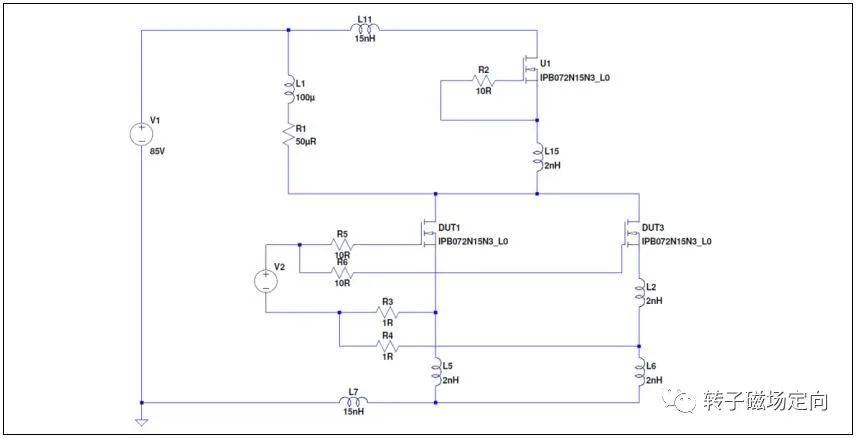

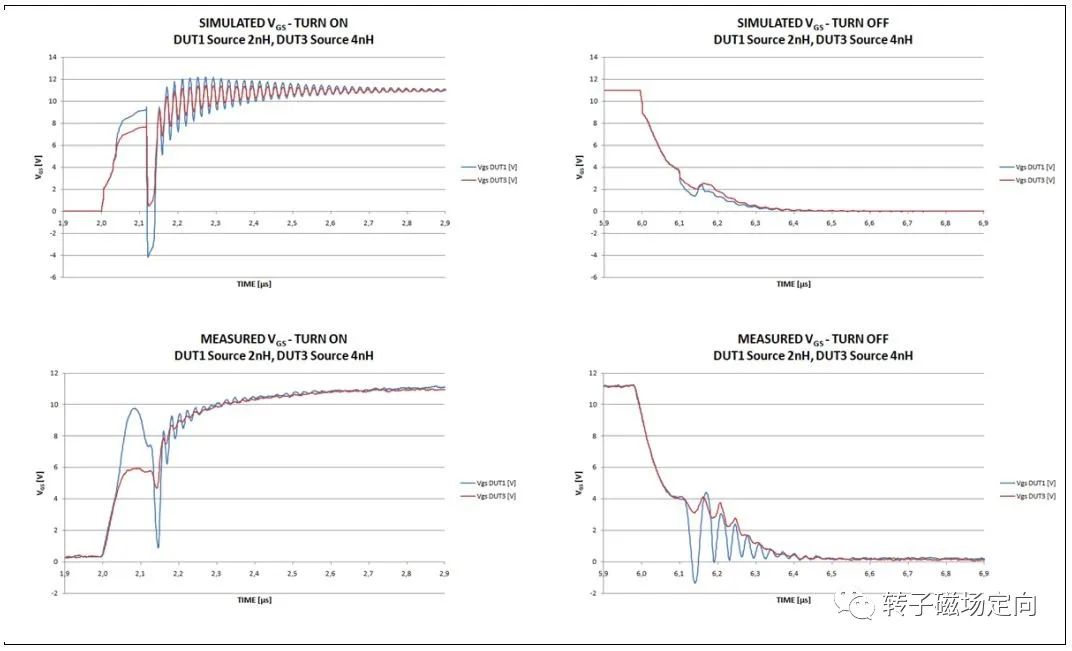

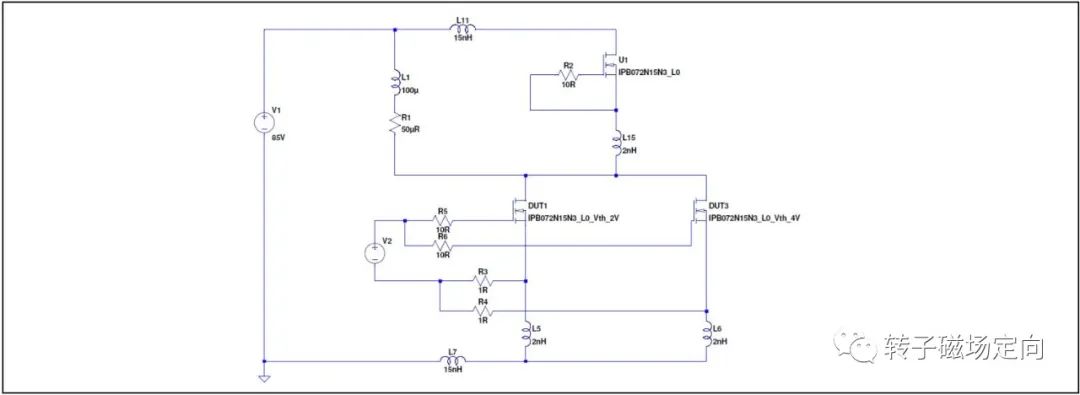

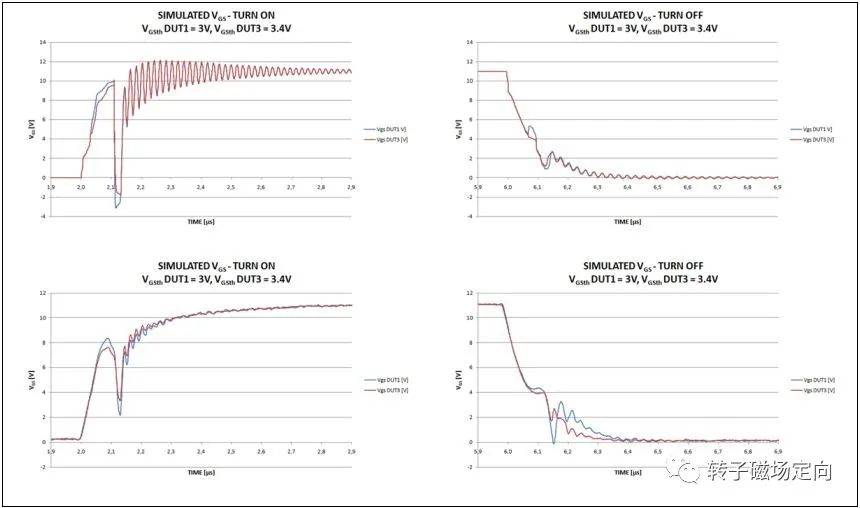

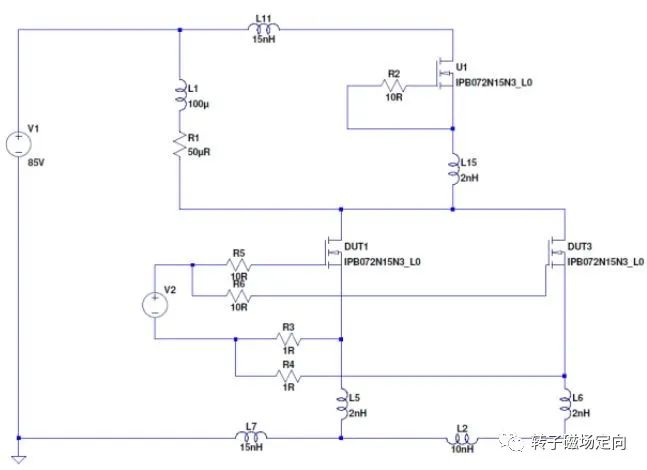

建立如上仿真模型,在DC- 增加15nH 寄生电感,DUT1 和DUT3 的源极都增加2nH寄生电感,同时考虑绑定线加工的差异,在DUT3内部增加2nH由绑定线产生的寄生电感。仿真和实测DUT1和DUT3的开关过程,如下图:

通过上图发现,仿真和实测的波形基本是符合的,因为绑定线2nH寄生电感的影响,导致DUT1和DUT3的驱动波形出现较大差异。

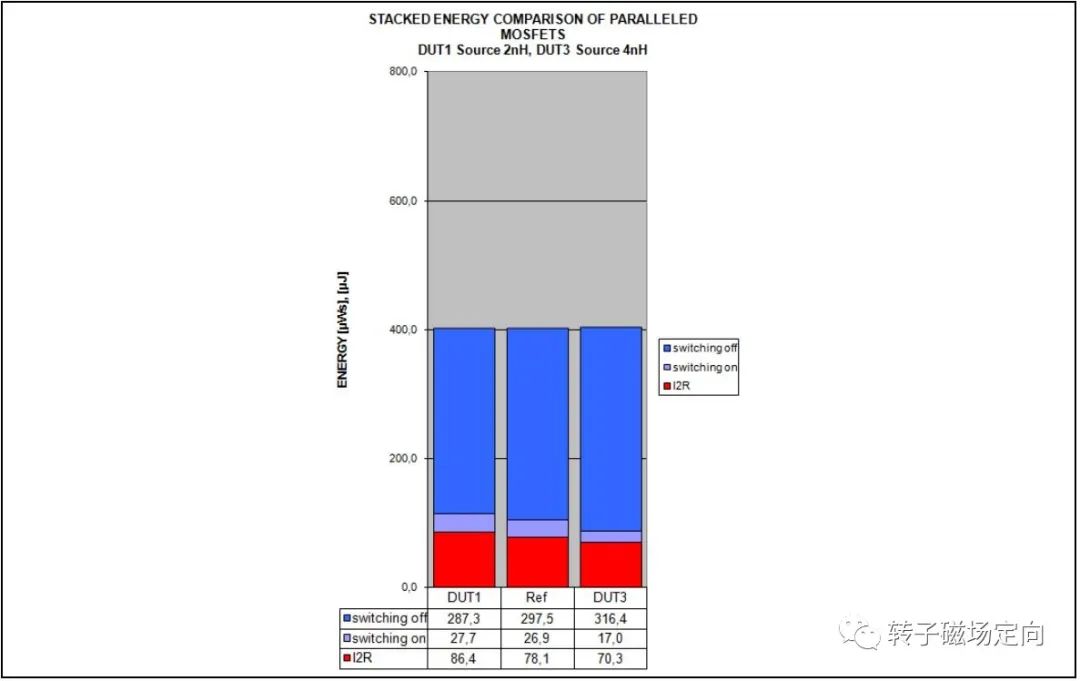

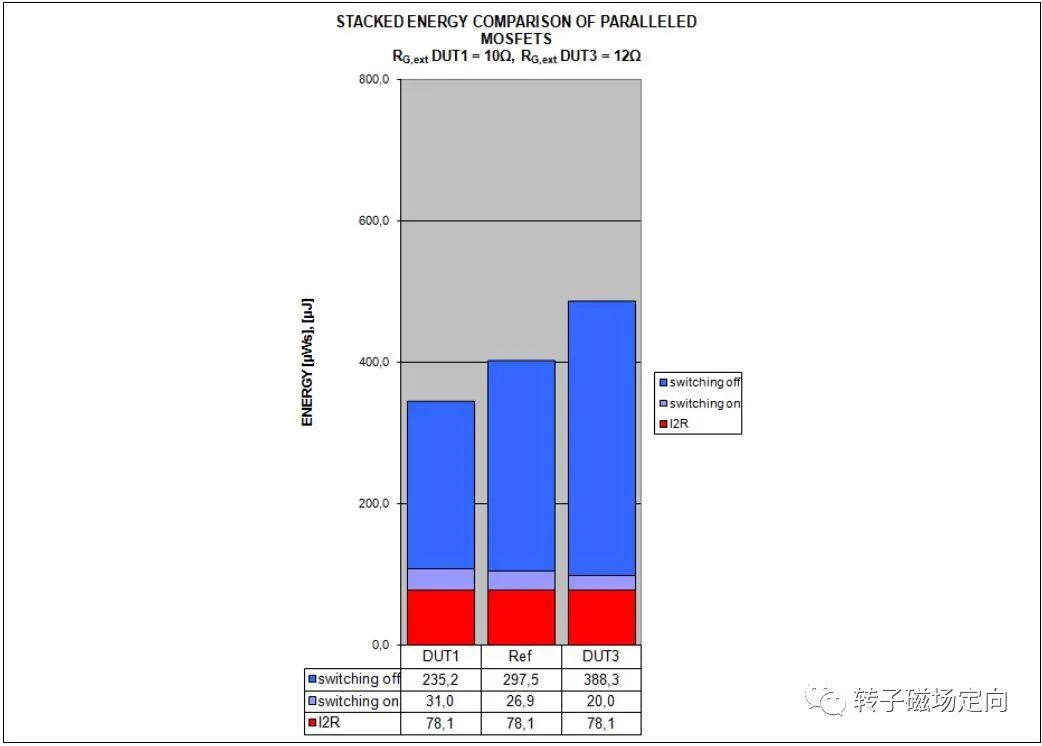

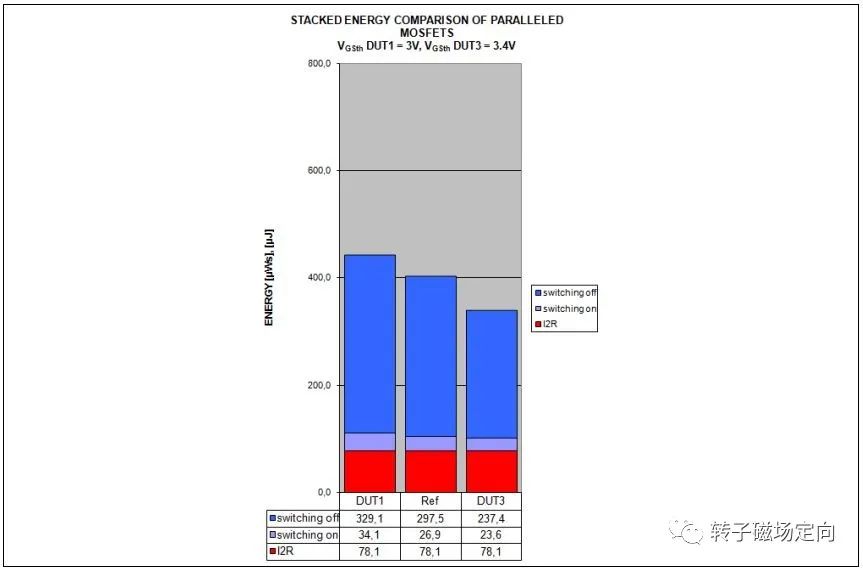

上图表明了DUT1和DUT3不同的损耗,包括开通,导通,关断损耗。测试结果是单次发100us开关脉冲所需的能量。

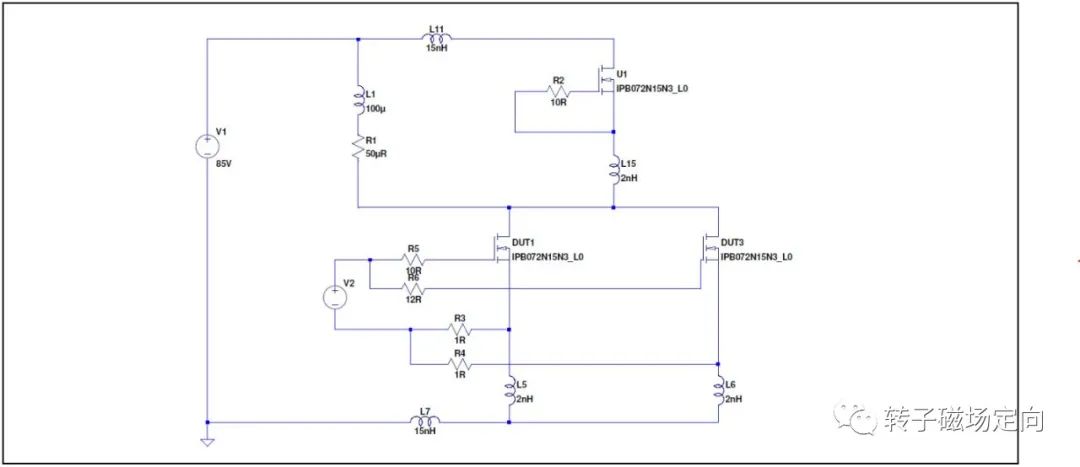

并联的MOSFET,因为RG的误差,会导致开关的不同步。假设11ohm的驱动电阻,有10%的误差,那么驱动电路等效如下:

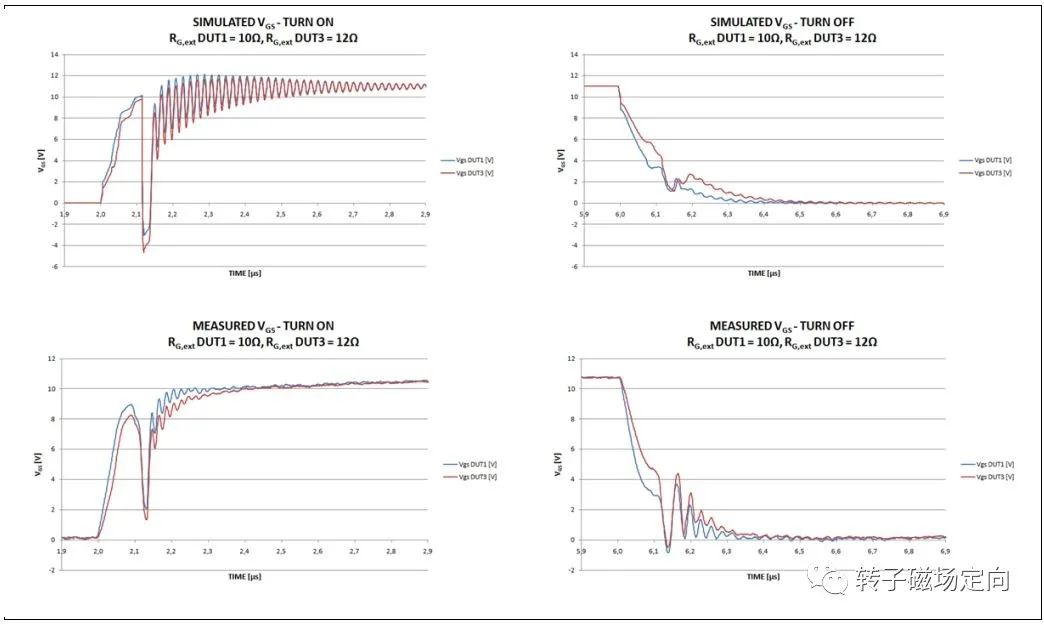

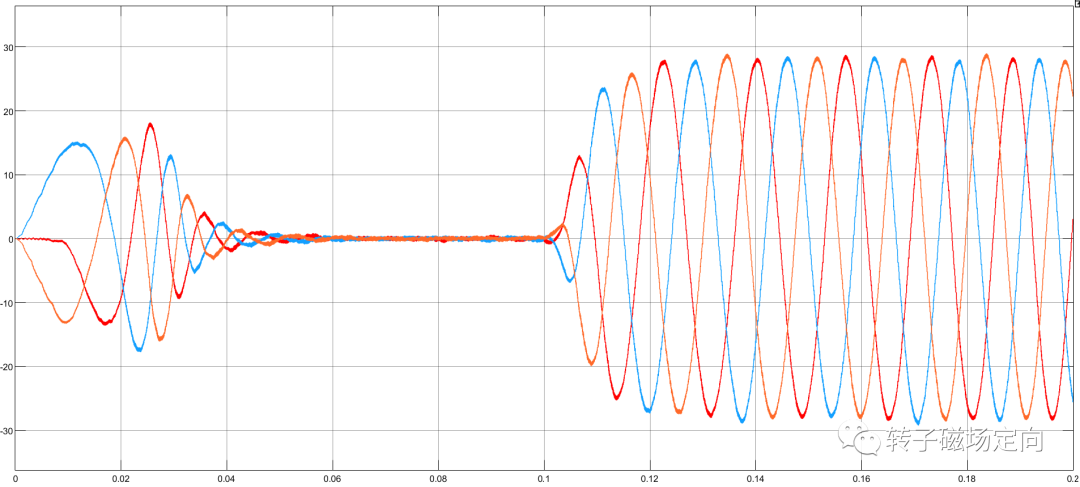

仿真和实测波形如下:

不同驱动电阻下,DUT1 和DUT3 的损耗如下图:

从上图发现,不同的驱动电阻,对开通损耗影响非常大,电阻越大,开通损耗越大。对关断损耗和导通损耗影响不大。

一般MOFET的Vgsth的典型值在3V左右,如下图:

假设并联的2pcs MOSFET,1pcs的门槛电压是2V,另外1pcs门槛电压4V,这是最极端的情况,那么建立如下仿真模型:

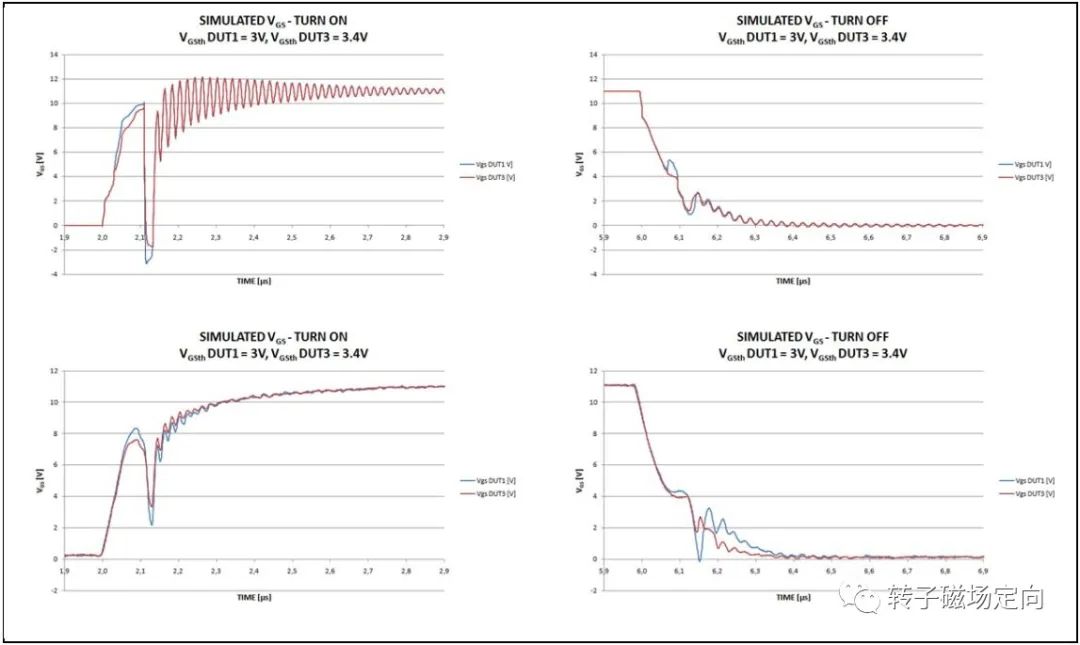

仿真和测试结果如下图:

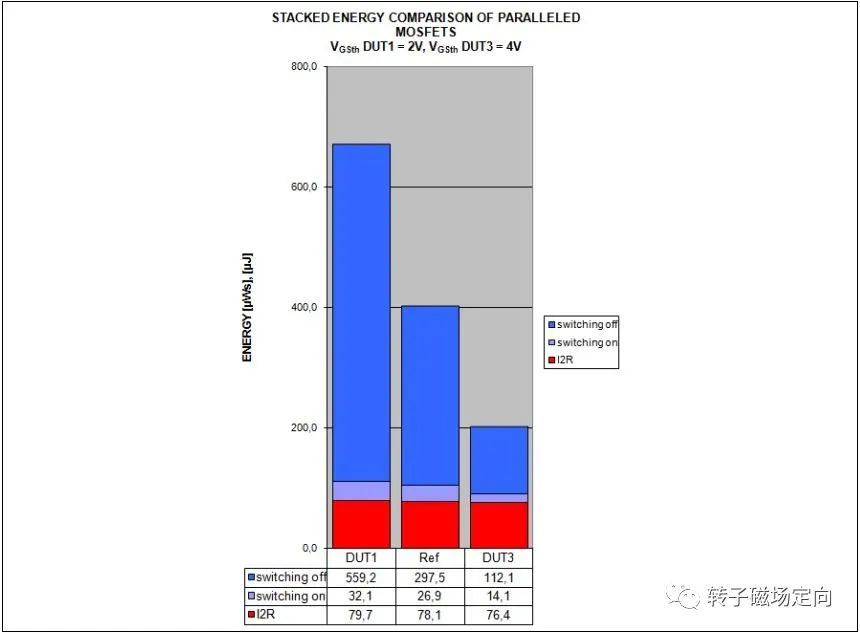

对比其损耗分布图如下:

不同的门槛电压,对导通损耗无影响,对关断损耗影响不大,但是对开通损耗造成了巨大的差异。因为根据前面分析的开通过程,当Vgs 达到Vgsth 的时候,其实MOS 已经开通了。所以对上述实验,当Vgs达到2V的时候,MOS 已经开通承担了全部电流,然后当Vgs 上升到4V 时,另外并联的MOS 才刚刚开通,严重的滞后导致其开通损耗远远小于提前开通的MOS。

如果选择同一批次供货的MOS,那么Vgsth的差异小很多。假设并联MOS 的Vgsth 差异只有0.4V,那么损耗的差异小很多。如下图,当Vgsth差异只有0.4V,开通损耗的影响就没有那么大了。

上图说明Vgsth差异0.4V对开关波形的影响不明显。

假设LAYOUT走线不均衡,导致产生了较大的线路寄生电感,那么建立如下仿真模型:

不均衡走线对开关波形的影响如下:

不均衡走线导致开关波形出现较大差异,尤其是对Id的影响,导致严重的开通过程中的不均流,如下图:

对损耗造成的差异如下:

不均衡走线,对开关损耗都造成了较大的差异,同时瞬态的不均流,给MOSFET 造成了较大的负载,存在失效的风险。

通过以上数据,包括仿真和测试,说明对并联影响最大的因素是Vgsth和LAYOUT布局走线。

那么针对Vgsth的差异,建议选用同一批次的MOSFET,包括绑定线寄生电感的差异,也可以通过这种措施来规避。批次一致性的管控能力也是对品质一项重要的评估指标。

至于驱动电阻的误差,一般来说选用高精度的贴片电阻即可,不会对损耗和开关波形造成明显差异。

针对LAYOUT布局,建议均衡走线,保证阻抗一致,同时MOSFET的外部驱动电阻,并联时建议分成两部分,一部分共用,另外一部分串联到每个并联的MOSFET。

下一期文章,分析一下采样电路,驱动电平的米勒钳位,LAYOUT布局的细节。

感谢您的耐心阅读。FOC提高班第三期已经正式启动报名,有意请私信。

行业杂谈:

为什么同一个公司搞管理的人一般要比搞技术的人收入高?

如何才能不让自己错过半导体的风口?

对个人而言,什么样的工作称得上是一份「好工作」?

为什么一些高学历还没低学历拿的钱多?

走进作者:

告别2022,展望2023

电机控制工程师如何拿高薪?

我的买房故事

月薪 4 万人民币是一种怎样的感受?

月入十万难吗?

专业文章:

什么是DPWM调制方式?

单电阻如何保护和采样有效值

解析NXP的无感FOC方案

Renesas无感FOC方案解析(上)

Renesas无感FOC方案解析(下)

德州仪器C2000还有市场吗?

2022年电控行业发展趋势

FOC学习的避坑指南

基于M0 MCU的无感FOC航模电机控制

MATLAB到底有多厉害?

基于磁链模型的非线性观测器