本文转载自《半导体行业观察》

感谢《半导体行业观察》对新思科技的关注

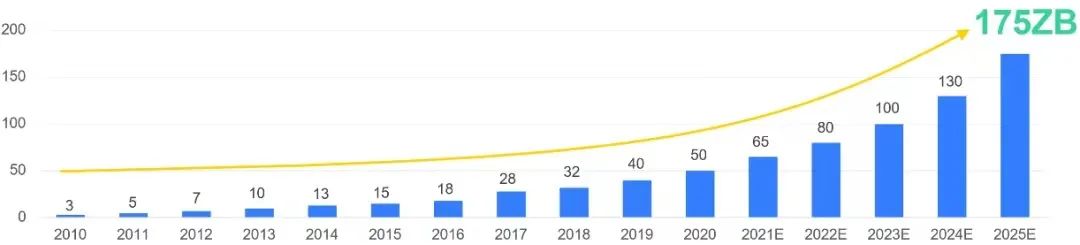

这些创新领域都需要处理大量的数据及计算。据IDC统计,2025年全球数据量将达到175ZB,对算力的要求每年增加10倍。换句话说,高算力的发展,成为支撑数字化世界的重要推手之一,是推动未来经济发展的重要指标与技术。

因此,高速接口技术开始得到广泛使用,比如DDR、LPDDR、PCIe、CXL等,接口上的性能在不断地提升,标准的演进和更新周期也在不断地缩短。

数据安全是重中之重

与之伴随而来的,是数据安全保护的重要性被提到了一个新的高度。因为随着新应用的出现,很多数据包含隐私、敏感信息,同时由于不同人的数据可能会存储在同一个资源池当中,这就给数据窃取、篡改,甚至是伪造带来了比较高的风险。

数据安全威胁来自四面八方。尤其随着当前密码分析技术、仪器自动化和量子计算等技术的发展,相比过去的攻击手段,攻击门槛已大大降低。

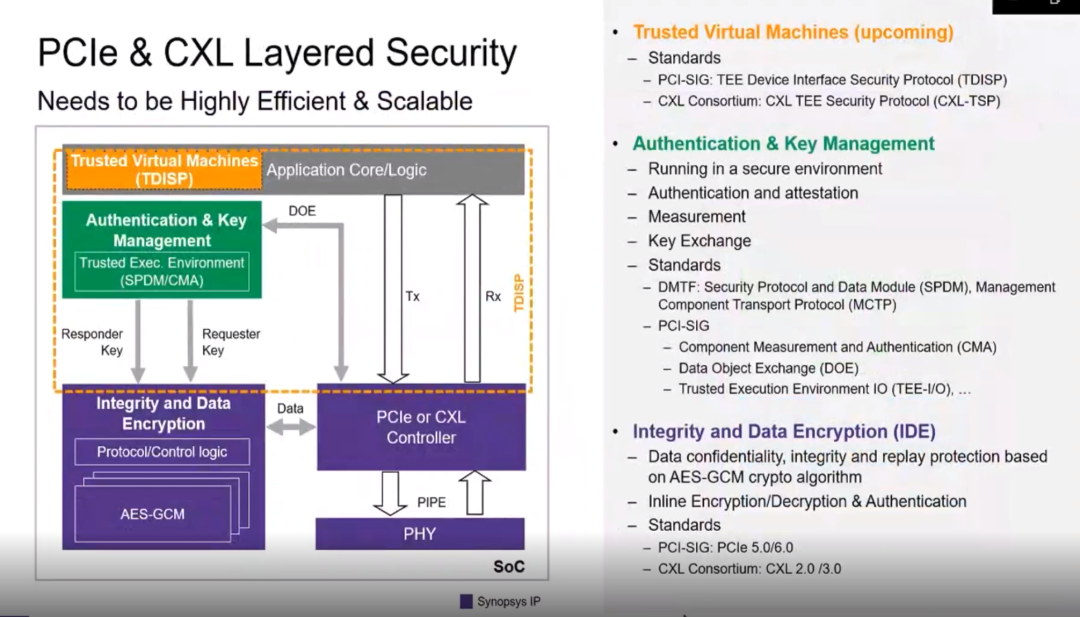

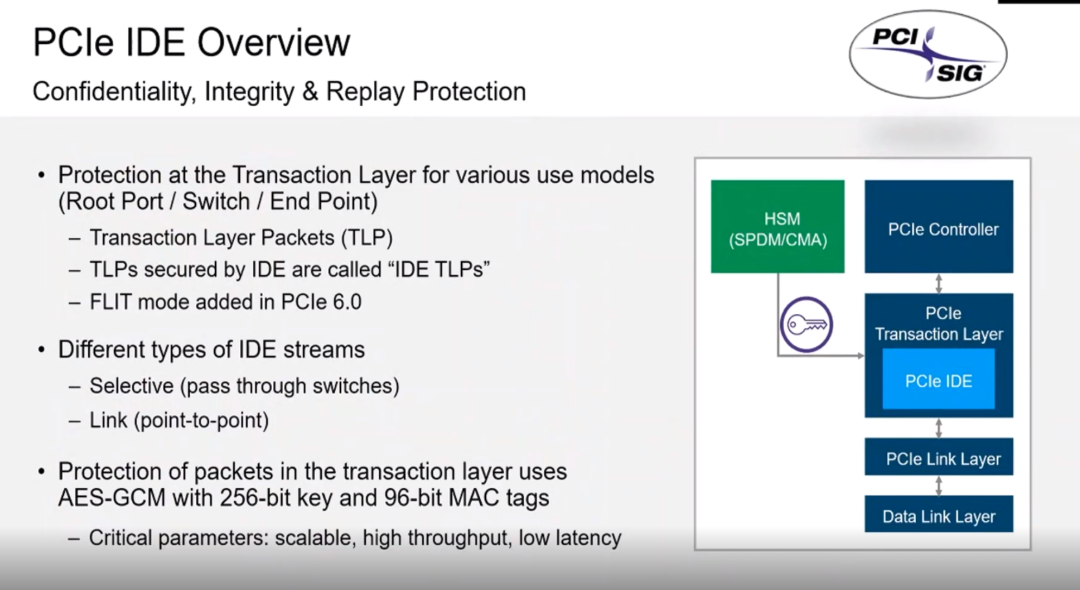

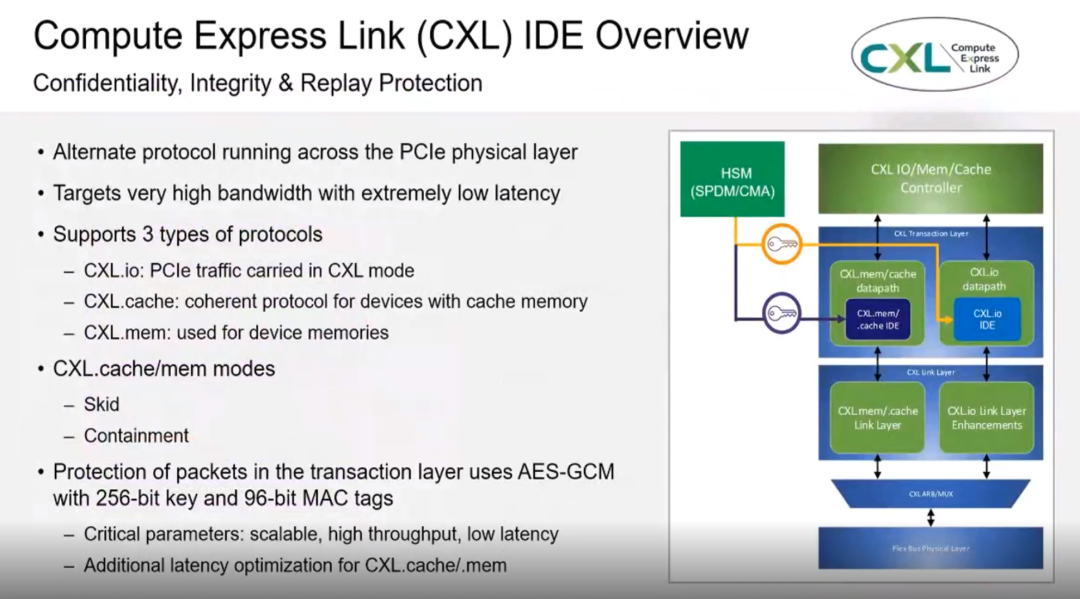

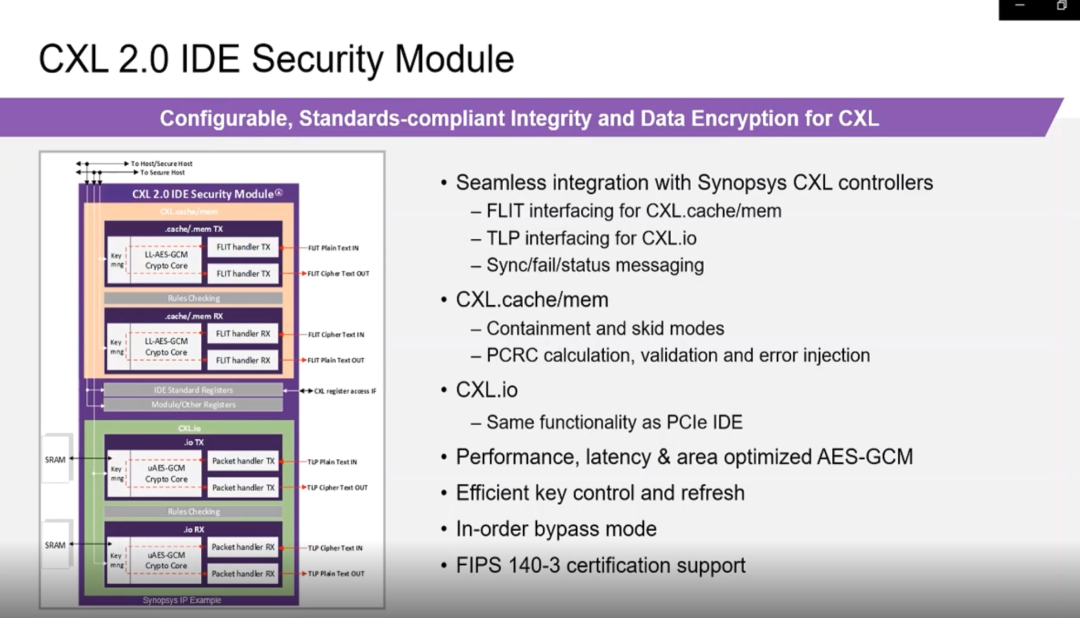

对此,通过政策法规和安全技术标准的演进,能够对数据安全问题加以限制和约束。以技术标准为例来看,PCIe和CXL组织在2020年底发布的最新标准当中首次加入了信息安全的功能——PCIe 5.0和CXL 2.0当中的IDE(Integrity and Data Encryption)数据完整性和加密保护。此外,下一代的PCIe 6.0、CXL 3.0当中的安全需求也得到进一步的强化。

这些都证明了数据安全接口的需求和重要性。除了最直观的性能、功耗、成本等指标外,数据安全作为一个重要的评判标准已经愈发成为了行业的技术共识。

高速接口成为

数据安全的关键

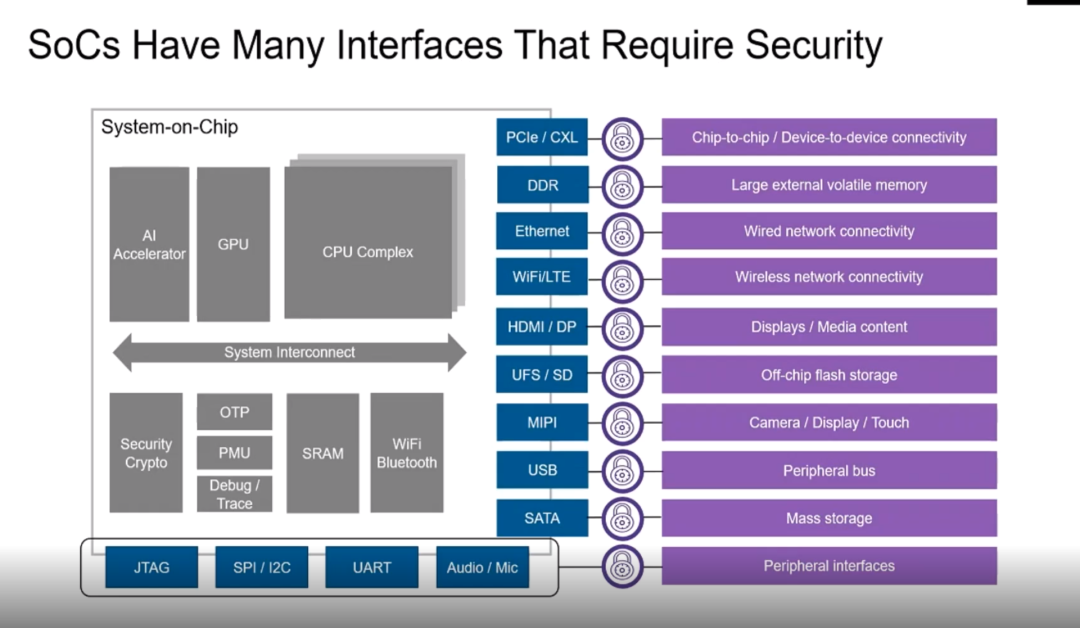

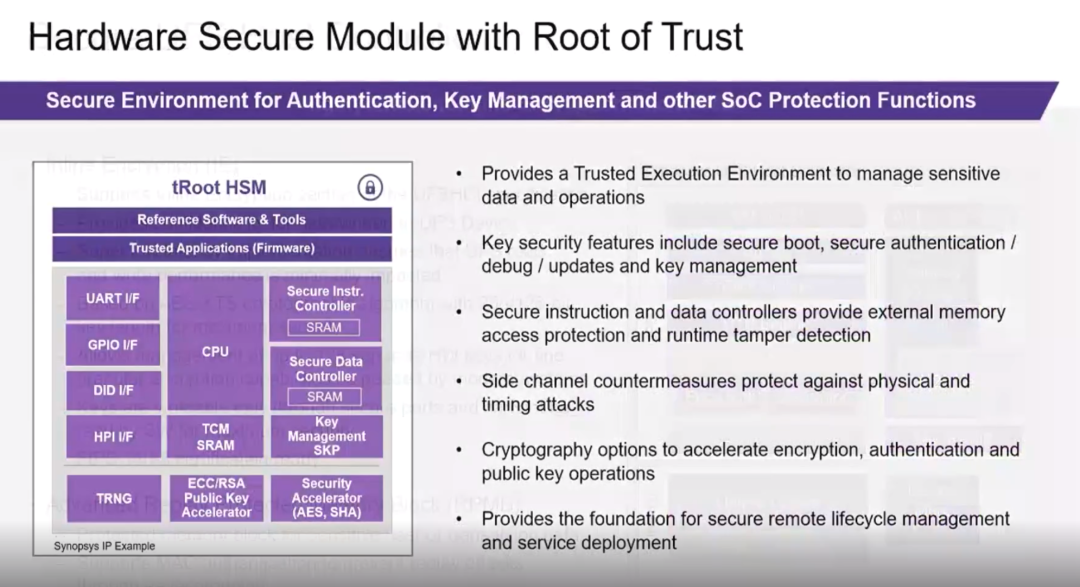

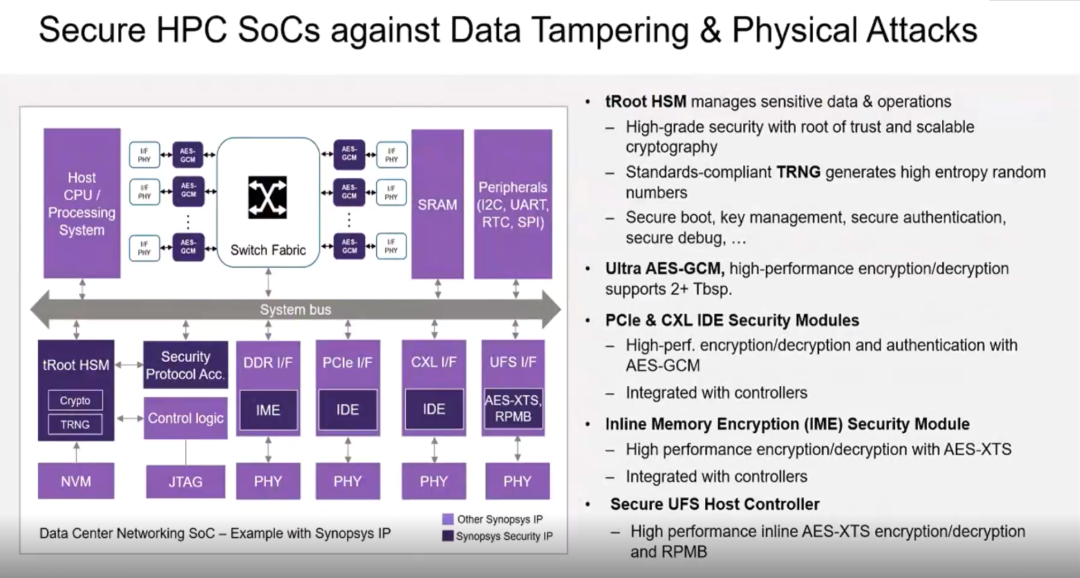

从芯片开发者的角度来说,为了有效地保护芯片内的核心资产和数据安全,SoC设计是实现安全的关键。面对上述可能出现的数据安全威胁,芯片开发者需要关注攻击技术的演进,尽早在芯片设计中提前做出应对。

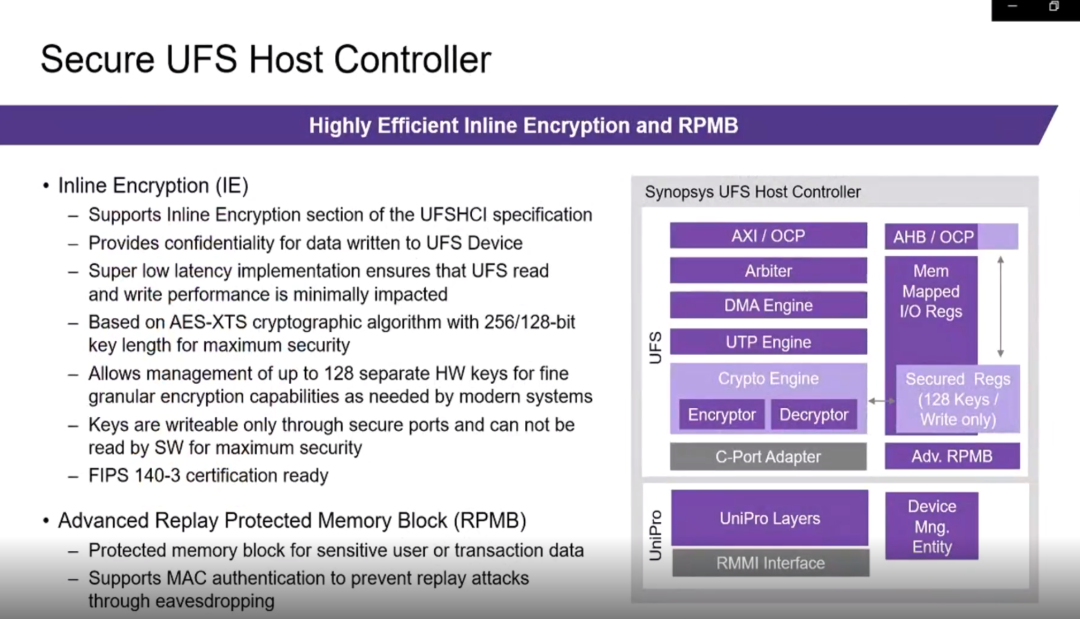

具体到芯片架构层面,各种接口作为芯片和外部世界的交互媒介,长期以来都是攻击者所关注的重要对象。行业最新的发展方向就是将安全功能融入到数据接口来实现传输和保护的高效结合。

如下图所示,芯片上有许多需要安全性的接口。