关键要点

・增加开关元件的栅极电阻会抑制噪声,但与之存在权衡关系的效率会降低,因此很好地权衡栅极电阻值的设置是非常重要的。

・将开关器件的损耗抑制在规定值以下时,其最大栅极电阻RG可以通过仿真来确认。

PFC电路:栅极电阻的更改

在实际的电路设计工作中,降噪是的一项重大课题,通常,可以通过提高开关器件的栅极电阻来抑制噪声,但其代价是效率降低(损耗增加),因此很好地权衡栅极电阻值的设置是非常重要的。在本文中,我们来探讨当将开关器件的损耗抑制在规定值以下时,最大栅极电阻RG的情况。另外,由于噪声需要实际装机评估,所以在这里省略噪声相关的探讨。

电路示例

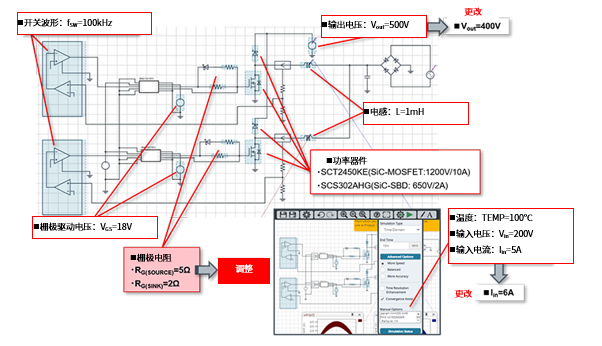

该电路以Power Device Solution Circuit/AC-DC PFC的一览表中的仿真电路“A-5. PFC CCM 2-PhaseVin=200V Iin=5A”为例(参考图1)。关于更详细的电路图,还可以通过这里查看。

在本示例中,我们将通过仿真来探讨将图1所示的低边开关器件SiC MOSFET SCT2450KE的损耗抑制在5W以下时,作为噪声对策可以将栅极电阻RG提高到多高。

图1:PFC仿真电路“A-5. PFC CCM 2-Phase Vin=200V Iin=5A”

栅极电阻与损耗的关系

如“PFC电路:探讨适当的栅极驱动电压”中图10所示,在导通状态下,传统Si(硅)MOSFET的导通电阻Ron相对于VGS几乎恒定。相比之下,SiC MOSFET的Ron相对于VGS变化很大(如图11所示),因此VGS值的设置比Si MOSFET更重要。也就是说,如果SiC MOSFET的VGS值过低,就会导致导通损耗增加,效率变差。反之,如果为追求高效率而将VGS设置得过高,则结果可能会超出额定值,因此设置适当的VGS值是非常重要的。

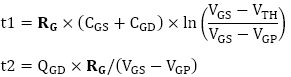

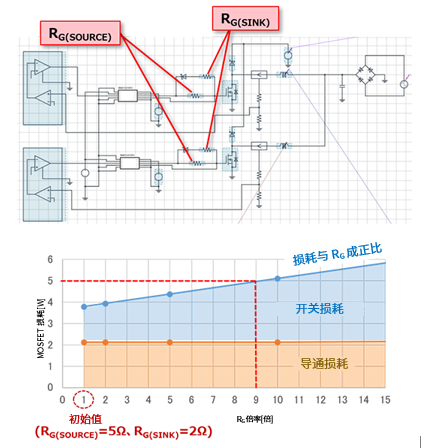

SiC MOSFET导通时的损耗、漏极电流ID、漏-源电压VDS和栅极电压VGS之间的关系见右侧图2。发生该开关损耗的期间t1和t2可以用下列左侧公式来表示:

图2:导通损耗与ID、VDS、VGS的关系

通过这两个公式可以看出,开关损耗发生的时间t1、t2与RG成正比。

另外,此时ID和VDS的变化几乎呈线性,所以可以认为损耗也与RG成正比。

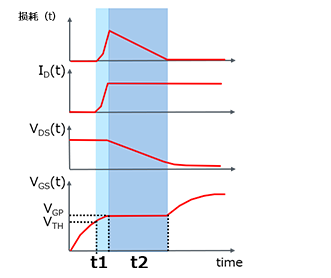

栅极电阻调整

图3表示使RG变化时SiC MOSFET的损耗仿真结果。为避免过于复杂,我们使Source用的电阻值和Sink用的电阻值以相同的倍率变化。

图3:改变RG值时的SiC MOSFET损耗仿真结果

技术资料下载

我们为您准备了ROHM举办的研讨会的讲义资料和DC-DC转换器的选型指南等可以下载的资料。

查看可以下载的资料清单

与“PFC电路:栅极电阻的更改”

相关文章一览

・PFC电路的优化

・Solution Circuit的PFC仿真电路

・PFC电路:电感调整

・PFC电路:开关频率的调整

・PFC电路:栅极电阻的更改

・PFC电路的优化 -总结-

END

更多内容

您可点击菜单栏

【干货推荐-内容中心】

前往获取更多资料~

点击阅读原文 了解更多信息