芯片界年度盛会ISSCC 2023于2月19号在旧金山重回线下召开,作为疫情之后的第一次线下全体大会,所展示出的最新技术、发展趋势等,非常值得关注。本文章会根据会议日程,结合short course, tutorials, technical sessions, forums, 实时更新参会学习心得和分析思考,希望大家批评指正!

2023 年的 ISSCC:概述

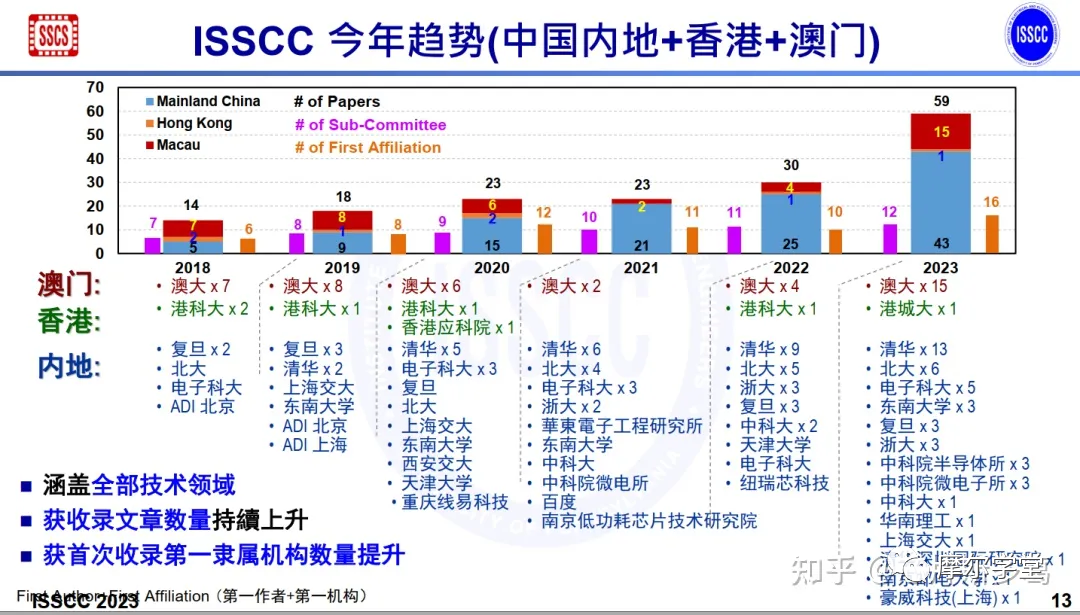

ISSCC 2023趋势

前沿芯片创新趋势分

根据 ISSCC 展望芯片创新趋势,一方面是通过跨领域 papers 分析新技术底层共性逻辑,另一方面是对比每年的Program会议日程有哪些新增、删减技术点。每个session的报告人和单位,也代表了在该技术领域的全球顶尖研究水平。

1、Walk in the middle of analog and digital

数字化是过去50年 ICT 技术发展的主基调,但在摩尔定律放缓的大背景下,通过工艺持续 scaling 提升芯片性能的技术路线已经逐渐难以为继。近年来,芯片设计趋势,尤其是计算芯片,已经从纯数字逐步向混合信号 mixed-signal design 发展,在 AI 芯片、量子计算芯片等领域尤为如此。那么,发展趋势变化的底层逻辑是什么呢?

贝尔定律指出 (Gordon Bell在1972年提出的一个观察),每隔10年,会出现新一代计算机(新编程平台、新网络连接、新用户接口、新使用方式且更廉价),形成新的产业。新一代计算机有全新的算力特点,向芯片提出新的需求,促使底层硬件芯片持续创新。不同时代的算力特点和需求决定了芯片产品开发模式的不断演进,这就表现为牧本定律(亦称“牧本波动”)。1987 年, 原日立公司总工程师牧本次生提出,半导体产品发展历程总是在“标准化”与“定制化”之间交替摆动,大概每十年波动一次 (参考资料:多核之后,CPU 的发展方向是什么?)。牧本定律背后是性能功耗和开发效率之间的平衡,这更多是通过产业界产品开发周期提炼出的规律。

在贝尔定律和牧本定律的基础上,我们探究底层芯片发展逻辑规律。评价芯片主要看PPA三个指标: power, performance, area. 在以CPU为主的通用计算时代,低功耗和高性能(高精度)是一对难以同时满足的目标,主要是高性能(高精度)优先。面向未来,AI 计算和量子计算正在成为 CPU 通用计算的有利补充,甚至是颠覆者。AI 计算和量子计算的一大特点是降低了对数据精度的需求,使得基于低精度、高噪声的模拟和混合信号芯片低功耗计算成为可能,低功耗和高性能在新一代芯片实现上达成统一。在此新的底层逻辑驱动下,一批创新文章方兴未艾,代表性文章有JSSC 2019、IEEE Solid-State Circuits Magazine 2021等。

展望未来,正如本次 Plenary talk 主讲人之一 Prof. Akira Matsuzawa所言:In the future, it will be important to develop computers such as AI processors and quantum computers whose operations are essentially analog, so mixed-signal technology is expected to develop even further.

2、From integrated-circuits to integrated-chips

在前文所述的底层发展逻辑变化的基础上,芯片已经从 integrated-circuits 转变为 integrated-chips,表现为模块融合、功能融合、芯片融合。三者互相支撑,由表及里,形成合力推动下一代芯片创新发展。

模块融合以不同场景下的需求为牵引,通过将传统意义上不同电路模块实现的功能,集成到一个电路模块中,实现功能融合、性能突破。模拟前端信号链处理 SoC 近年来的发展将这一技术趋势体现地淋漓尽致。

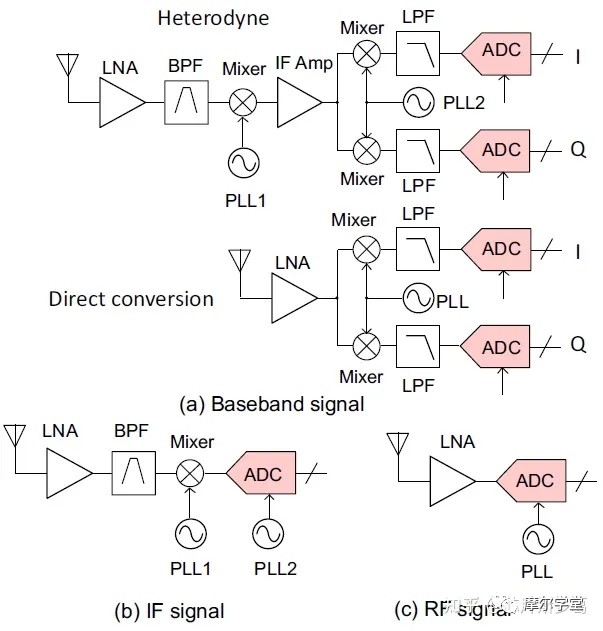

举例来说,对于无线通信场景,最新的技术趋势之一是将传统接收端 Mixer 的功能融入到 ADC 中,通过一个高性能 ADC 同时实现 A/D 采样和 RF received signal 解调,代表性参考论文有 JSSC 2020。

无线通信接收机中的模块融合 © 2023 ISSCC

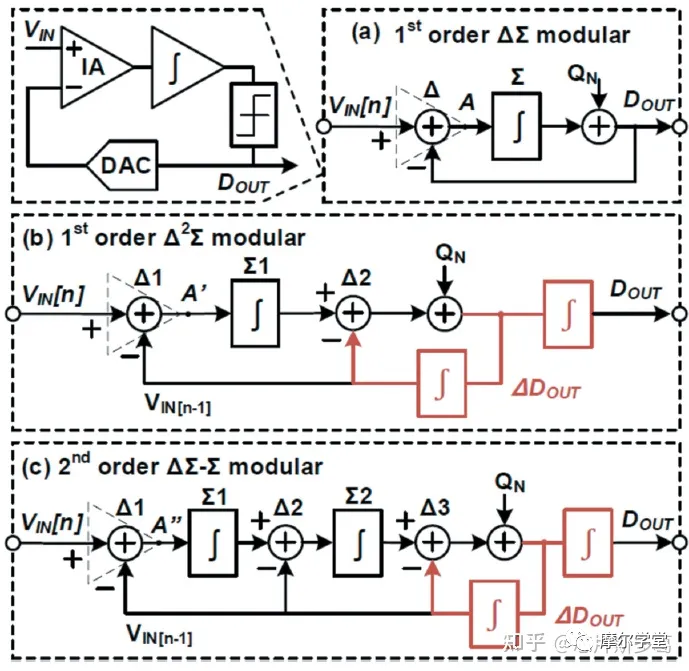

模块融合也体现在低功耗生物信号采集前端上,通过一个高动态范围、低噪声的 delta-sigma ADC,突破传统 amplifier + ADC 的固有架构,实现低功耗、小面积、高精度的生物信号采集。代表性参考论文包括 JSSC 2017, JSSC 2021 等

以 delta-sigma ADC 为基础的 direct A/D conversion © Liu et al., 2021 IEEE Sensors Journal

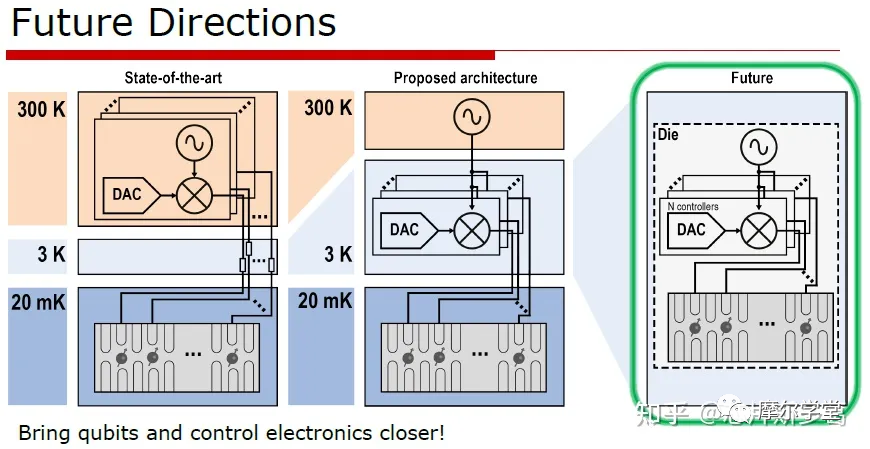

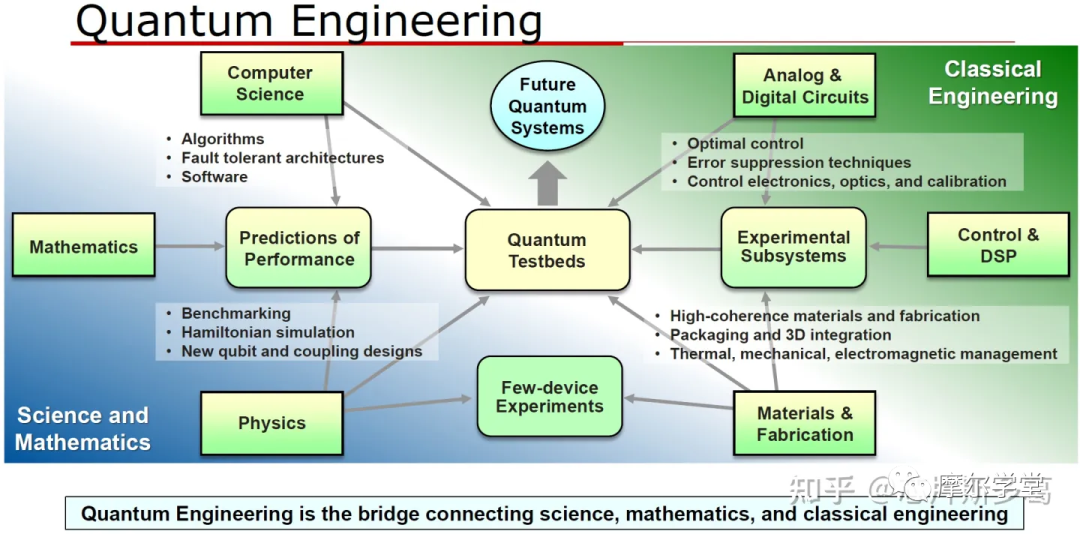

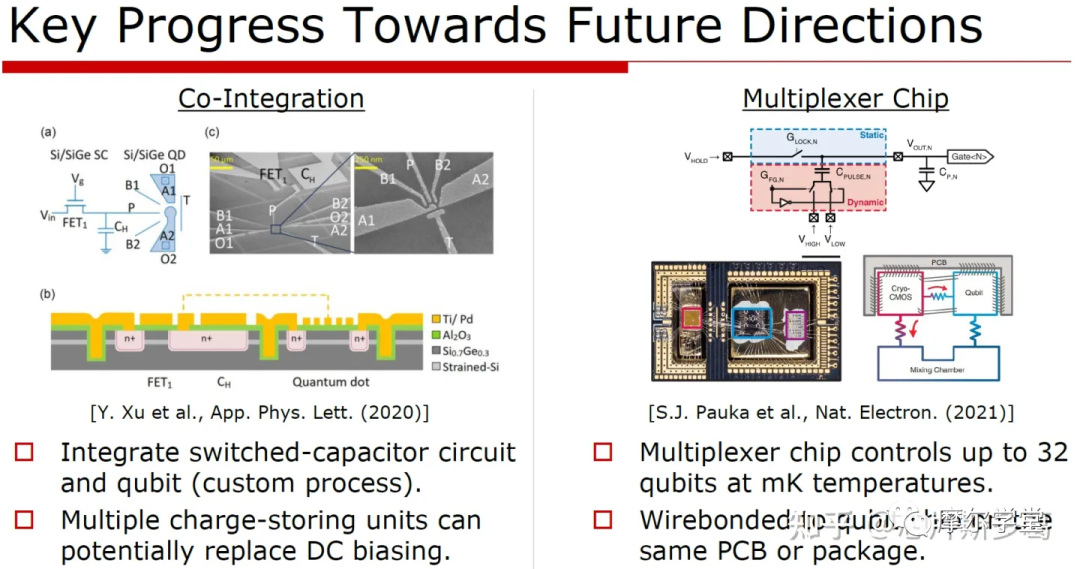

面向量子计算的模拟信号链处理芯片同样体现出模块融合的趋势,具体表现为Bring qubits and control electronics closer、将开关电容电路和 qubit 集成、将模拟信号链处理芯片和 qubit 芯片在 PCB 上封装到一起等。

量子计算芯片中的模块融合 © 2023 ISSCC

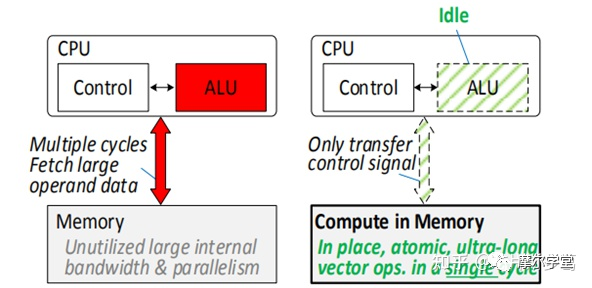

存内计算是模块融合+功能融合的最佳体现,每年 ISSCC 上发表的论文数量持续取得突破。存内计算通过将传统冯诺依曼架构中计算、存储分离的独立模块融合一体,减少计算过程中数据搬运所带来的功耗和时间开销,达成低功耗的高性能运算。

在 ISSCC 2023 全部34个session中,有2个session (S7, S16) 是以存内计算为单一主题,而且都是long session。此外,以存内计算为主题的论文还出现在 session 29(3篇)和session 33 (2篇)。因此,ISSCC 2023 至少有21篇存内计算相关的论文,论文数量已经超过了有些传统技术分类subcommittee track的论文数量。有关存内计算论文趋势的具体分析,可以参考矽说大佬的深度分析:ISSCC 2023 前瞻 —— 存算一体是大势所趋还是审美疲劳?

存内计算:存储计算模块融合 (图源网络)

芯片融合层面,主要体现为 Chiplet 和先进封装技术。这一点苏妈在今年的 Plenary talk 中也有重点提及:It is increasingly attractive to use modular chiplet architectures where the most advanced nodes are only used for the most compute-heavy IP which get the most gains from using the latest technology, and less advanced nodes are used for the IO and other functions that do not benefit as much from the most-advanced node. To continue advancing chiplet architectures over the next decade, innovation around the die-to-die interconnect is critical. 通过 Chiplet,实现突破算力和功能极限的 integrated-chips.

3、 器件、电路、系统跨层级联合创新

ISSCC 2023 首次新增一个paper session: Innovations from Outside the (ISSCC) Box,涵盖论文主题打破了此前 ISSCC 限定在固态电路级别的传统,包括生物电子、分子编程器、2D材料、光量子等。

新增Session 27: Innovations from Outside the (ISSCC) Box

虽然芯片新产品层出不穷,但摩尔定律放缓已成大趋势。在此背景下,单一芯片级别的创新,可能更多是工程调优,而不是颠覆性的新原理、新技术、新架构。业界人多资源广,适合工程调优,不断推出新产品以满足市场需求。相比而言,学界大多是博士生一人做一款芯片,工程投入远不如大公司一个团队。因此,这就造成了芯片领域学界业界脱节严重、学界脱实向虚等问题。

本次 ISSCC 的组委会,可能是意识到这个问题现象越发严重,因此尝试推出一个 outside ISSCC box new session,打破人们对于 ISSCC 论文风格的固有认知。关于这一点,ISSCC 2023 International Technical Program Chair在会议论文集 Foreword 中有提到:ISSCC is, despite of its age, looking to the future, seeking innovative designs more than ever. This goes hand in hand with performance advances of state of the art. The conference emphasizes this with two highlighted sessions of invited papers, one with out-of-the-box ideas and one with chip releases from industry.

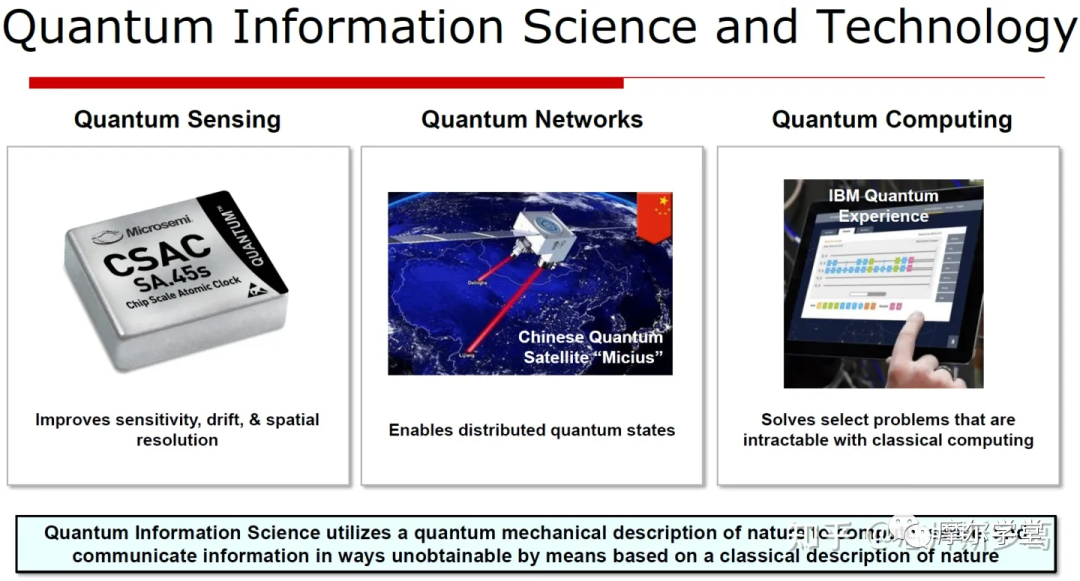

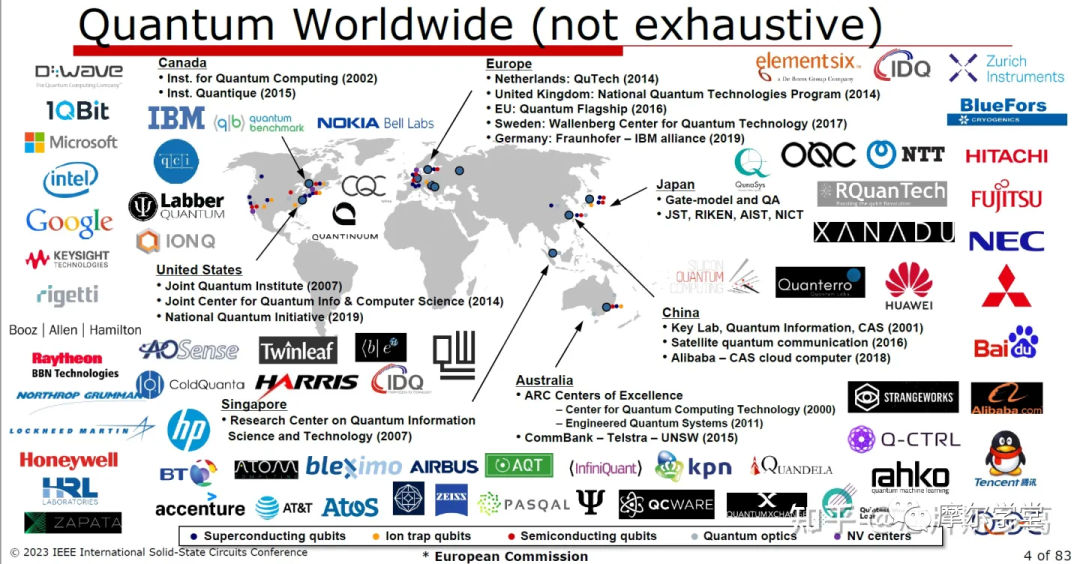

4、量子计算芯片重回热点

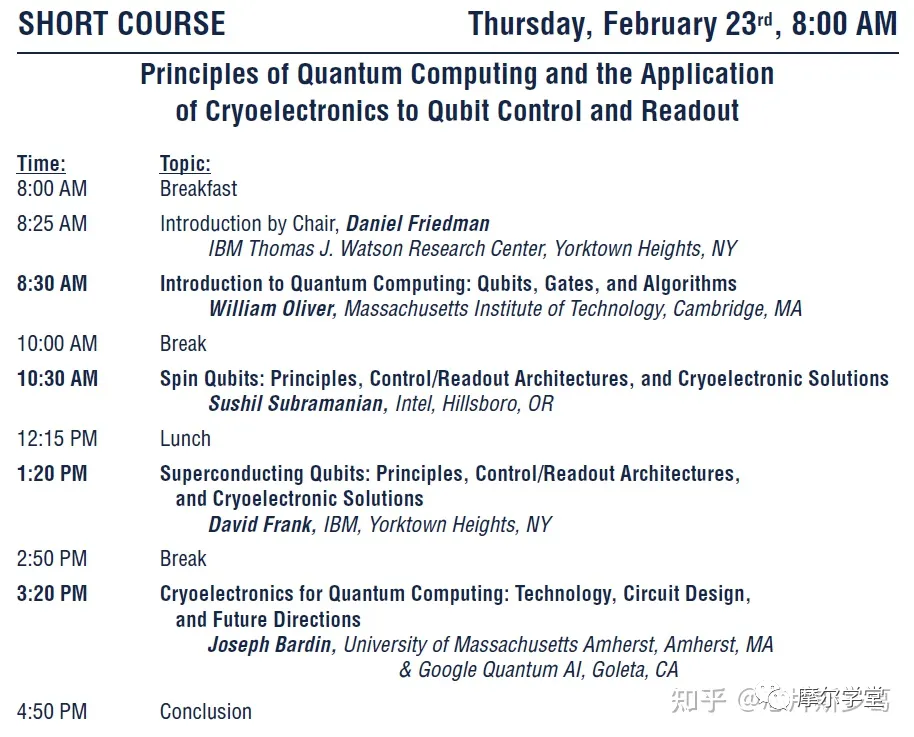

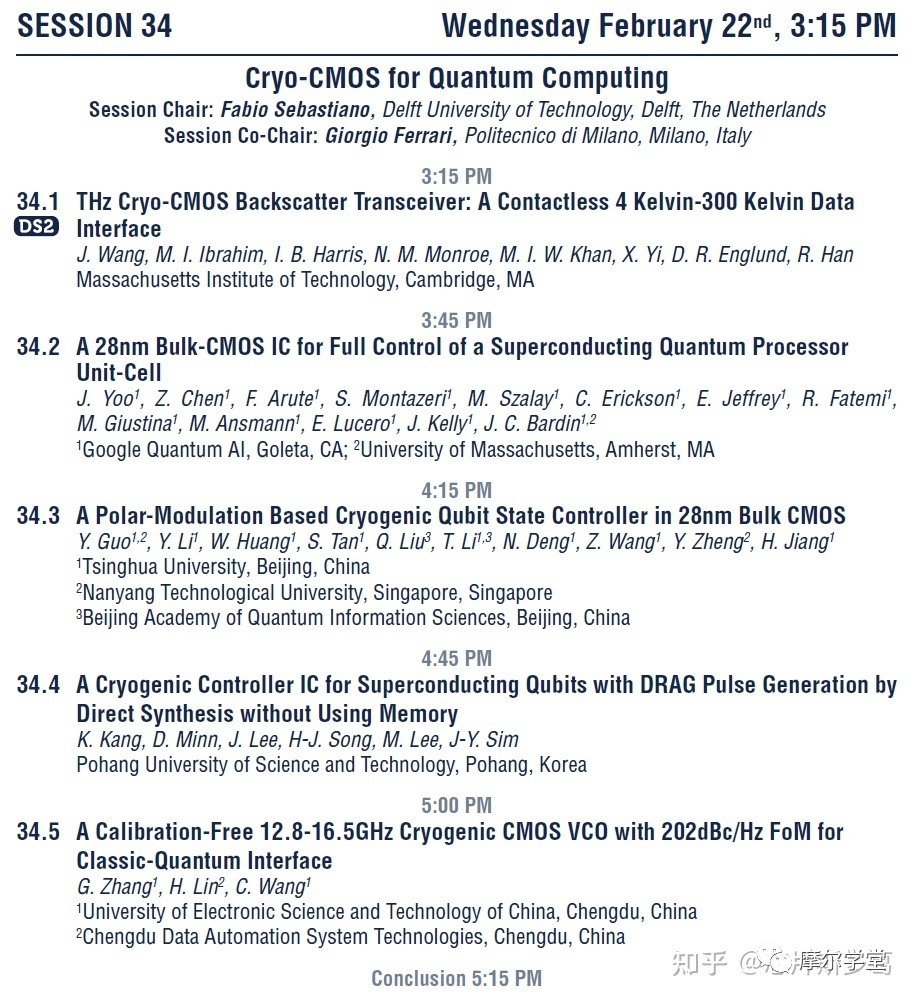

量子计算是今年 ISSCC short course的主题,同时,paper session相比2022年也新增一个单独的量子计算session 34:Cryo-CMOS for Quantum Computing,足以见得本次组委会对于量子计算的重视。

Short course: Principles of Quantum Computing and the Application of Cryoelectronics to Qubit Control and Readout

Session34: Cryo-CMOS for Quantum Computing

在ISSCC 2020 & 2021上,量子计算都有单独的regular paper session。但是,在去年的 ISSCC 2022上,量子计算有一个invited paper session: Highlighted Chip Releases: Systems and Quantum Computing,并没有regular paper session. 今年量子计算内容大幅增加,可能预示着量子芯片正在蓄势待发,会不会像之前的存内计算一样掀起一场 paper 革命呢?让我们拭目以待。

1、Innovation For the Next Decade of Compute Efficiency, Lisa Su, Chair and Chief Executive Officer, AMD

今年第一个 Plenary talk 来自芯片界传奇级人物、AMD 掌门人--苏妈 Lisa Su,对于未来十年芯片算力提升之路给出了高屋建瓴、细致入微的分析。

图源网络

下面分享报告的一些关键要点。

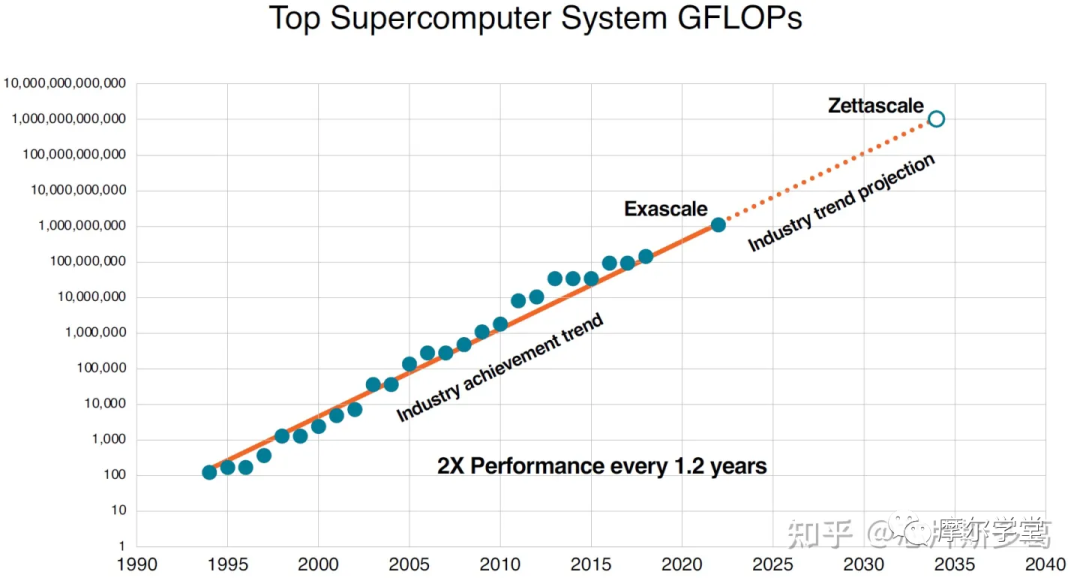

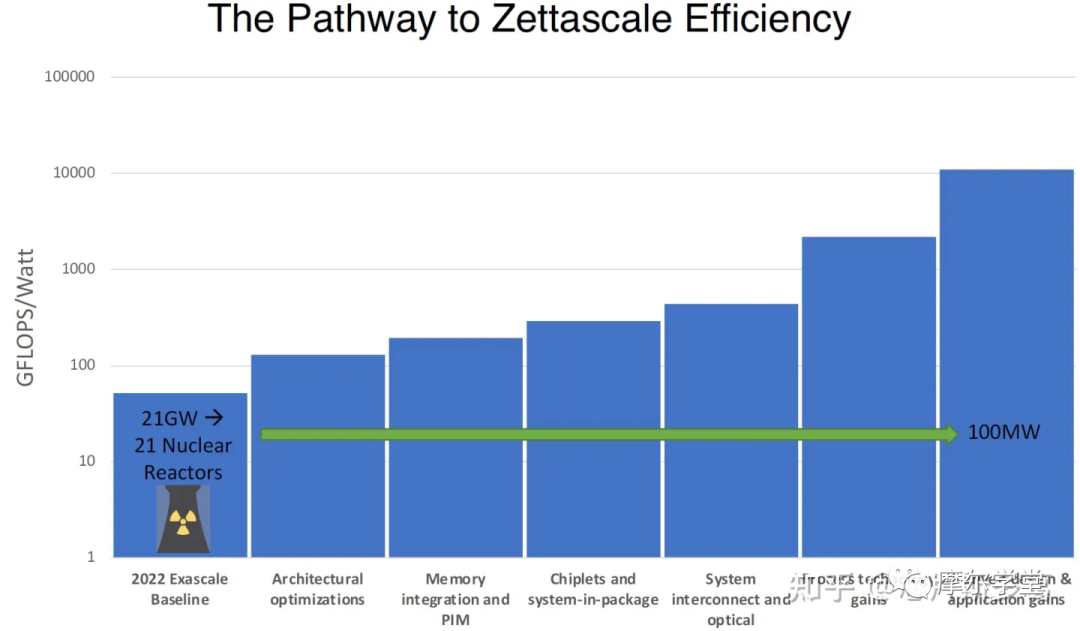

Efficiency gains must outstrip those of the last decade in order for a zettascalecapable system to fit within a reasonable power level. © 2023 ISSCC

Short courses

面向电路小白,提供了特定主题的深入分析和前沿技术最新动向。Short course包括由行业领先的专家以类似课堂的形式进行的四次讲座。今年的Short course主题是量子计算:Principles of Quantum Computing and the Application of Cryoelectronics to Qubit Control and Readout。具体包括以下四个课程:

4.1 Introduction to Quantum Computing: Qubits, Gates, and Algorithms, William Oliver, Massachusetts Institute of Technology, Cambridge, MA

SC1: Introduction to Quantum Computing © 2023 ISSCC

SC1: Introduction to Quantum Computing © 2023 ISSCC

SC1: Introduction to Quantum Computing © 2023 ISSCC

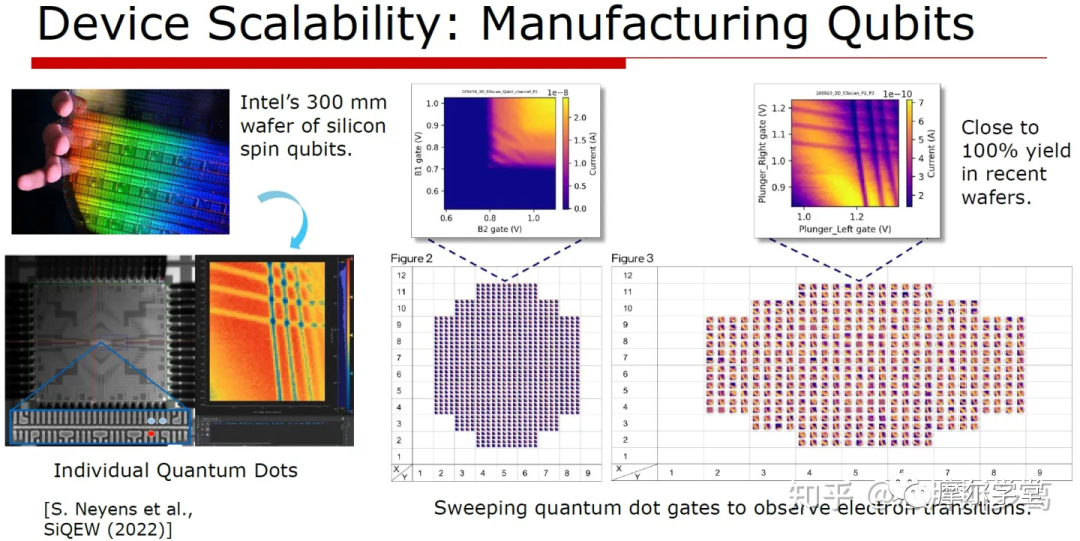

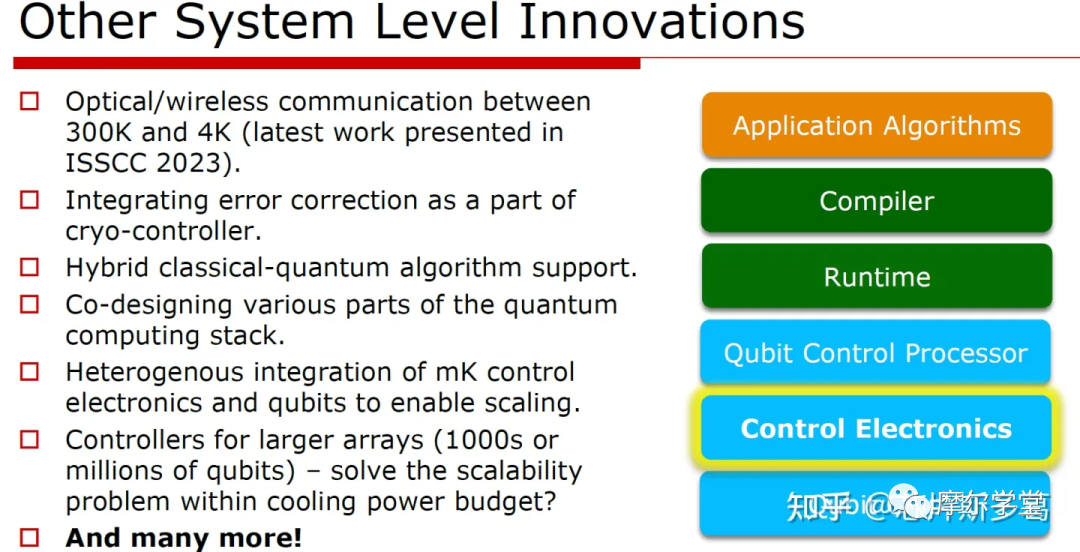

4.2 Spin Qubits: Principles, Control/Readout Architectures, and Cryoelectronic Solutions, Sushil Subramanian, Intel, Hillsboro, OR

SC2: Spin Qubits © 2023 ISSCC

SC2: Spin Qubits © 2023 ISSCC

SC2: Spin Qubits © 2023 ISSCC

SC2: Spin Qubits © 2023 ISSCC

4.3 Superconducting Qubits: Principles, Control/Readout Architectures, and Cryoelectronic Solutions, David Frank, IBM, Yorktown Heights, NY

SC3: Superconducting qubits © 2023 ISSCC

SC3: Superconducting qubits © 2023 ISSCC

SC3: Superconducting qubits © 2023 ISSCC

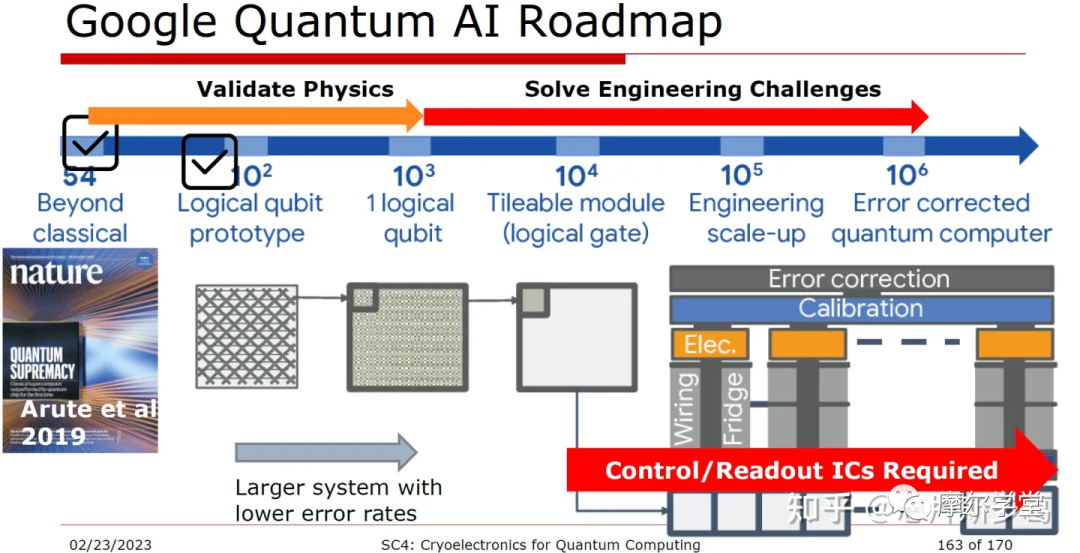

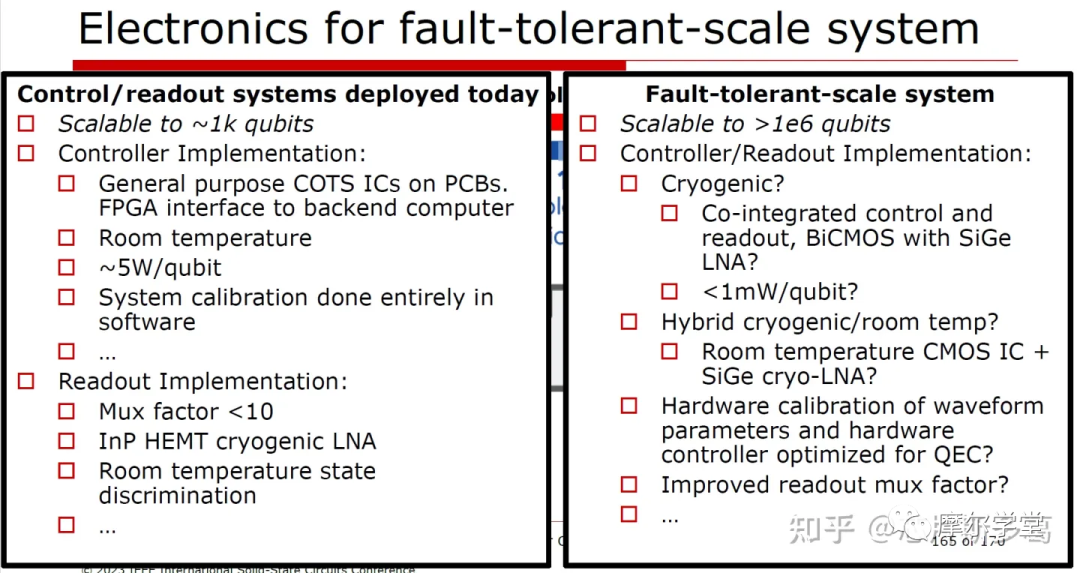

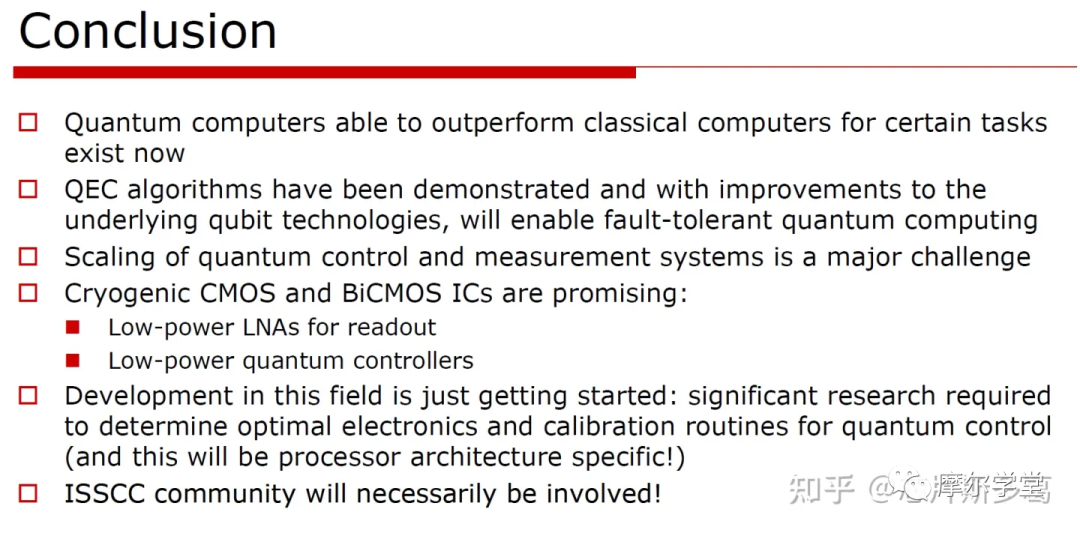

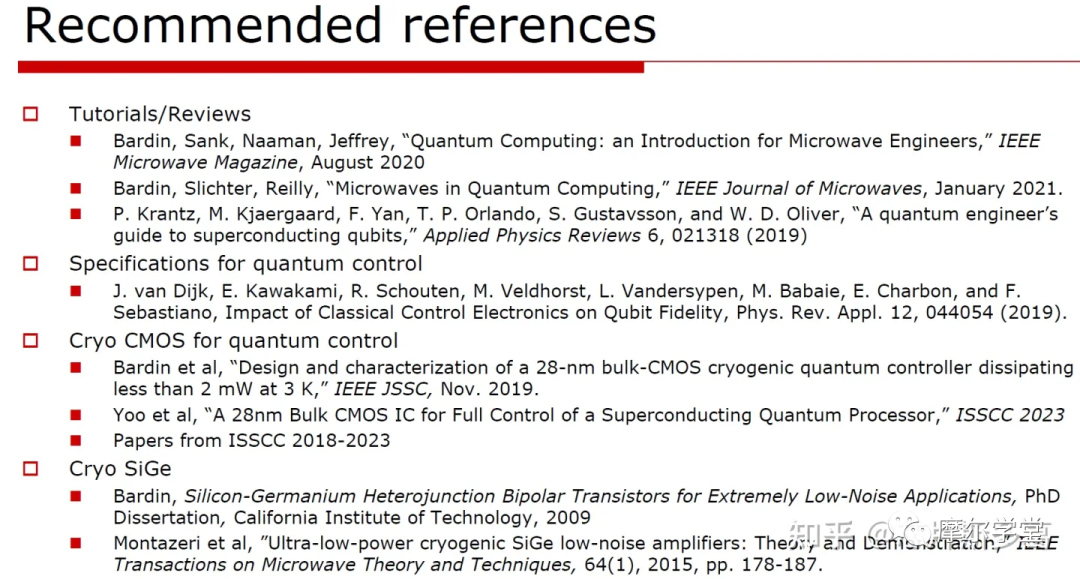

4.4 Cryoelectronics for Quantum Computing: Technology, Circuit Design, and Future Directions, Joseph Bardin, University of Massachusetts Amherst, MA & Google Quantum AI, Goleta, CA

SC4: Cryoelectronics for Quantum Computing © 2023 ISSCC

SC4: Cryoelectronics for Quantum Computing © 2023 ISSCC

SC4: Cryoelectronics for Quantum Computing © 2023 ISSCC

SC4: Cryoelectronics for Quantum Computing © 2023 ISSCC

SC4: Cryoelectronics for Quantum Computing © 2023 ISSCC

Tutorials

今年ISSCC共有12个Tutorials,涉及12个不同的主题,每个主题介绍一个特定技术领域的基本概念和工作原理。Tutorials面向希望探索和了解一个新课题的非专家、研究生和执业工程师。

今年Tutorials的主题包括:

Fundamentals of Frequency References

Bridging RF and Power: An Introduction to Envelope Tracking Systems and Building Blocks

Fundamentals of Data Converters

Automotive System Design

All-Digital PLLs: From Fundamental Concepts to Future Trends

Solid-State CMOS LiDAR Sensors

Fundamentals of Ultra-low Voltage Embedded M emory Design

Role of Current-Mode Passive Mixers and N-Path Filters in RF Receivers

Physical-Layer Security for Latency- and Energy-Constrained Integrated Systems

The Art of mm-Wave Layout

Digital Equalization and Timing Recovery Techniques for ADC-DSP Based Highspeed Links

Extending Processor Cores for Machine Learning

Tutorials的内容一般比较基础,相关资料在网上比较容易找到,这里不做过多展开。值得注意的是,今年有一个主题讲毫米波电路版图技巧,题目是The Art of mm-Wave Design & Layout,slides封面图非常漂亮,科技与美学的极致体现!

The Art of mm-Wave Design & Layout © 2023 ISSCC

本文转自:芯片斯多葛@知乎,整理所得,谢谢!

今天小编带来了:ISSCC2023套餐,里面有文章、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台