解决外国“卡脖子”问题是当前信创的核心工作。CPU巨头大多集中在海外,对行业起着决定性的作用。国产高性能CPU需要全方位提升从硬件设计到生态建设的能力,一方面对国外高端CPU的技术持续进行吸收和自主创新,另一方面推进相应的生态建设和国产自主可控产品替代。关于CPU架构介绍的技术贴和书籍劈天覆盖地,但大多都不能形成系统,学习者往往只能识其皮毛,很难深入架构系统学习。

针对此现状,笔者看到一本应该是目前中文出版物中最全面、最贴近国内能够接触到的最先进技术、系统性讲解高性能CPU核微架构设计的书:《高性能超标量CPU:微架构剖析与设计》。写作团队具有丰富的高性能CPU微架构设计经验,交付产品涵盖ARM、x86、RISC-V等主流架构。即使到了2023年,想要系统清晰地学习5年前、10年前,甚至20年前的CPU微架构设计,公开的书面材料仍是有限且碎片化的。现有的讲解CPU设计的书籍以经典教材为主,教材内容与工业界实际在做的事情之前存在着较大的差距,缺少从行业角度对高性能CPU设计进行全面深入描述的内容。这是高校学生和初窥门径的从业者一定会面临的情况,所以非常需要一本能够填补这一空白的书籍。

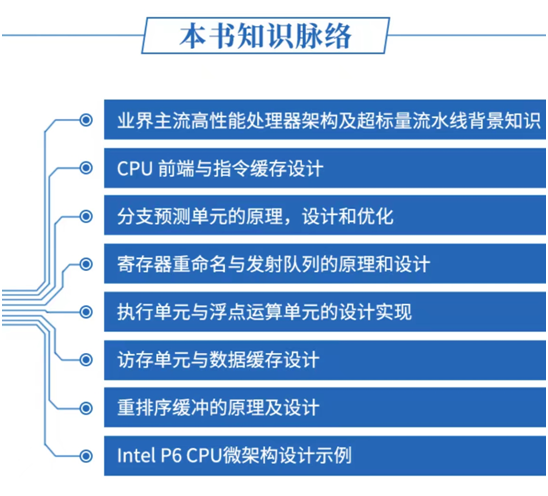

不可否认的是,高性能CPU设计这一领域是相对“闭源”的,最好的学习方法自然是直接阅读RTL代码和架构手册,但由于各种原因,国内能够拥有实操经验的人员相对而言仍是少数。加上知识产权限制与业务领域和水平的不同,系统性地思考和真正形成具有流畅内在逻辑的书面文字并非看上去那么轻松。本书在规避知识产权限制的基础上,尽力为读者展现当下先进设计的样子以及相应的设计方法,希望读者阅读后能够举一反三,消化吸收为属于自己的方法学,这样后续阅读相关文献时能够第一时间抓住要点掌握精髓,最终能够独立完成微架构的探索、迭代和重构。本书主要是帮助读者理解高性能CPU核微架构以及如何设计和优化。在许多情况下,一些实际产品中的微架构将不会详细描述,以免在商业知识产权方面带来不必要的麻烦。但是,万变不离其宗,核心原理和思维方法能够帮助读者去设计本书中描述的各个单元。微架构实现方法并不存在绝对和唯一的答案。一个好的设计一定是经得起一定时间段内竞品和基准测试的考验的,并且应该是可扩展和易于迭代的,这需要在开始设计时在性能、功耗、面积和验证复杂性方面做好平衡。本书内容以CPU微架构指令运行生命周期为脉络,按硬件流水线逐级展开。具体内容分为10章,第1章介绍业界主流高性能处理器架构及超标量流水线背景知识;第2到9 章对按顺序分别展开讲解 CPU各个功能单元的微架构设计;第10章对经典的 x86架构CPU微架构Intel P6的设计进行了详细剖析,便于读者通过设计实例来印证前9章的相关内容。本书是站在工程师的角度对设计人员需要了解的内容进行的阐释,并针对当前最新的技术趋势对实现方案进行了取舍后呈现给读者。这种做法有利有弊,帮助一部分读者理清了一些问题,但也有可能忽略了另一部分读者对于全部方案探索的欲望。不过整体来说,希望能够带给读者想要了解的信息以及背后的逻辑。另外,本书淡化了指令集架构对微架构的影响,但读者应该会看到实际内容较多篇幅会贴近ARM,还有一部分贴近x86,这是由于写作团队的业务背景决定的。欢迎读者交流和批评指正。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

购买链接:

扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取“购买链接”。