▲ 更多精彩内容 请点击上方蓝字关注我们吧!

自 1958 年 IBM 设计出首个管状“开关模式电源”以来,打造无传导和开关损耗的理想开关一直是电源转换器设计者的梦想。如今,各项开关技术的通态损耗都有了明显降低;采用最新的宽带隙半导体的产品,在 750V 额定电压下的电阻已能达到小于 6 毫欧的水平。目前这项技术还未达到其物理极限,预计在不久的将来,该阻值还会进一步降低。

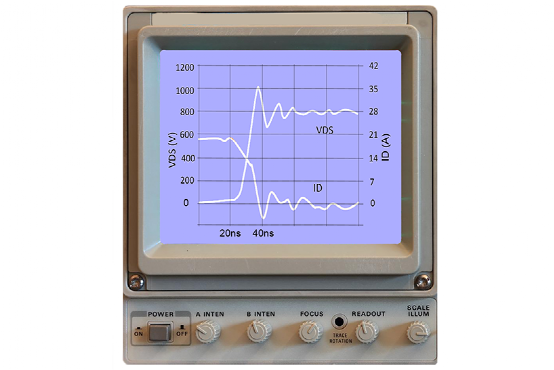

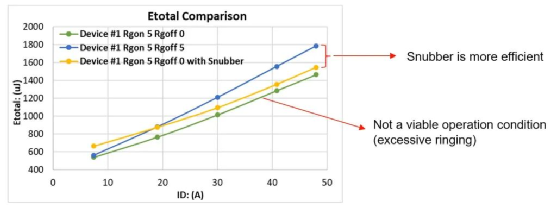

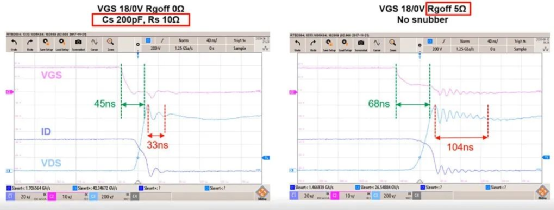

在当今的高性能功率设计中,边缘速率 (V/ns) 有所提高,降低了开关损耗,可实现更高的频率、更小的磁性元件和更高的功率密度。然而,这些快速边缘速率增加了造成电磁干扰设计相关问题的可能性,这些问题会与电路寄生效应发生相互作用,导致不必要的振荡和电压尖峰。借助良好的设计实践,这些问题可以使用小缓冲电路解决。那么,这个问题有多严重呢?如果我们看到速率达到 3000A/µs,也就是典型的碳化硅开关值,那么根据熟悉的 E=-Ldi/dt 公式,仅 100nH 连接电感或漏电电感就会产生 300V 尖峰电压。100nH 仅仅是几英寸 PCB 迹线的电感或变压器漏电电感的真实值,所以这就是通常会看到的情况,而且需要一个好的示波器才能看到整个电压瞬态。不过该开关在看到瞬态方面没有问题,如果超过额定雪崩电压能量,会立即停止运转。在任何电路电容下,该尖峰都会振铃,从而让测量的电磁干扰释放达到峰值。一个补救措施是尝试降低电路电感,但这通常不是一个实用的选择。此外,还可以大幅降低该开关的电压,代价是影响成本和导通电阻,也可以使用串联栅极电阻放缓边缘速率。这个仪器并不敏感,它延迟了波形,通过限制占空比限制了高频运行,还提高了开关损耗,同时几乎不影响振铃。振铃可通过缓冲网络实现,支持快速开关,但会减少尖峰和抑制振铃。在大电容器和大功率电阻时代,这看起来像是一个“暴力破解”方法,与 IGBT 等一起使用,试图减少大“尾”电流效应。然而,对于 SiC FET 等开关而言,这是一个非常高效的解决方案。在这种情况下,主要使用缓冲电路抑制振铃,同时限制峰值电压。因为器件电容非常低,振铃频率高,所以只需要一个非常小的缓冲电路电容,通常为 200pF 左右,并使用几欧姆的串联电阻。与预期一样,电阻会耗散部分功率,但是它实际上会通过限制硬开关和软开关应用中的电压/电流重叠来降低关闭损耗。打开时,缓冲电路会耗散额外的功率,因此需要考虑总损耗 E(ON) + E(OFF) 才能公正地评估其优势。将一些测量值代入E(TOTAL) 以体现 40 毫欧 SiC FET 在 40kHz 下的运行状况,考虑了三种情况:无缓冲电路,RG(ON) 和 RG(OFF) 为 5 欧姆(蓝线);200pF/10 欧姆缓冲电路,RG(ON) = 5 欧姆,RG(OFF) = 0 欧姆(黄线);无缓冲电路,RG(ON) = 5 欧姆,RG(OFF) = 0 欧姆(绿线)。这会得出最低的 E(TOTAL);但是振铃过高,因而不可行。在高电流下,使用缓冲电路的好处很明显,与仅调整栅极电阻相比,在 40A 下的耗散降低约 10.9W。在轻负载下,缓冲电路的整体损耗较高,但是在这些条件下,系统耗散很低。综上所述,缓冲电路是一个不错的解决方案,但切实可行吗?点击阅读原文,查看易于实施的缓冲电路。而且SIC FET的导电损耗和动态损耗都低,接近理想开关,而且只需增加一个小缓冲电路,就可以发挥全部潜力,且不会造成过高的电磁干扰或电压应力问题。干货|功率MOSFET零电压软开关ZVS的基础认识在公众号内回复您想搜索的任意内容,如问题关键字、技术名词、bug代码等,就能轻松获得与之相关的专业技术内容反馈。快去试试吧!如果您想经常看到我们的文章,可以进入我们的主页,点击屏幕右上角“三个小点”,点击“设为星标”。