▼关注公众号:硬件微讲堂▼

大家好,我是硬件微讲堂。这是我的第65篇原创文章。欢迎关注公众号,通过问题面试后加入免费技术交流群,抱团取暖,共同进步!

关于MOS管的米勒效应,前面已经发了3篇:

MOS管的米勒效应(1)

MOS管的米勒效应(2)

MOS管的米勒效应(3)--如何减小米勒平台

其中(1)和(3)收录在“器件篇”付费专辑中。尤其第3篇通过仿真数据来验证如何减少米勒平台,总结的3种策略切实有效。今天我们继续米勒效应的第4篇。

一道问题

照例,先抛出来一道问题:如果MOS管处于米勒平台的区间内,MOS管工作在哪个区?

A:恒流区;

B:可变变阻区;

C:部分在恒流区,部分在可变电阻区;

D:截止区;

题不大,但却是真正考验基本功。要回答这个问题,需要从两方面入手:

①搞清楚MOS管三个工作区的工作条件;

②搞清楚MOS管米勒平台的变化历程。

MOS管3种工作状态

MOS管的3种工作状态:截止区、恒流区(饱和区)、可变电阻区,这个想必大家都知道。但光知道这个还不太够,还需要清楚进入相应工作区的充分条件。

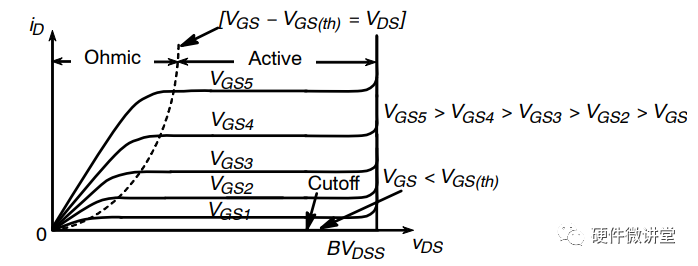

如上图所示,Ohmic Region即为可变电阻区,Active Region即为饱和区,也叫恒流区,Cut-off Region即为截止区。由于MOS管为压控型器件,只需要控制栅-源极电压Vgs电压,即可控制MOS管的导通。

当Vgs

当Vgs>Vth且Vds

当Vgs>Vth且Vds>Vgs-Vth时,MOS管处于恒流区(饱和区);

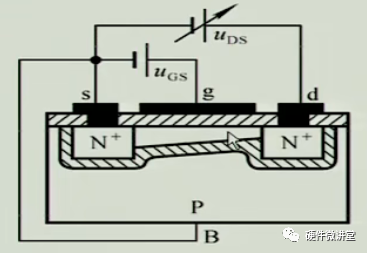

当然上面的条件,我想很多同学都知道。但是我想让同学们理解里面的含义,而不是单纯地记忆公式。比如,可变电阻区的Vds

在Vgs>Vth的前置条件下,保证源极S侧的导电沟道存在。再在漏极-源极间加入一个电压Vds,要保证漏极D侧的导电沟道也存在,就必须使得Vgd>Vth。这样Vgs和Vgd都大于Vth,漏极S和源极D之间的导电沟道才会一直存在。

而Vgd等于Vgs+Vsd,可变换为Vgs-Vds。Vgd>Vth,即Vgs-Vds>Vth,则有:Vds

恒流区的Vds>Vgs-Vth就不展开解释,具体可以参看《Rdson对应MOS管的哪个工作区?》,里面的解析比较详细。

MOS管米勒平台变化历程

要搞清楚MOS管米勒平台的变化历程,不妨我们用TINA-TI做下仿真,结合仿真数据来分析变化过程。

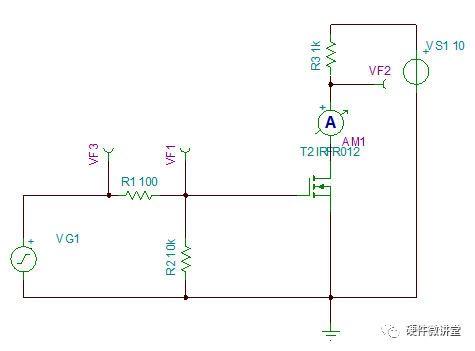

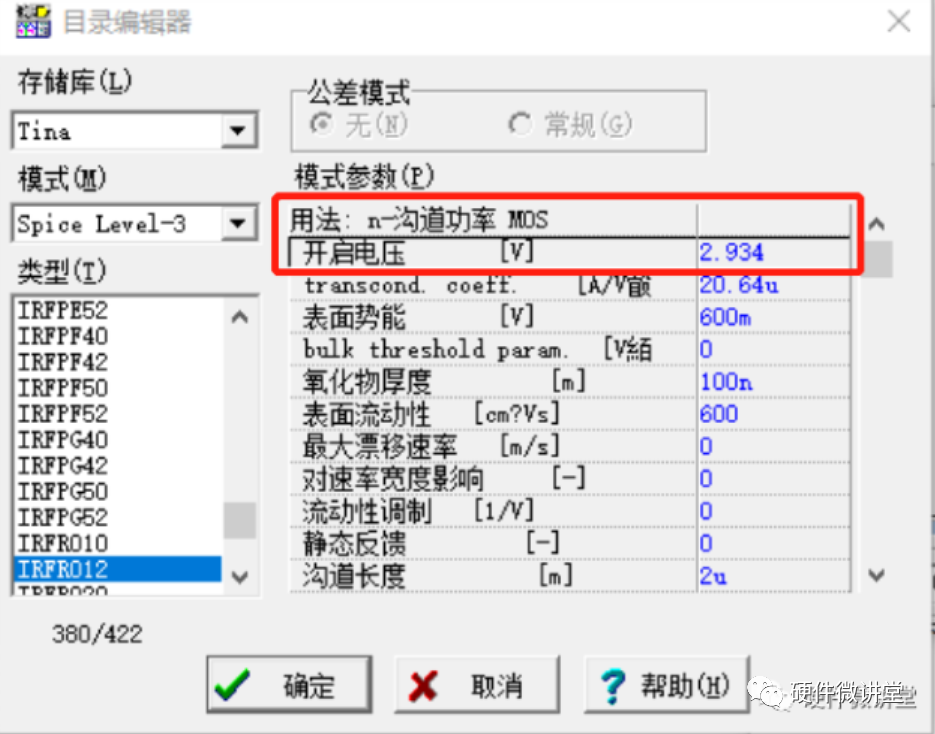

①搭建MOS管的仿真电路,如下图所示。还需要检测栅源电压Vgs、漏源电压Vds和漏极电流Id。

VF1,监测Vgs的电压波形;

VF2,监测Vds的电压波形;

VF3,监测驱动源VG1的电压波形;

AM1,监测Id的电流波形。

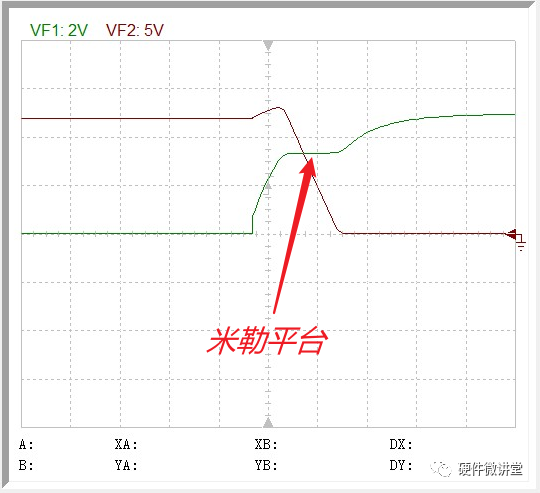

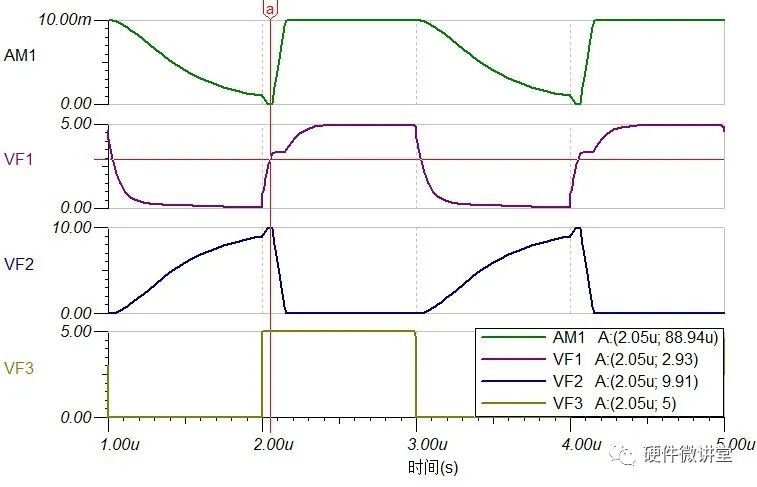

②跑一下“瞬时分析”,看下整体的波形,如下图所示。

如上图所示,a点标记的时间位置为2.05us。可以明显看出:

①在a点前,漏极无电流Id;

②在a点后,漏极开始有电流Id(如AM1所示),即MOS管开始导通;

该MOS管的开启电压Vth为2.93V,即为a点。

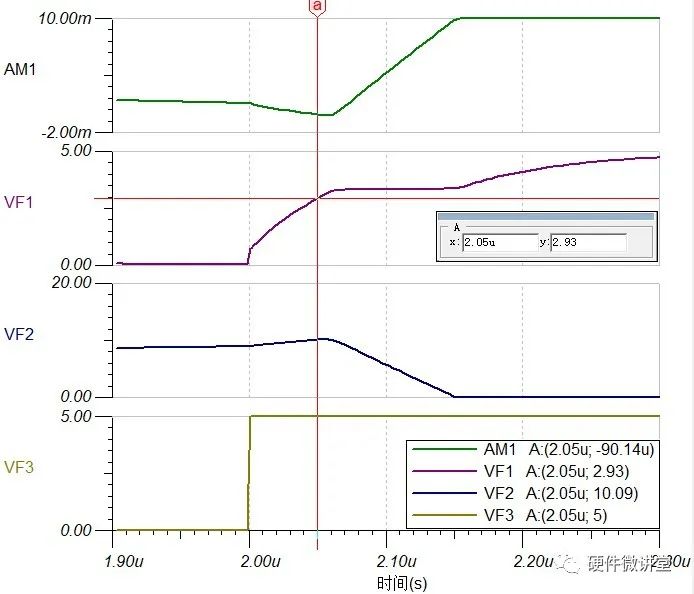

为方便进一步观察,将仿真结果进一步放大,如下图所示:

不知道屏幕前的你,看完上图片有没有什么疑惑。反正我是有疑问!!!

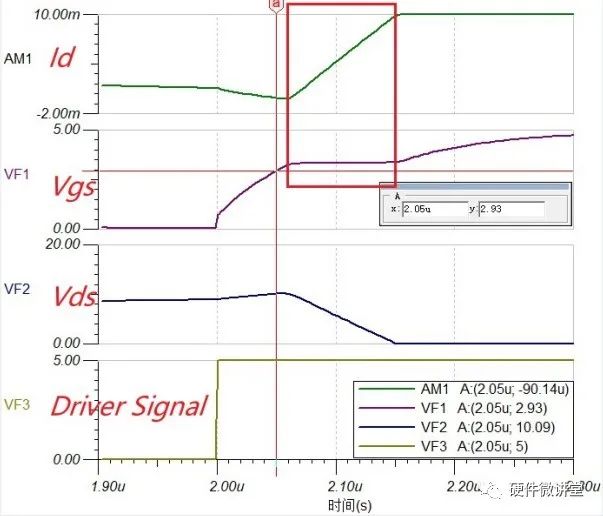

如上图红框所示,Id在米勒平台期间仍在上升。在米勒平台结束时,漏极电流才达到最大值。这和我之前了解到电流变化趋势不同。

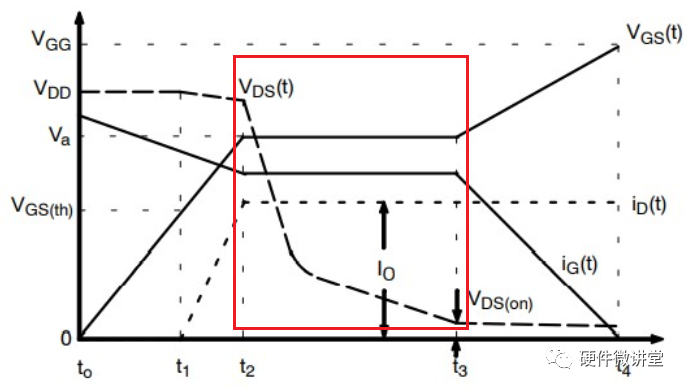

上图,相信很多同学在很多文章中都看过。或者在网上搜一下“米勒效应”,

随便点开几篇文章都有这幅图片。在这幅图中,可以明显看出:漏极电流Id是在t2时刻达到最大值,在米勒平台期间(t2-t3时间段)Id基本保持不变。这幅图和仿真出来的结果相差很大。

期初,有怀疑这幅图的正确性。几经努力,找到了这幅图片的出处,源自安森美(Onsemi)的技术文档《AN-9010_MOSFET Basic》(文末可以免费获取)。鉴于是大厂的技术文档,暂时打消了我对其正确性的怀疑。

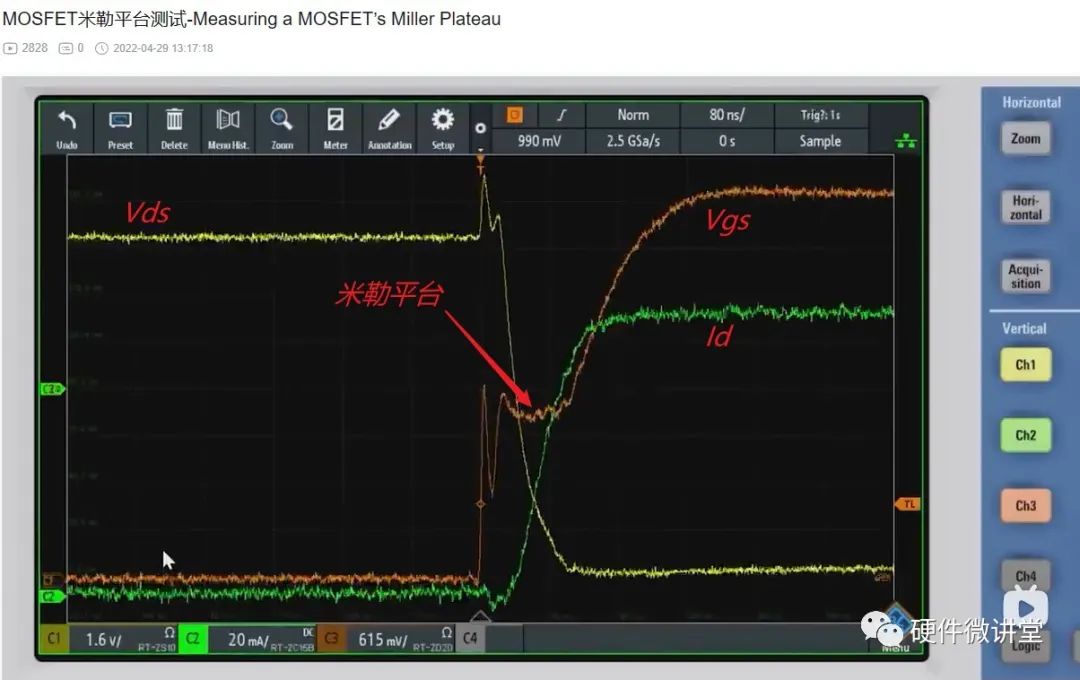

再次去查询相关资料,在B站上看到一个视频,是老外在讲解米勒效应,展现出来的实测波形,绿色的Id确实是在橙色的Vgs米勒平台期间上升,基本在米勒平台结束后Id到达最大值,如下截图所示。

仿真波形和实测波形可以呼应,说明仿真数据没有错。

这样的话,仿真没有错,Onsemi的图也没有问题,但是波形趋势相差很大,那问题出在哪里呢?是谁的问题呢?

我暂时没有想通,期待屏幕前的大神能帮忙拨开迷雾,指点迷津。

由于本文在仿真中遇到了暂时解释不通的问题,所以在文章开头提出的问题,暂时没有得到验证解决。

安森美(Onsemi)的《AN-9010_MOSFET Basic》(英文原版),在公众号回复:MOS,即可获取该文档。

关注“硬件微讲堂”,硬件路上不慌张!