本文介绍了自制铜浆的组成和特点,探讨了铜浆在多层陶瓷封装外壳制备技术中的适用性。通过对铜浆微观形貌观察,方阻、剪切强度的测试,分析并讨论了玻璃相添加量、烧结温度、排胶温度、排胶时间对于铜浆性能的影响。

研究发现,当烧结温度为850℃,玻璃相添加量为7wt.%时,铜浆表现出良好的导电性和较高的剪切强度,方阻为2.5mΩ/,剪切强度为45.7MPa。当排胶温度达到650℃,适当延长排胶时间,降低升温速率有利于促进埋层铜浆的致密化烧结,减少孔洞,从而改善多层陶瓷封装外壳的表面平整度。

01

引言

随着我国微电子产业水平的不断提高,电子封装技术向着高频高速、高可靠性、大尺寸、高度集成化方向发展,电子封装导体材料在新一代封装材料体系中发挥着越来越重要的作用。传统的W、Mo导体材料主要应用于HTCC多层陶瓷外壳加工工艺,而内部线条所采用的丝网印刷工艺由于其本身工艺特性(丝网目数、金属浆料及印刷加工工艺性等)以及W、Mo导体材料自身性能(导电性差,电阻率分别为5.5μΩ·cm和5.2μΩ·cm)的限制,很难满足更高频率和更高传输速率的陶瓷外壳的封装要求。Au、Ag方阻较低,目前金浆、银浆已成熟应用于LTCC技术,但由于Au、Ag高昂的成本以及激烈的竞争带来的LTCC类封装外壳价格持续走低,导致LTCC类封装外壳利润越来越低,极大的限制了Au、Ag在陶瓷封装领域的应用及推广。因此选择一种具有良好导电性的合适导体材料对于突破上述限制,更好的实现微电子器件高频、高速的传输要求至关重要。

Cu金属具有很多优良的性能,Cu具有比贵金属Au更为优良的高频特性和导电性,同时Cu也没有像Ag那样的迁移缺陷,而且Cu比Ag的熔点要高,可以使样品烧结范围变得更加宽广,除此之外,Cu还拥有优良的可焊性和较低的成本[1,2]。已经被广泛用于电子工业、导电涂料、催化剂等多个领域,在微电子封装领域也有着较强的应用价值[3]。上世纪90年代,以日本为主的发达国家研制出的铜浆,成功实现了在MLCC、LTCC元件领域的应用,显著降低了材料成本支出,大大提升了其市场竞争力。虽然国内已经有部分厂家开始研制铜导体浆料,华南理工大学吴松平[4]通过化学还原法制备了粒径达到400nm左右的超细铜粉,并进一步制备了可用于MLCC的无铅导电铜-镍膜,具有良好的粘附性和致密性;风华电子工程公司近年成功开发出适合BME-MLCC使用的端电极铜浆,但多层陶瓷封装外壳用铜导体浆料的国产化仍未得到解决,均被国外垄断。本文介绍了自制铜浆的组成及特点,通过不同玻璃相含量、烧结温度、排胶温度及排胶时间的调整,开展铜浆在多层陶瓷封装外壳制备技术中的适用性研究。

02

实验

2.1 导电铜浆的制备

2.1.1 铜浆玻璃相的制备

采用B2O3、SiO2、CaO、TiO2等分析纯试剂制备铜浆用玻璃相。将上述氧化物按一定比例称取后倒入氧化铝球磨罐进行滚磨,混合均匀后烘干,再把均匀的粉料放入电阻炉中加热至1300℃,保温30min,待原料成为液体时倒入蒸馏水中水淬,即可得到初始的玻璃料。随后将制得的玻璃料烘干后放入行星球磨机中进行球磨,玻璃粉D50粒径磨至1.2~1.6μm后,倒出进行烘干处理,研磨过筛,制得玻璃相备用。

2.1.2 铜浆的制备

将铜粉与预先制备的有机载体、玻璃相按一定比例搅拌混合后,用三辊研磨机研磨,待浆料细度≤5μm即可,制得铜浆备用。

2.2 样品的制备及表征

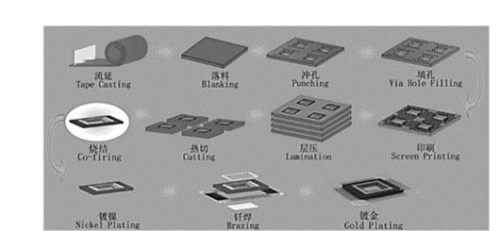

以上述制得的铜浆为导体材料,十三所自制陶瓷材料A为陶瓷基体,依托十三所多层陶瓷封装外壳加工工艺平台(如图1所示),经过冲孔、丝网印刷、印刷填孔、层压、热切、烧结、镀镍、镀金等工艺制备某型号陶瓷外壳(如图2所示)。

采用EVO-MA18扫面电镜(德国卡尔蔡司)对铜浆烧结后表面形貌、孔隙率进行观察分析。采用GOM-802型直流毫欧表(苏州德计仪器仪表)测试铜浆方阻。根据GJB7677-2012用DAGE4000剪切前度试验机测试铜浆焊盘剪切强度。

03

结果与讨论

3.1 不同烧结温度对铜浆性能的影响

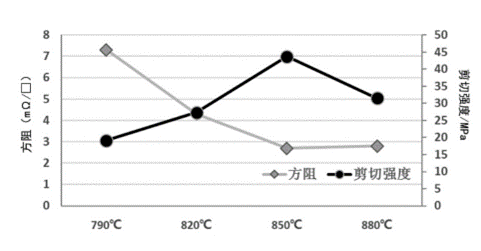

图3是玻璃相添加量为6wt.%的铜浆在790℃、820℃、850℃、880℃4个不同温度条件下烧结后方阻和剪切强度的测试结果。从图3可以看出烧结温度对铜浆的电性能和剪切强度都有重要影响。随着温度的升高,铜浆的方阻呈现先下降后平稳的趋势,当烧结温度为850~880°C时,方阻为2.7mΩ/☐左右;而铜浆剪切强度则呈现出现提高后下降的趋势,当烧结温度为850°C时,铜浆剪切强度最大,为43.7MPa。

图1 多层陶瓷封装外壳工艺流程图

图2 某FC-CLGA陶瓷封装外壳

图3 不同烧结温度条件下铜浆的方阻和剪切强度

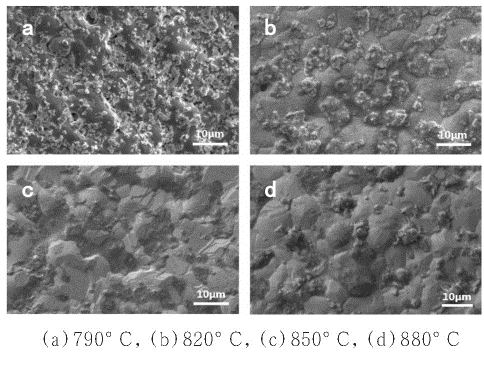

当烧结温度较低时,铜浆中所添加玻璃相未熔融或者部分熔融(如图4a、4b所示),不能有效的包裹铜颗粒,铜浆烧结过程中液相量较少,致密化烧结驱动力不足,形成部分孔隙,影响了铜浆的导电性。同时由于玻璃相未能有效的浸润铜浆和陶瓷基体,因此剪切强度较弱[5]。当温度达到850°C时,玻璃相全部熔融,大量的液相在铜粉周围形成网络,有助于铜粉均匀、致密化烧结,并充分浸陶瓷界面,此时铜浆的导电性和剪切强度均大幅度提高。随着烧结温度进一步升高,方阻变化不大,但剪切强度出现明显下降。一方面由于过高的烧结温度造成玻璃相粘度降低流失,铜粉向下沉积,界面玻璃相减少[6,7],另一方面,当烧结温度过高时玻璃相过分析晶(如图4d所示),玻璃相本身强度降低。

图4 不同烧结温度的铜浆SEM图

3.2 不同玻璃相添加量对铜浆性能的影响

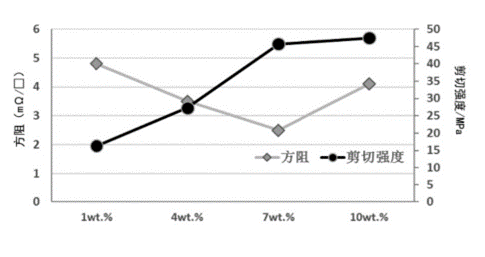

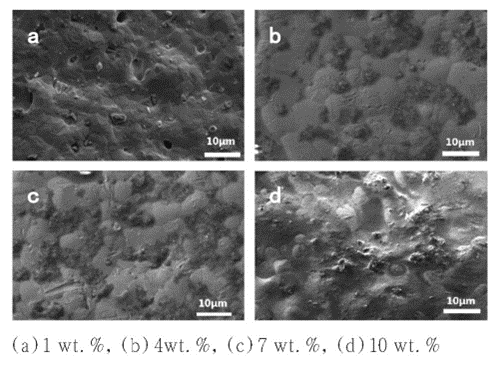

为了研究不同玻璃相添加量对铜浆性能的影响,分别配制玻璃相含量为1wt.%、4wt.%、7wt.%、10wt.%的4种不同浆料,并在氮气气氛、850°C条件下进行烧结,并对烧结后铜浆表面组织形貌、导电性、剪切强度进行分析。图5给出的是4种铜浆方阻和剪切强度的测试结果。从图可见,随着玻璃相添加量的增加,铜浆方阻呈现先减小再增加的趋势,当玻璃相添加量为7wt.%左右时方阻最低,为2.5mΩ/☐。当玻璃相含量小于7wt.%时,剪切强度则随着玻璃相添加量增加,显著提高。当玻璃相含量超过7wt.%时,剪切强度缓慢提高,此时方阻开始增大。当玻璃相含量为1wt.%时,由于液相量不足,致密化烧结动力不足,且无法形成网络状结构使得铜粉烧结过程中出现大量团聚,形成孔洞,导电性和剪切强度都较差。随着玻璃相添加量增加,液相能够充分浸润铜颗粒,致密化烧结驱动力提高,形成致密的铜颗粒导电网络[8],方阻进一步减小,剪切强度增加。当玻璃相添加量超过7wt.%,不导电的玻璃相占比增加,电阻反而逐渐增大,此时铜颗粒与陶瓷基体的界面已经被充足的玻璃相充分浸润,因此剪切强度趋于稳定。

图5 铜浆的方阻和剪切强度与玻璃相添加量的关系 图6为不同玻璃相添加量铜浆烧结后表面扫描电镜测试图。从图中可以看出,当玻璃相添加量为1wt.%时,烧结后铜浆表面存在较多孔洞。当玻璃相添加量提高到4wt.%、7wt.%时,铜浆烧结致密,可看见明显的玻璃相形成的网络将铜颗粒均匀、紧密地连接在一起。当玻璃相添加量提高到10wt.%时,过多的玻璃相浮于铜浆表面,可焊性变差,对于封装器件后面对镀镍、镀金工艺形成不利影响。

图6 不同玻璃相添加量的铜浆SEM图

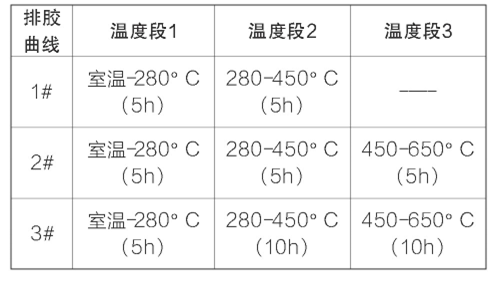

3.3 不同排胶曲线对铜浆性能的影响

在多层陶瓷封装外壳制备过程中,由于设计使用需求,引入大量埋层铜浆,且铜易氧化,需在还原气氛条件下烧结,在后期与陶瓷共烧的过程中存在排胶困难的问题。如表1所示,设置1#-3#3个不同的排胶工艺,通过调整排胶温度、排胶时间研究不同排胶曲线对于埋层铜浆在与陶瓷共烧过程中致密化烧结的影响。表1 不同排胶工艺的排胶温度及排胶时间

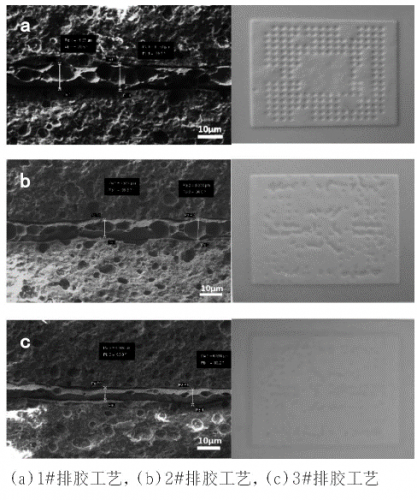

表1给出的是3种排胶曲线条件下完成烧结后,埋层铜浆断面的SEM图以及对应的多层陶瓷封装实验件(如图7所示)。从图中可以看出,当在450°C结束排胶,埋层铜浆在烧结完成后,导体膜层内部疏松多孔,孔洞较大,膜层厚度为11μm左右,样品印有大量埋层铜浆的区域出现明显的凸起。当增加450°C~650°C排胶温度段后,埋层铜浆孔洞减少,膜层厚度减小,但样品表面仍存在轻微凸起。当采用3#排胶曲线,延长排胶温度时间至10h时,减小升温速率,埋层铜浆实现致密化烧结,膜层厚度减小到6μm左右,样品表面平整。由上述分析结果可知,排胶温度、排胶时间对埋层铜浆的致密化影响很大。主要原因可能是排胶温度和升温速率影响了铜浆中有机载体是挥发。当排胶温度低于450°C时,有机载体中部分有机物无法完全挥发,使得剩余的有机物保留至烧结后期,最终形成起泡[9,10];同时,过快的升温速率会导致有机载体在短时间内集中挥发,在膜层中形成细小孔洞[11],这两者都会造成膜层疏松多孔。

适当提高排胶温度,延长排胶时间,降低升温速率,使得有机物能够完全、有层次性的挥发,实现埋层铜浆的致密化烧结,对于提高多层陶瓷封装外壳的平整度至关重要,也是实现铜浆在多层陶瓷封装外壳制备技术中应用的关键环节。

图7 不同排胶工艺条件下的铜浆SEM图

04

结论

本文将自制铜浆应用于多层陶瓷封装外壳制备技术,并探讨了烧结温度、不同玻璃相添加量对铜浆性能的影响。实验结果表明,当烧结温度为850°C,玻璃相添加量为7wt.%左右时,铜浆表现出良好的导电性和较高的剪切强度,满足高频高速、高可靠性陶瓷封装的应用需求。适当提高排胶温度、延长排胶时间,降低升温速率有利于埋层铜浆的致密化烧结,减少孔洞,从而改善多层陶瓷封装外壳的表面平整度。

——END——

声明: 欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为射频美学。 本公众号目前所载内容为本公众号原创、网络转载、其他公众号转载、累积文章等,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所