《芯片设计五部曲》:模拟IC、数字IC、存储芯片、算法仿真和总结篇(排名不分先后)。

上一集我们已经说了,模拟IC,更像是一种魔法。

我们深度解释了这种魔法的本质,以及如何在模拟芯片设计的不同阶段,根据常见的EDA工具特性和原理,从计算角度帮助模拟工程师更高效地完成吟唱施法。

芯片设计五部曲之一 | 声光魔法师——模拟IC

第二集:数字IC

假如我们想要录制一段声音,模拟信号的做法是把所有的声音信息用一段连续变化的电磁波或电压信号原原本本地记录下来。而按照一定的规则将其转换为一串二进制数0和1,然后用两种状态的信号来表示它们,这叫数字信号。

处理数字信号的芯片就是数字芯片,比如常见的CPU、GPU。

当声音变大或变小了,模拟信号都会跟着变化,所以模拟信号有无数种状态。状态之间微妙的差异,需要人的经验判断,有点玄学的成分。

而数字信号永远只有0和1两种状态,信号的转换严格遵循逻辑关系,一个输出对应唯一确定的结果,程序完全依照输出指令执行,这是科学。

数字IC设计工程师的设计目标:在PPA(Power、Performance、Area)三个指标上追求完美的平衡。

怎么玩转这门科学?

这,是一种艺术。

今天,我们就从资源需求、并行特征、数据敏感度等角度展开聊聊在数字芯片设计各阶段,如何利用不同EDA工具的特点,让数字芯片的设计研发效率获得显著提升。

和模拟芯片相呼应,这篇还是从计算角度出发,至于调度/管理/数据/协同/CAD等视角,会在后面的文章里体现~(比如第三集

和模拟相比,数字芯片需要使用EDA工具的场景更多,IC工程师们对于计算机的使用天然比较亲近。但就跟《解密一颗芯片设计的全生命周期算力需求》一样,只负责某项工作的研发可能不关心,或者只了解自己的这部分,IT对业务所知有限,也不一定清楚。除非有大佬坐镇,大多数公司的日常大概是以拍脑袋经验论为主。

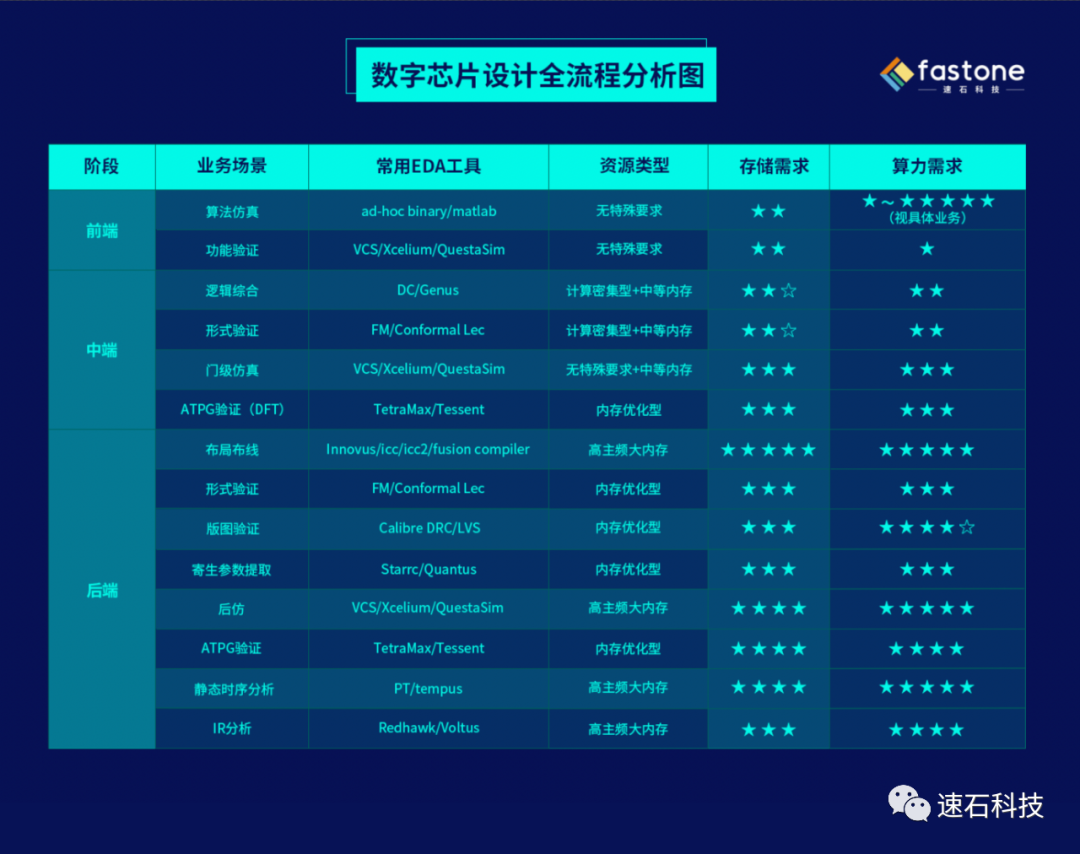

我们先来看一下大画面,数字芯片设计全流程分析图:

数字前端:前端设计/验证

数字中端:逻辑综合与DFT实现

数字后端:物理实现

资源需求

后端>中端>前端,数字后端·真·资源黑洞

数字前端,用RTL代码将芯片架构师的设计写出来,前端验证也主要是针对RTL的功能进行验证,偏逻辑功能。

数字中端,需要将RTL代码综合成网表并规划、插入各种用于芯片测试的逻辑电路,需要加入Foundry厂提供的标准单元库的工艺参数,验证也到了逻辑门这一级。

数字后端负责芯片的物理实现,先将电路网表通过自动布局布线画成版图,再进行寄生参数提取,创建一个可以精确模拟数字电路响应的模型,这一阶段会加入版图的寄生参数。

从代码到逻辑门电路再到物理层,随着阶段的演进,信息量逐级递增,计算时所需消耗的资源量也随之增加。

而在28nm以及更先进制程下,包含的工艺参数更多,电路更复杂,前中后端每一阶段的信息量级还会被进一步放大。

哪怕前端RTL基本一致,中端和后端因为Foundry厂工艺参数更多更复杂,同样的代码计算量也是更大的。

换个思路,我们举个栗子。

通过一个在数字前中后端都会出场的EDA工具来看看三大阶段的资源需求。

VCS的主要作用是将Verilog HDL(一种硬件描述语言)转成C语言,编译出来并执行。作为一个翻译官,ta的工作量取决于双方对话的频率,以及需要翻译的文本量。

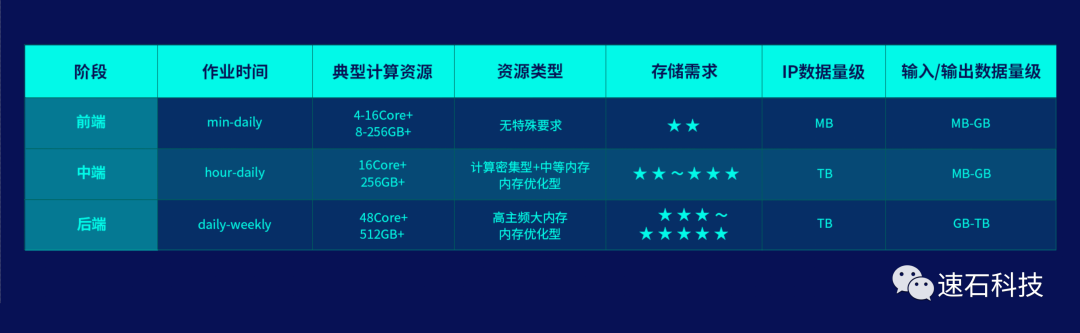

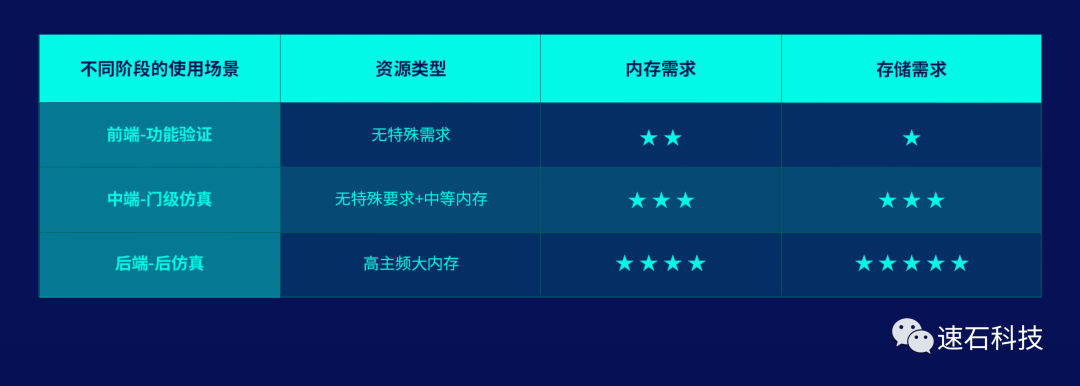

VCS在前端的功能验证、中端的门级仿真、后端仿真中都有出场,在不同阶段对任务资源的需求完全不同:

从前端到中端再到后端,虽然VCS的工作性质没变,但整体来说,消耗的资源越来越多了。

综上,数字后端设计与验证环节相比中端和前端资源需求更高、运算时间更长、数据量更大,往往会占据整个项目周期资源需求量的50%以上。

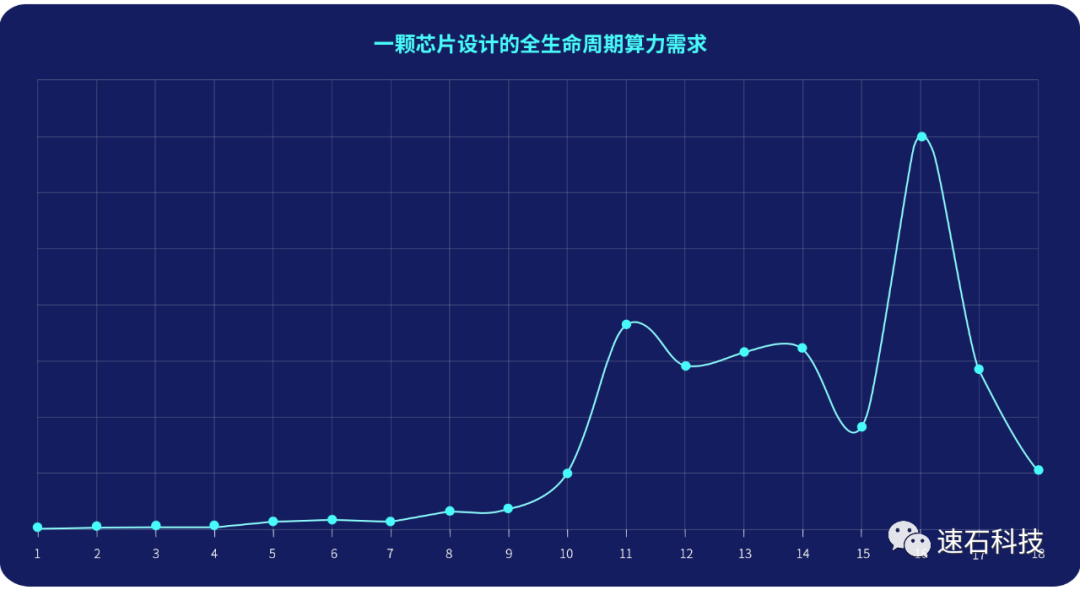

下图是我们某客户全生命周期月度算力实际用量曲线,可以看到后端的波峰相当明显,详情戳:解密一颗芯片设计的全生命周期算力需求

典型并行场景

静态时序验证&版图验证

互不干扰指的是,拆分为小任务之后,任务之间互相不干扰,可以不同步。

从前端到中端再到后端,任务数量越来越多。

任务的并行度决定了速度提升的空间。

静态时序验证:最常见且并行度较高

静态时序验证是最常见的设计场景之一,基本原理是检查各信号通路上经过的门电路,然后累加门延迟,求取整个路径的信号延迟。

沿信号通路求Delay Time的过程,就是沿信号通路不停做简单加法。

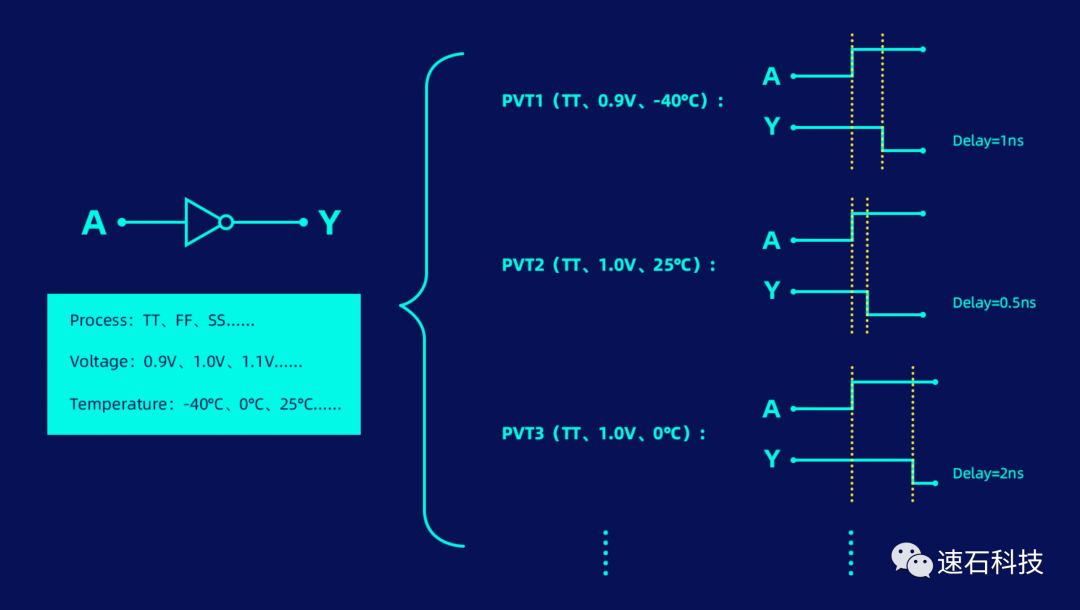

在静态时序验证过程中,有一个PVT的概念。

我们需要验证逻辑门在不同的工艺(Process)、电压(Voltage)、温度(Temperature)条件下的延迟。

首先,列出可能的条件,如:

工艺:TT、FF、SS……

电压:0.9V、1.0V、1.1V……

温度:-40°C、0°C、25°C……

随后,穷举每一种可能性,如:

PVT1=TT、0.9V、-40°C

PVT2=TT、1.0V、25°C

PVT3=TT、1.0V、0°C

……

最后,验证逻辑门在每一种PVT条件下的延迟:

数字芯片中有着无数这样的逻辑门,每一个PVT下,逻辑门都有对应的Delay Time,而P、V、T之间可以有很多种组合,就会有很多个Delay Time的情况需要验证。

这一场景,天然适合暴力堆机器。

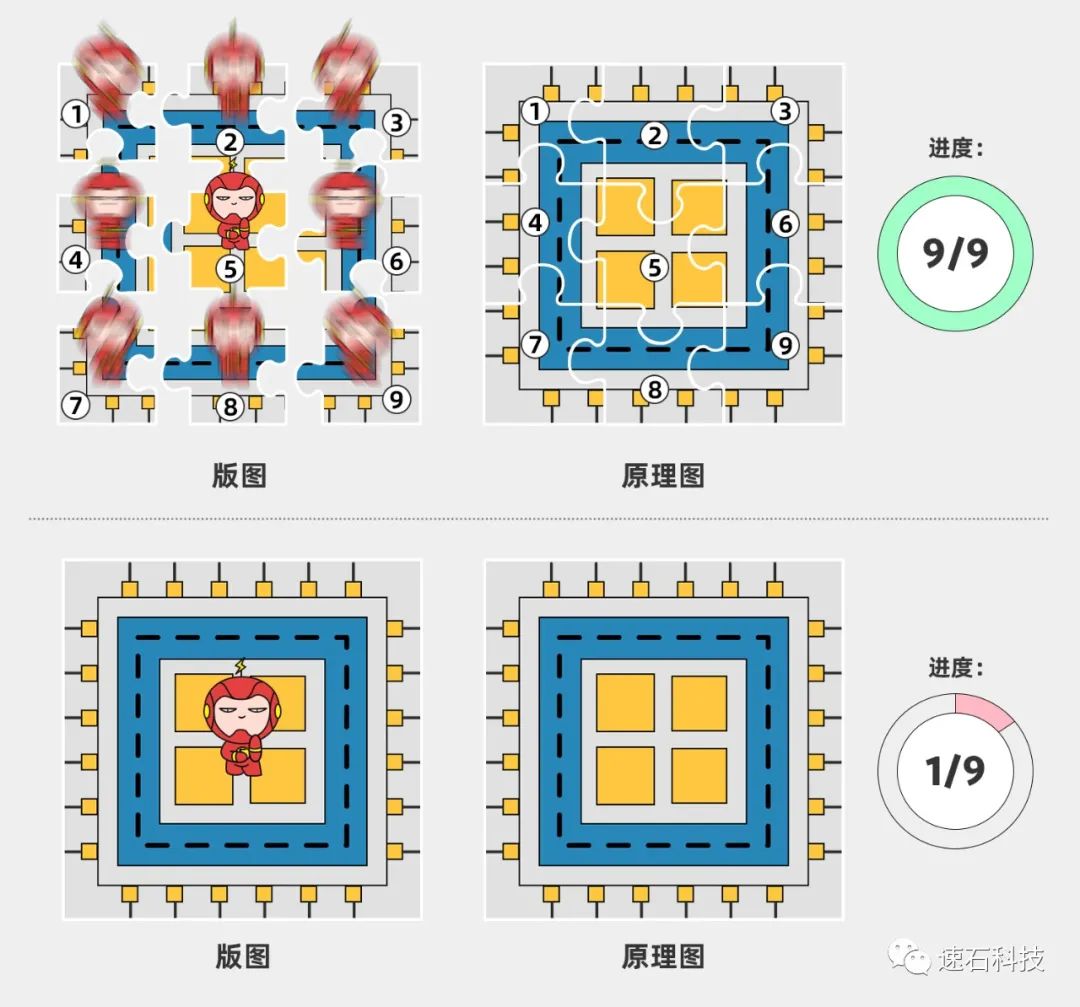

版图验证:最高并行度

模拟芯片和数字芯片,这一场景的原理一模一样,使用的EDA工具也完全相同。

版图验证属于检查类任务,以模块为单位,本质上是数据对比工作,重内存需求,子任务间没有数据关联,是数字芯片设计与验证中并行度最高的场景。

这一阶段很适合利用云上的内存优化型资源,使用“小F影分身术”(版图分割术),通过暴力堆资源的方式快速完成任务。

关于版图验证,我们在《芯片设计五部曲之一 | 声光魔法师——模拟IC》中有更详细的说明。

数据敏感度

前端>中端>后端,但是不用担心

好了,接下来我们看看这些数据都会出现在哪些阶段:

数字前端有大量RTL代码,甚至部分公司在此过程中还自己开发了IP,属于数据安全等级最高的那一拨。许多公司都会严格管理这部分数据,设置一定的保密等级,甚至固定放在某几台机器上。

中端则涉及到部分的RTL代码、IP和PDK数据,以及一些Netlist、Session和Report。

后端彻底告别了代码,以IP、PDK、版图和数据敏感度较低的数据为主。

如果你要做一款游戏,前端相当于游戏的源代码,中端是详细的角色形象设计稿,后端就是玩家拿到手的游戏光碟了。

前端泄密,恭喜你的对手达成“代码级抄袭”;

中端泄密,别人能照着样子把仿品做出来,但没有源代码参考,知其然不知其所以然;

后端泄密,等对方逆向明白,大半年时间也过去了,你的下一代产品已经在路上了。

值得一提的是,如果使用的是先进工艺,Foundry厂也会对IP/PDK数据有保密要求。

所以在选择云上业务场景的时候,我们一般优先推荐数字后端先来。当然,会根据每家公司的实际情况进行具体分析。(以后会写到,这次一定

那么,前端或者中端是不是就适合用云了呢?

甚至,在某些情况下,IC设计公司会面临全部数据无论敏感度高低必须存放在本地的情况,比如一些高保密项目(军工项目或国家重点项目),或者有点微妙的竞争关系,怎么办?

我们有针对性的存算分离解决方案,欢迎来对号入座。

存算分离解决方案到底是什么?我们是如何实现的?扫描文末二维码关注小F,对暗号“存算分离”抢先了解~

这里还有燧原科技的一手体验,戳此先睹为快:【案例】燧原科技:芯片设计“存算分离”混合云实践

关于数字IC设计,从不同设计阶段的计算任务视角出发,我们总结了四点: