来源:科技新报

随着 LED 尺寸不断微缩,Mini LED、Micro LED 技术发展,更清晰、更高分辨率的显示器油然而生。然而,LED 发挥性能的同时,体积也达到极限,这种限制在 AR、VR 等近距离显示尤其明显,并造成「纱窗效应」(Screen Door Effect),即用户感觉画素间出现空隙和条纹。

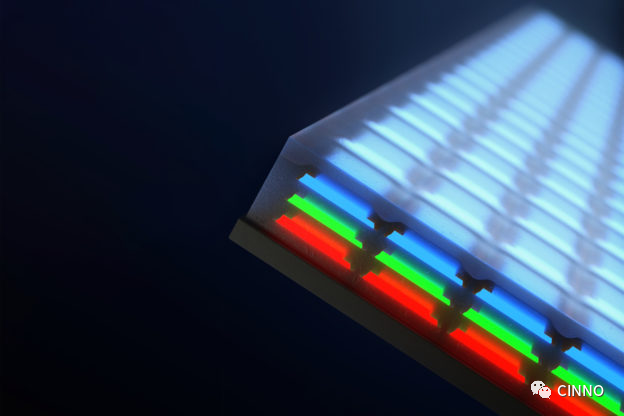

传统显示器每个画素由红、绿、蓝三个并排排列的子画素组成,Micro LED 显示器亦如此。科学家推测,虽然 Micro LED 无法像 OLED 画素紧密,若每个 Micro LED 画素跟一个子画素宽(而非三个),就能在一定数量的荧幕空间挤出三倍画素,大幅提高图像分辨率。麻省理工学院(MIT)团队开发独特方法,透过超薄膜制程垂直堆栈 Micro LED,而非横向排列,让封装更紧密。

科学家先将红、绿、蓝 Micro LED 薄膜一层层堆栈,类似层蛋糕排列,再细细切成网格状,分割成许多独立画素。每个堆栈画素可产生全部商业色彩范围,宽度约 4 微米,这些 Micro LED 可封装成 5,000ppi,即每吋 5 千个画素密度。

麻省理工学院机械工程副教授 Jeehwan Kim 指「这是最小 Micro LED 画素,也是期刊报导的最高画素密度」,垂直画素化能在较小范围有更高分辨率。研究论文最近发表于《自然》杂志(Nature)。

研究人员指出,传统显示器每个红、绿、蓝画素都是横向排列,限制创建每个画素的大小。不过麻省理工学院是垂直堆栈所有三个画素,理论可将画素面积减少三分之一。

随后,团队展示透过改变施加到每个红、绿、蓝色膜的电压,可在单画素产生各种颜色。举例如果红色电流强、蓝色电流弱一点,画素就会呈粉色,有助创建所有混合颜色,使显示器有接近所有可用商业色彩。

团队正在研究可同时控制数百万个 Micro LED 画素的方法,研究人员透露「有源矩阵」(active matrix)将是需进一步开发的东西。

Micro LED 矩阵有效分辨率为 5,000ppi,这是文献最高画素密度,相比之下,三星最新 OELD 显示荧幕约 500ppi,目前最清晰 VR 设备也低于 1,000ppi。如果 Micro LED 商业化,垂直画素能大幅提升分辨率,尤其 VR 和 AR 应用,不过要为这种显示器供电又是完全不同的挑战。

更多商务合作,欢迎与小编联络!

扫码请备注:姓名+公司+职位

我是CINNO最强小编, 恭候您多时啦!

CINNO于2012年底创立于上海,是致力于推动国内电子信息与科技产业发展的国内独立第三方专业产业咨询服务平台。公司创办十年来,始终围绕泛半导体产业链,在多维度为企业、政府、投资者提供权威而专业的咨询服务,包括但不限于产业资讯、市场咨询、尽职调查、项目可研、管理咨询、投融资等方面,覆盖企业成长周期各阶段核心利益诉求点,在显示、半导体、消费电子、智能制造及关键零组件等细分领域,积累了数百家大陆、台湾、日本、韩国、欧美等高科技核心优质企业客户。