之前介绍了用ModlSim独立仿真带ISE IP核的仿真工程,本次介绍用ModelSim独立仿真带Vivado IP核的仿真工程。整体步骤基本一样,只是do文件分成了两个文件。使用工具Vivado2017.2 && Modelsim 10.5。

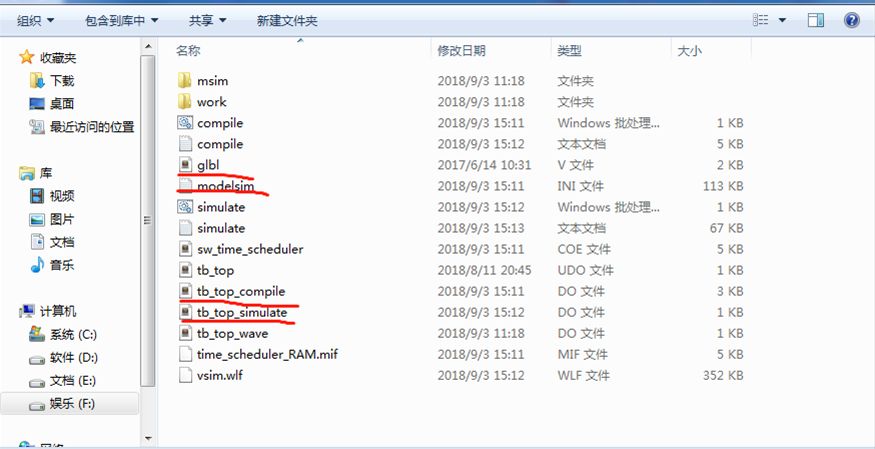

1、找到Vivado调用Modelsim仿真时自动产生的仿真文件,如下图红线所示。

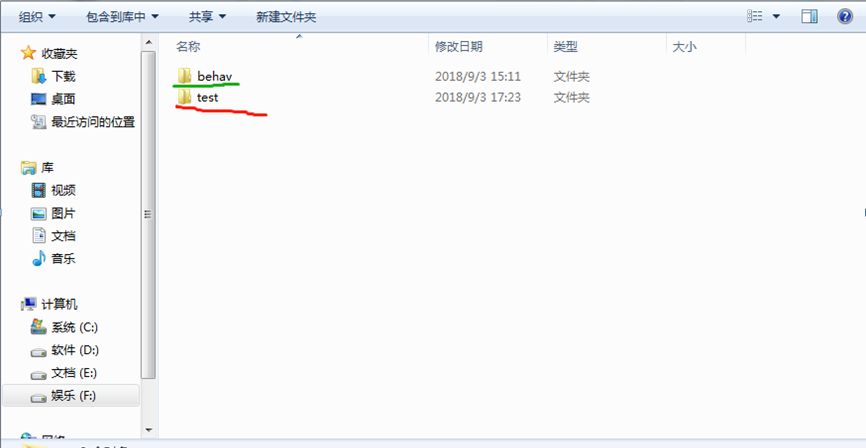

2、在behave文件夹同级路径下新建立一个文件夹,本实例中为test。

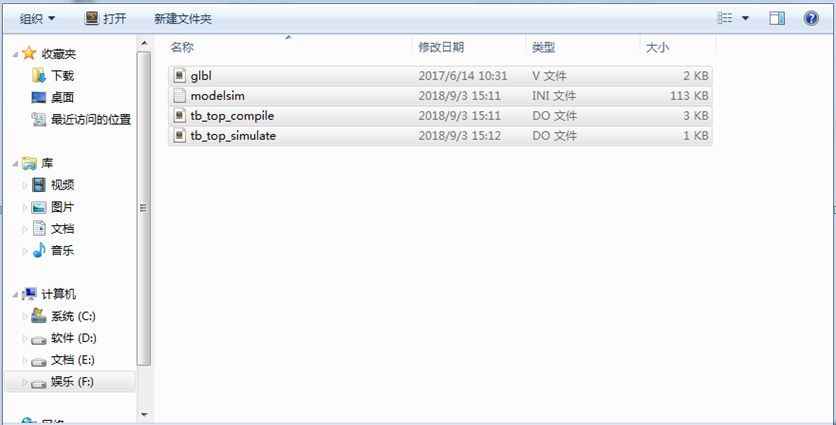

3、将所需的仿真文件复制到新文件夹中。

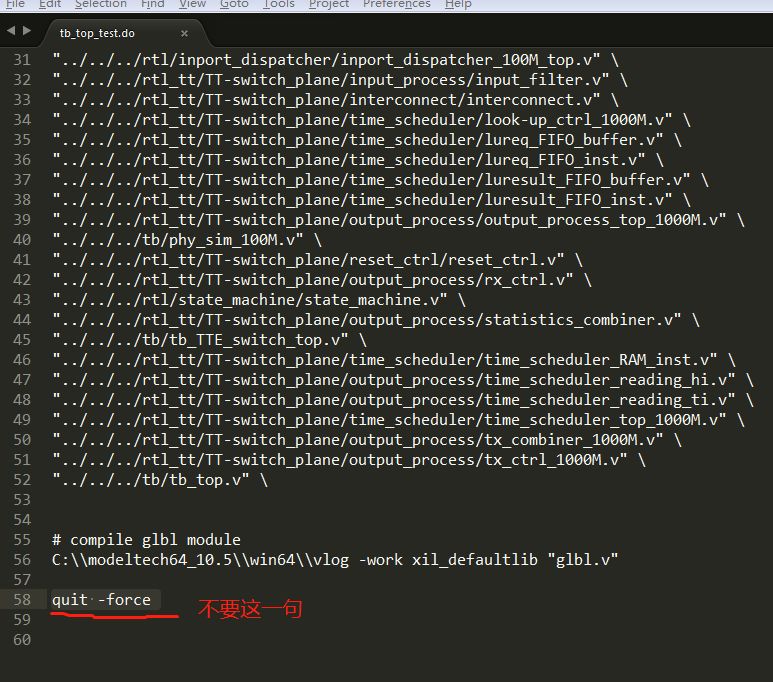

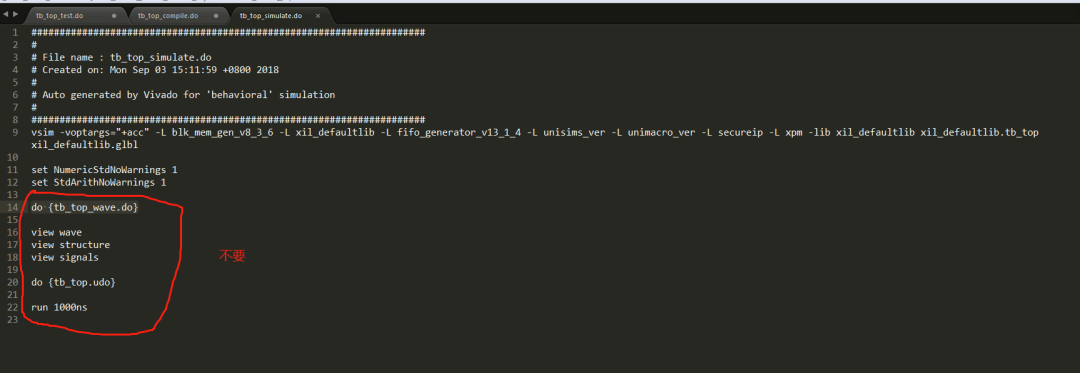

4、将两个.do文件的内容合并成一个文件。

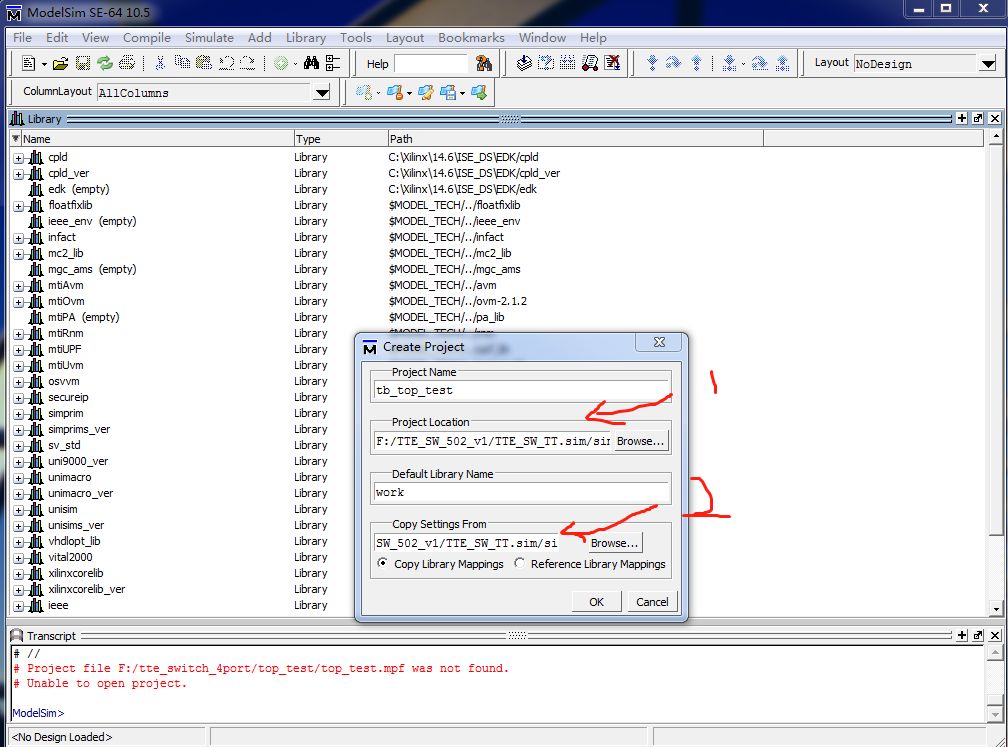

5、打开modelsim,新建工程,在Project_location选步骤3新建的文件夹,Copy_SettingsFrom选择该文件夹下的modelsim.ini文件,然后点击OK.

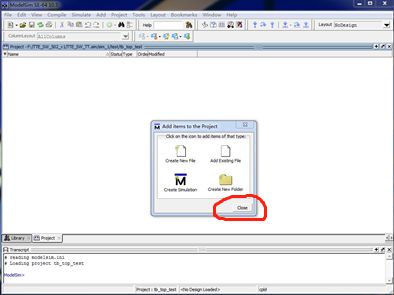

6、点击close

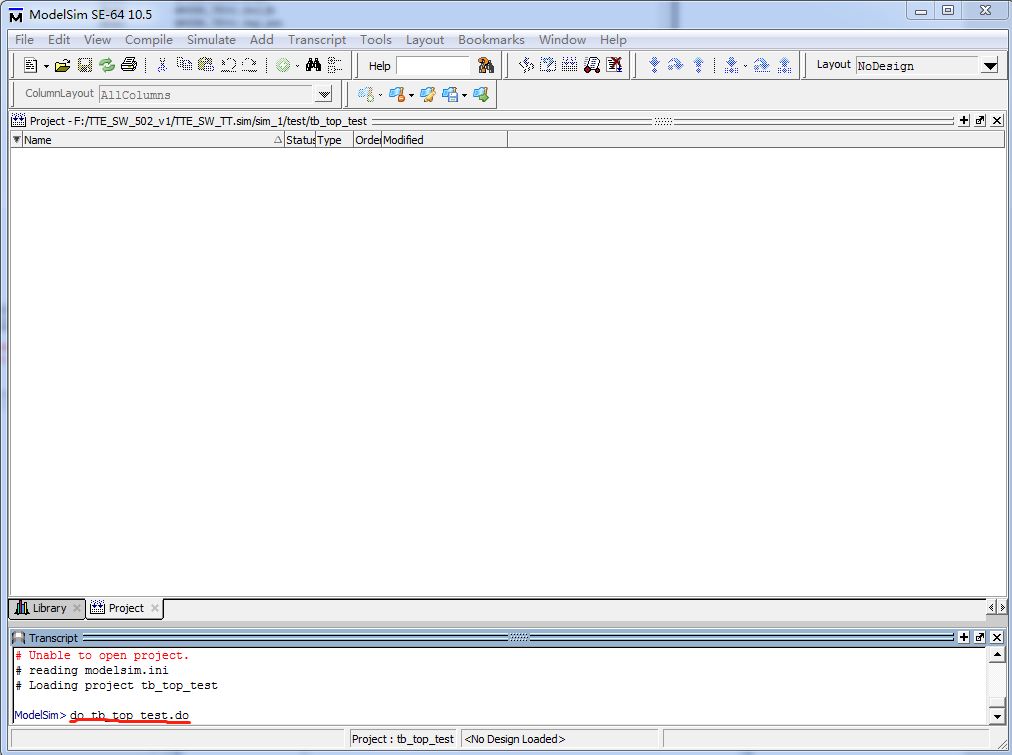

7、运行步骤4所生成的.do文件

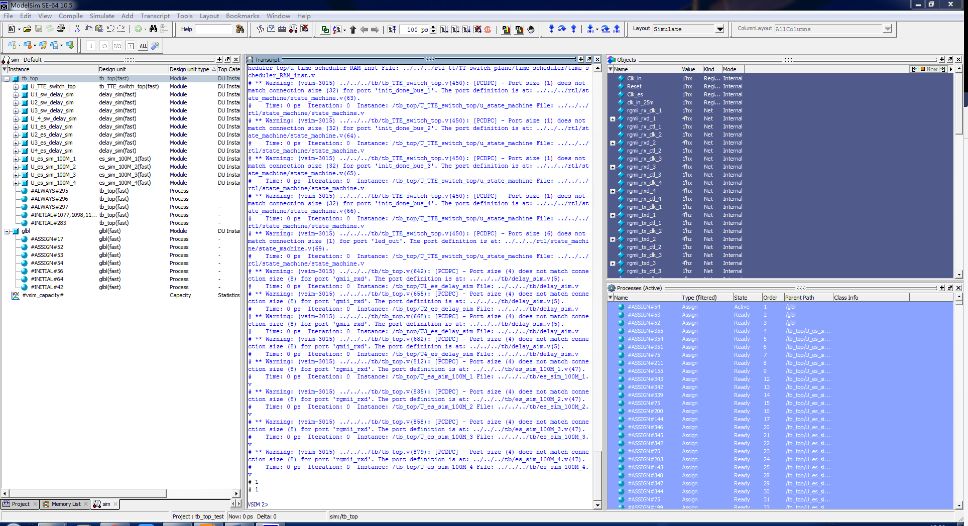

8、运行后会出现下图所示的界面,将信号添加进波形图。

9、在波形界面进行仿真,第一次运行出现下图所示界面,点击否(这个界面可能多次弹出,点否就行了)。

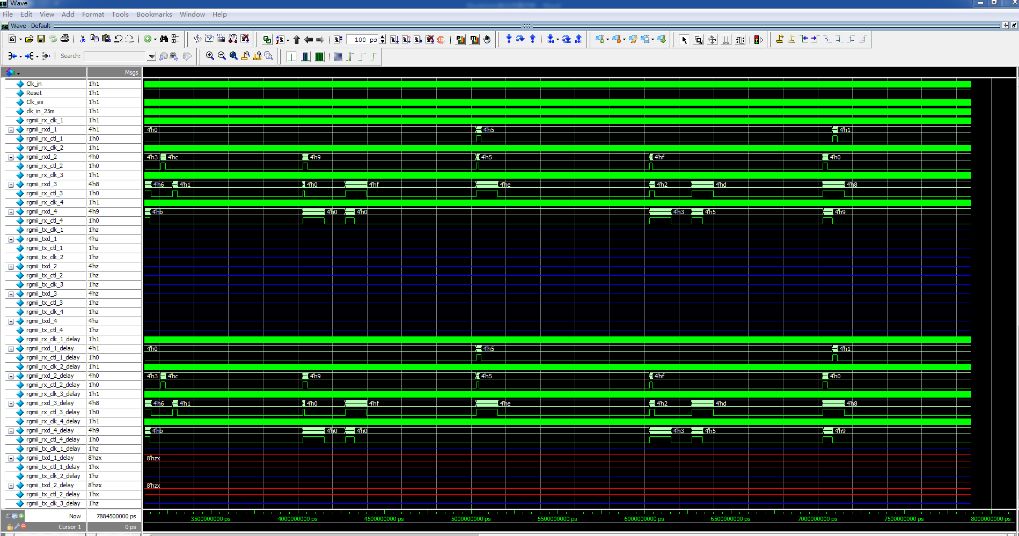

10、再进行仿真,即可得到波形图

https://cloud.tencent.com/developer/article/1137595

https://blog.csdn.net/u013098336/article/details/80809586

https://blog.csdn.net/USB_ABC/article/details/69897590

https://blog.csdn.net/ningan1987/article/details/4657410

http://www.voidcn.com/article/p-efujwurl-ds.html

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群