点击左下角阅读原文,有详细介绍。

Arbiter: Arbitrates between competing requesters 仲裁器-在竞争请求者之间进行仲裁

ASIC: Application specific integrated circuit.专用集成电路。

Audio codec: Device/program that compresses/decompresses digital audio 音频编解码器-压缩/解压缩数字音频的设备/程序

BTB: Branch target buffer 分支目标缓冲区

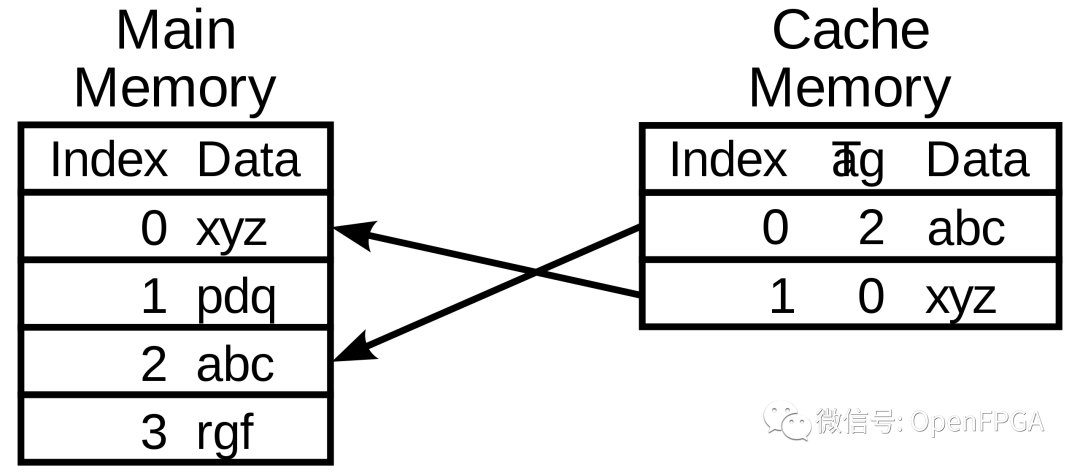

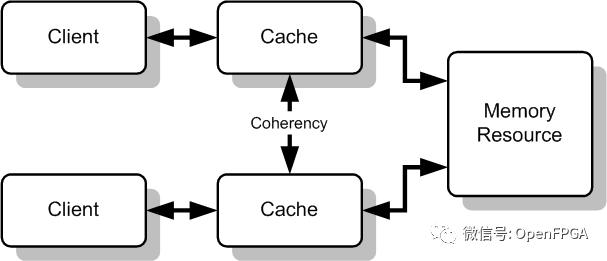

Cache: Local storage of program and/or data for future use. 程序和/或数据的本地存储以供将来使用。

CISC: Complex instruction set computing 复杂指令集

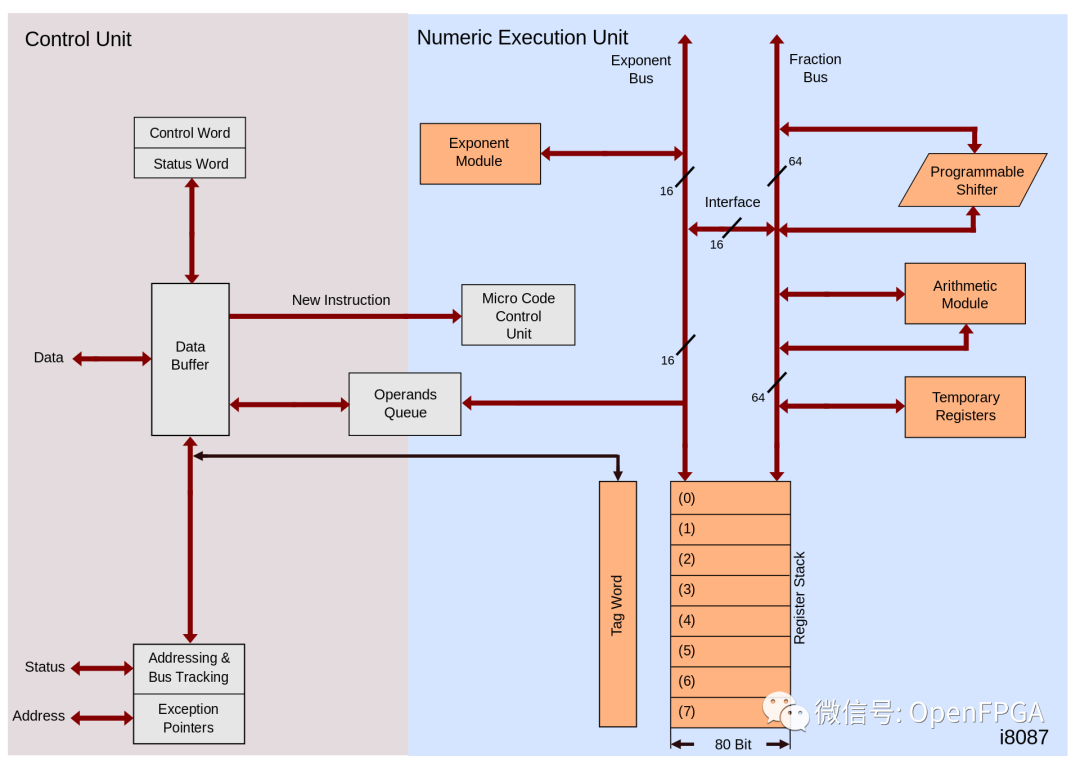

Coprocessor: A processor used to supplement operations of a primary (host) processor.协处理器-用于补充主处理器操作的处理器。

CPI: Cycles per instruction 每条指令的周期

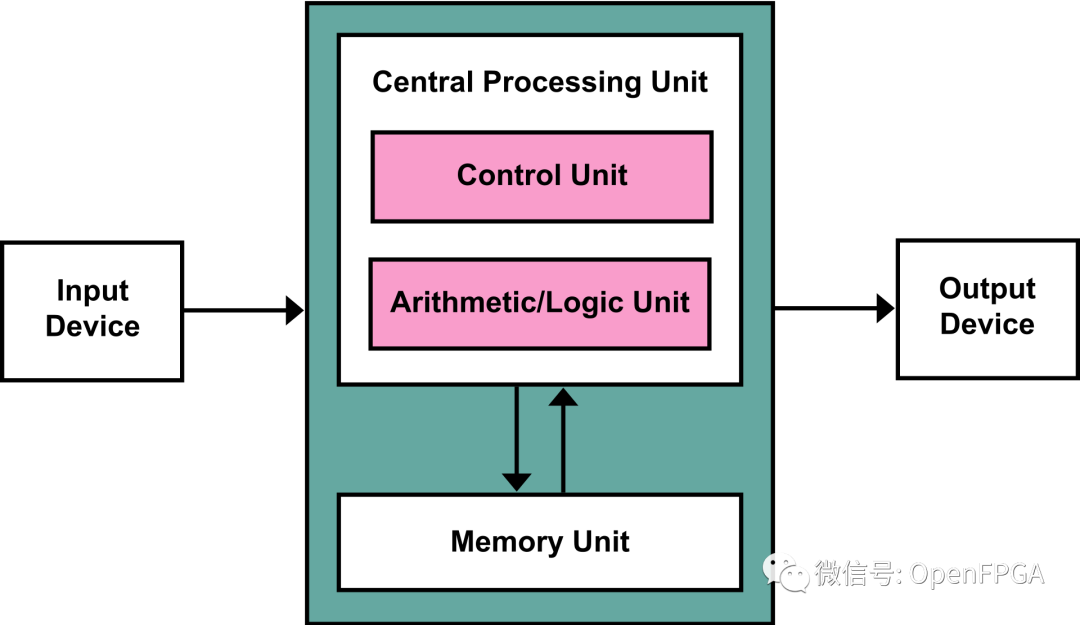

CPU: Central processing unit 中央处理器

CRC: Cyclic redundancy check 循环冗余校验

CSA: Carry save adder 进位保存加法器

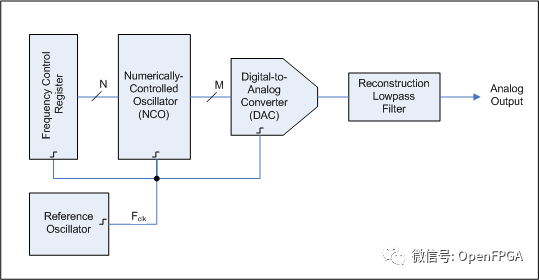

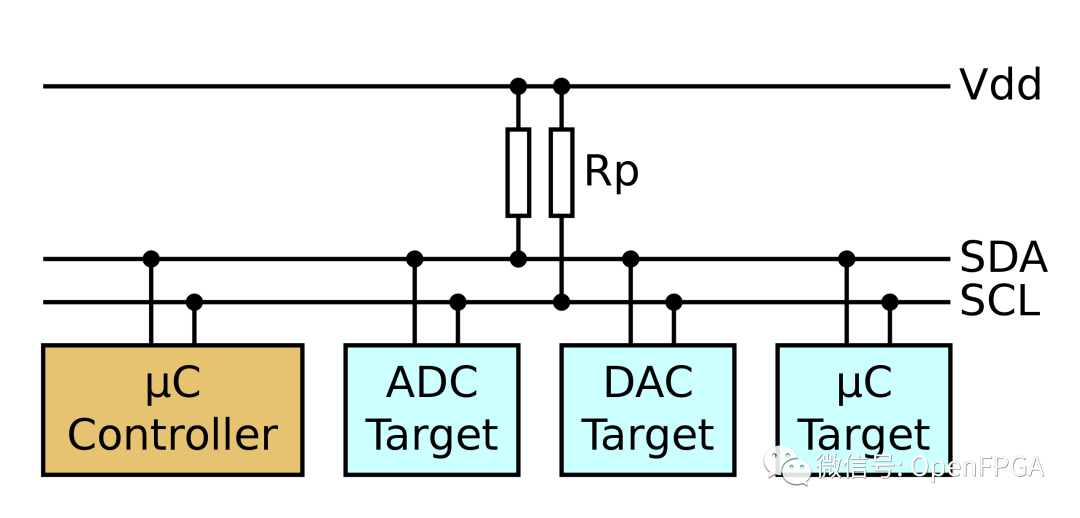

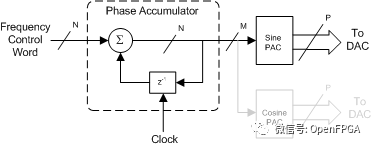

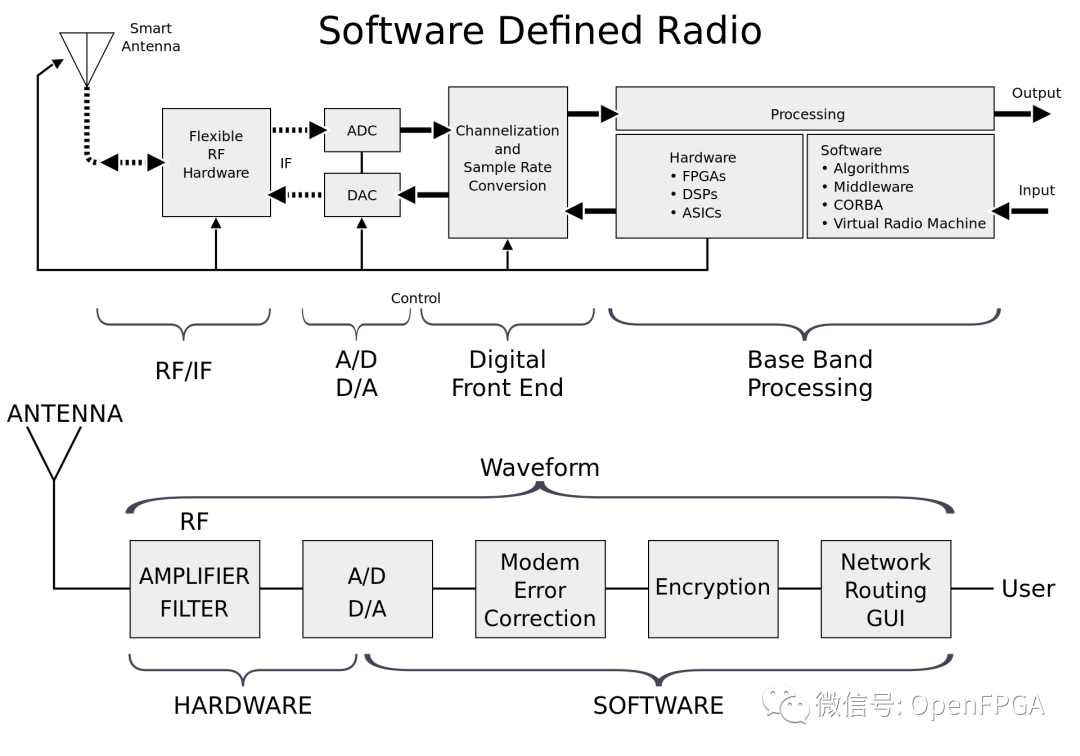

DAC: Digital to Analog Converter 数模转换器

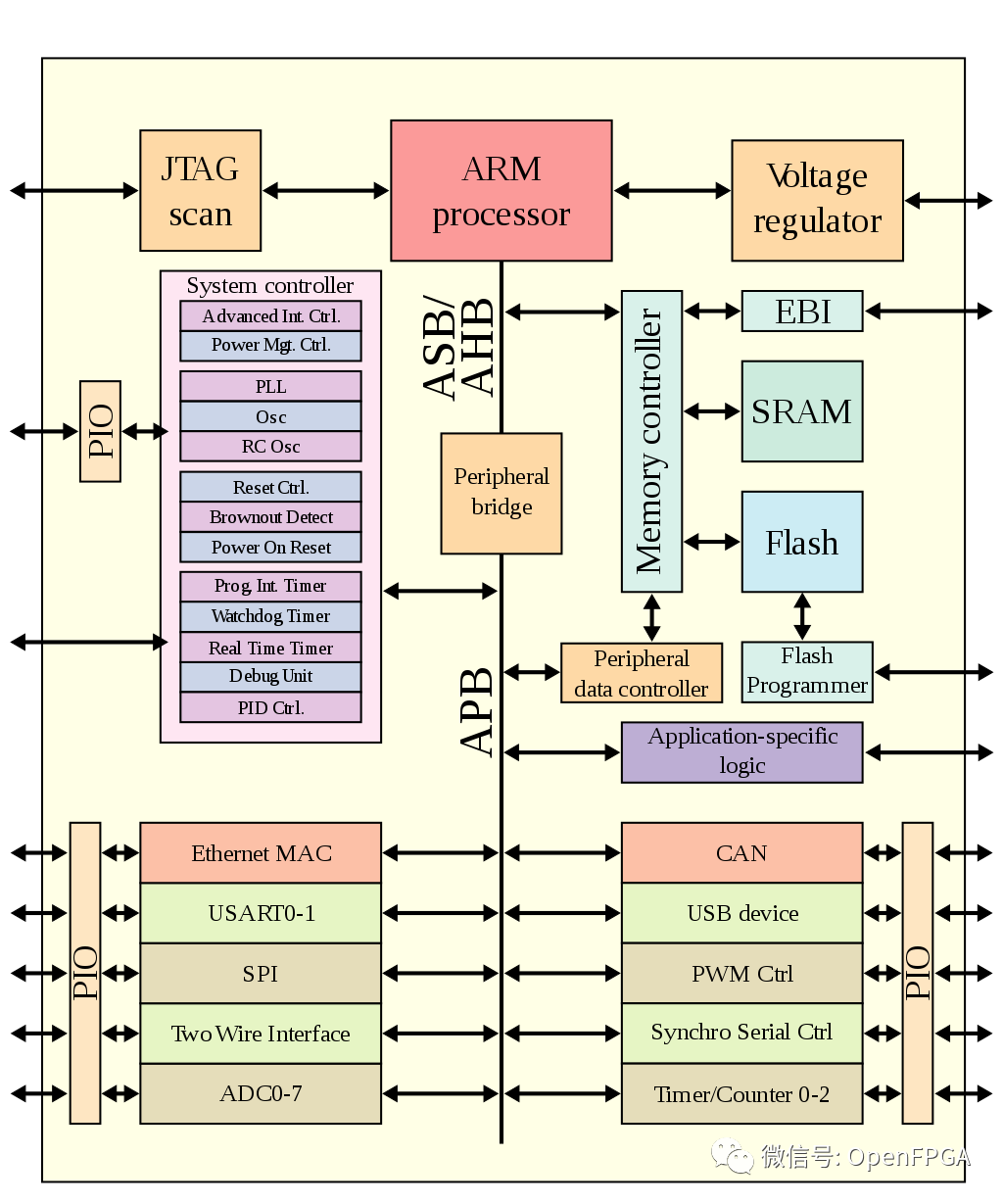

DMA: Direct memory access 直接内存访问

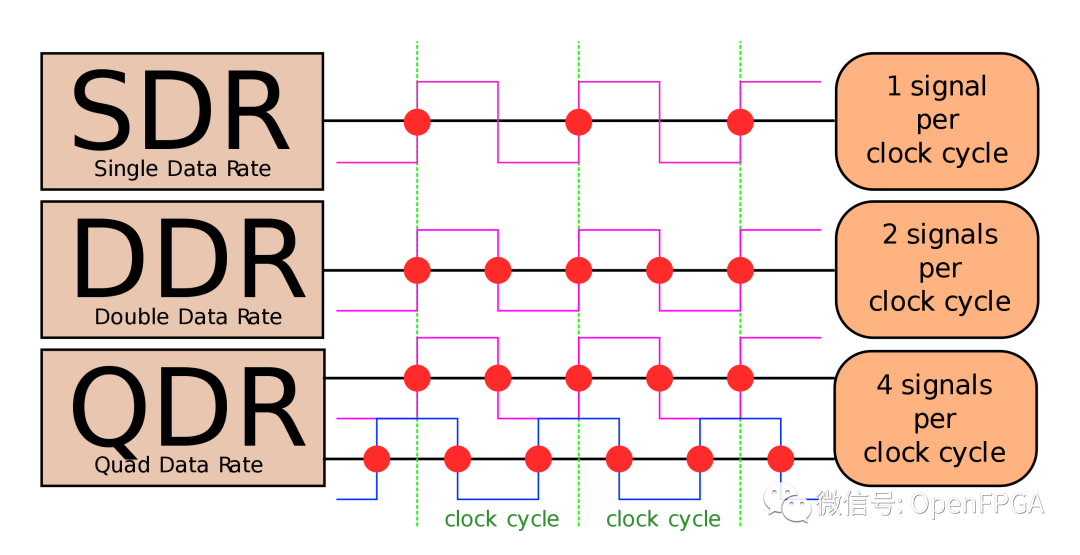

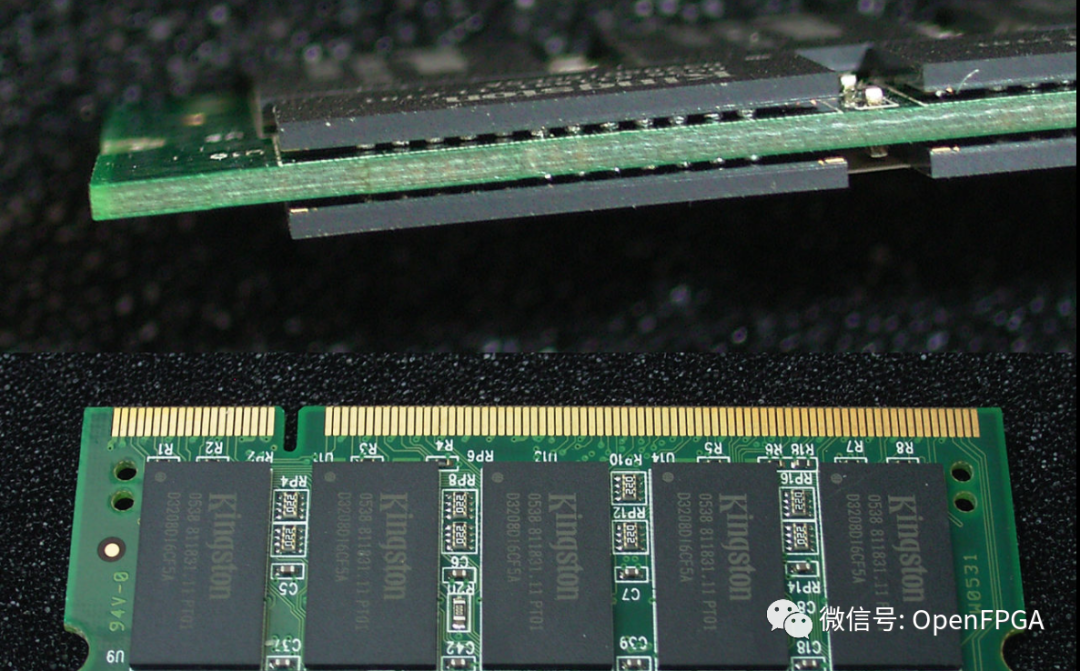

DDR Double data rate 双倍数据速率

ECC: Error correcting code 纠错码

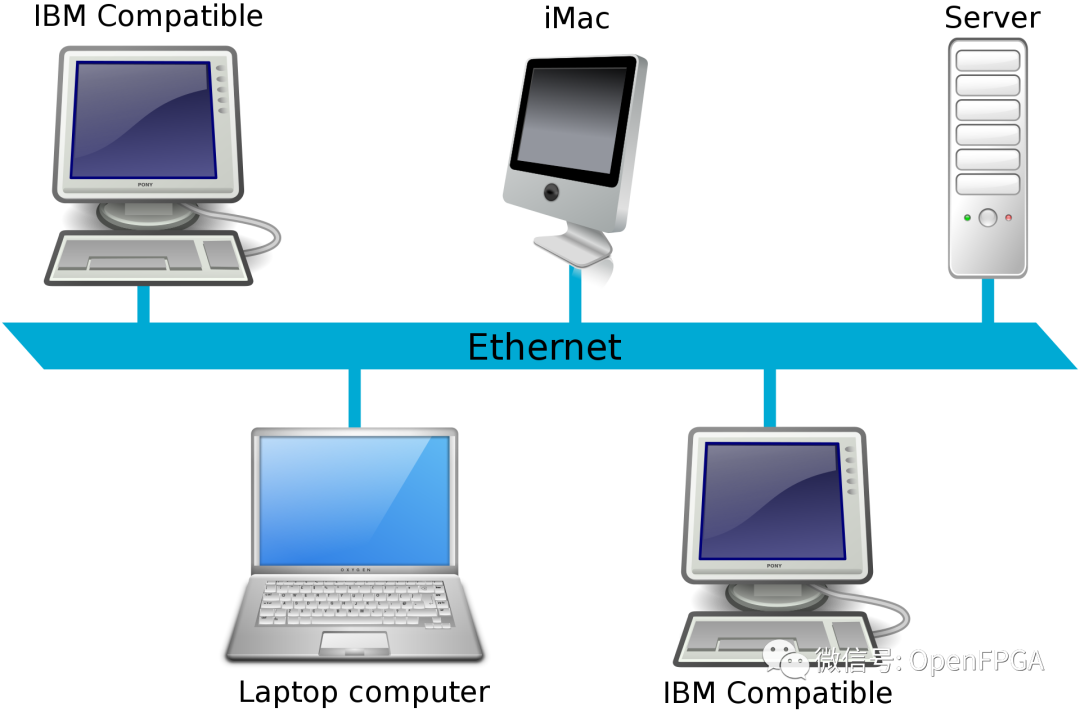

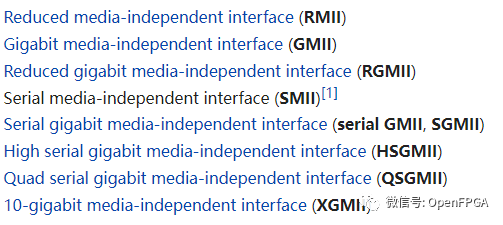

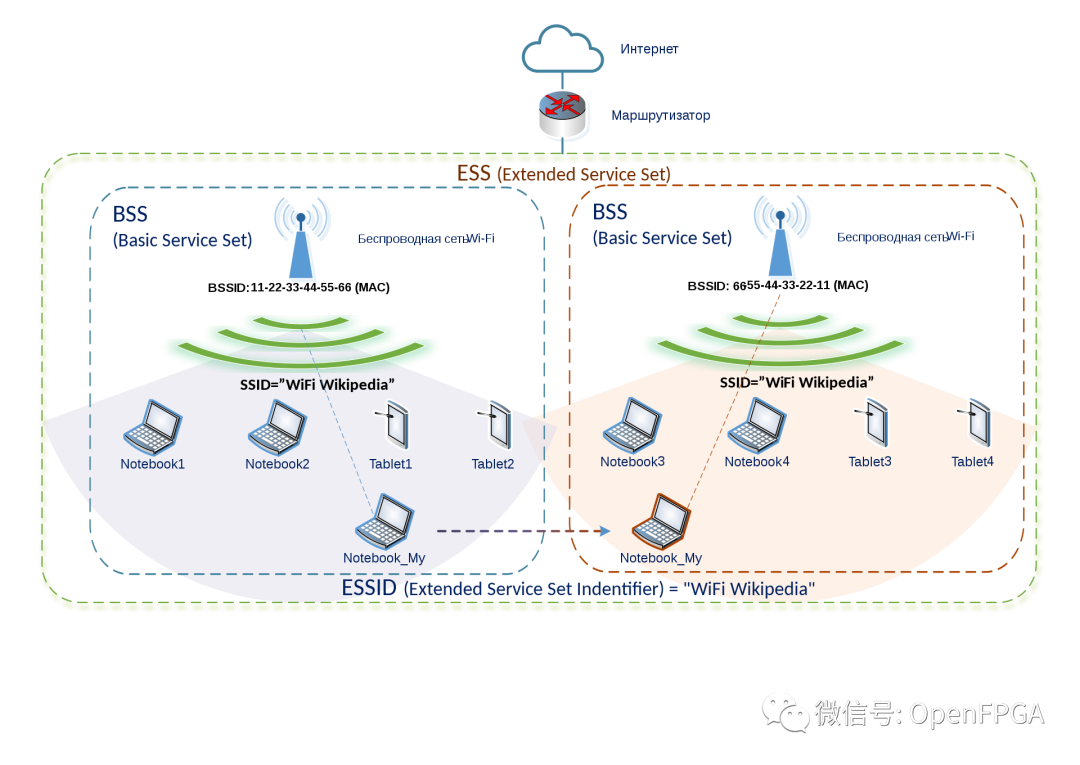

Ethernet: Family of standard network technologies 标准网络技术系列

Fault Tolerance: The ability of a system to keep operating in the event of failure of one of its components. 容错-系统在其组件之一发生故障的情况下保持运行的能力。

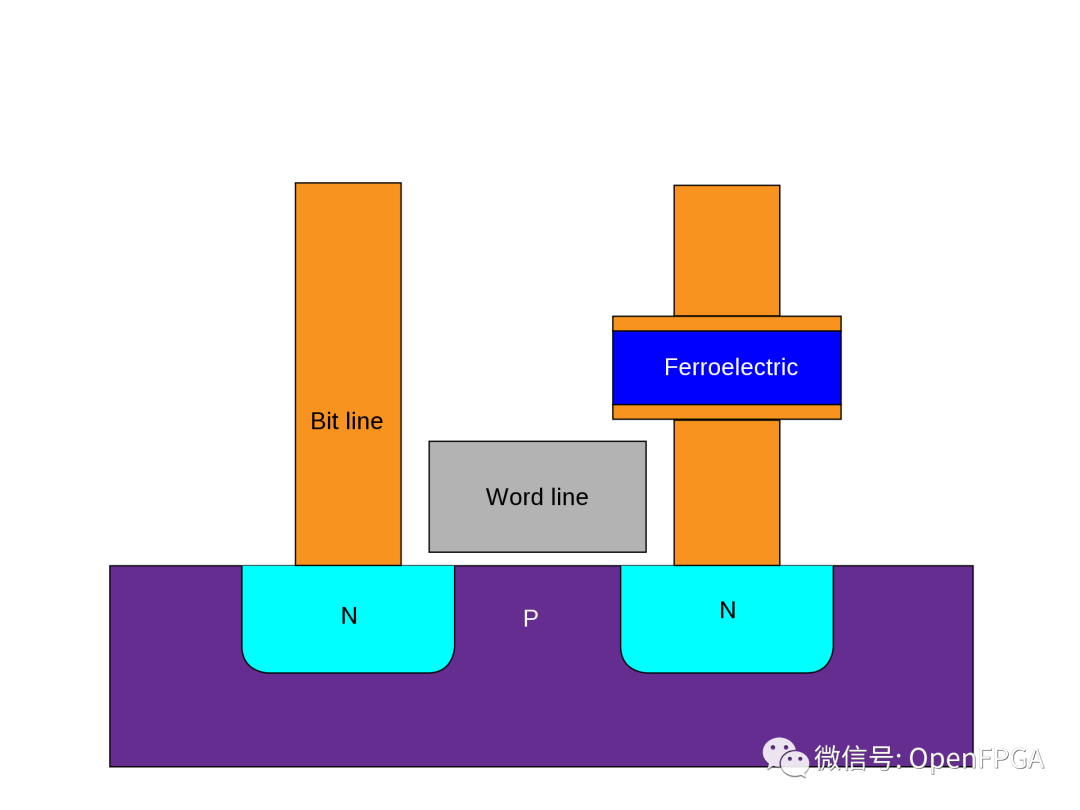

FRAM: Non-volatile RAM based on ferroelectric layer.基于铁电层的非易失性 RAM。

FPGA: Field-programmable gate array is a chip that can be reprogrammed "in the field". 现场可编程门阵列

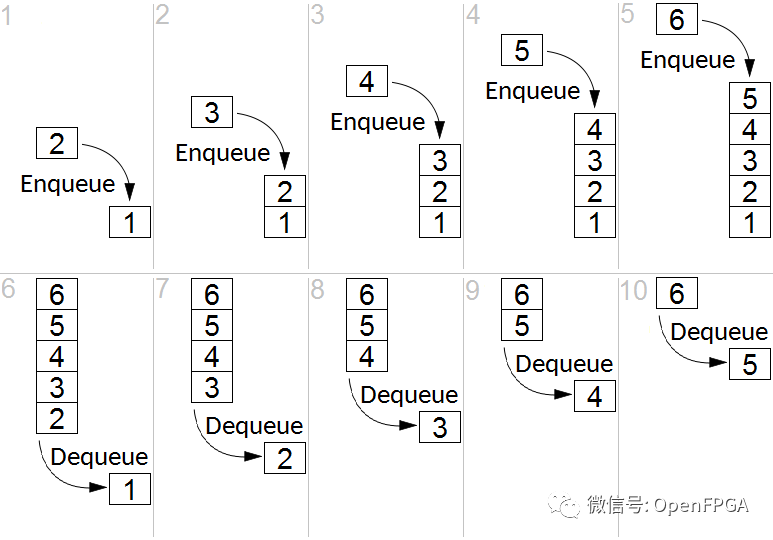

FIFO: First in first out buffer 先进先出缓冲区

FPU: Floating point unit 浮点单元

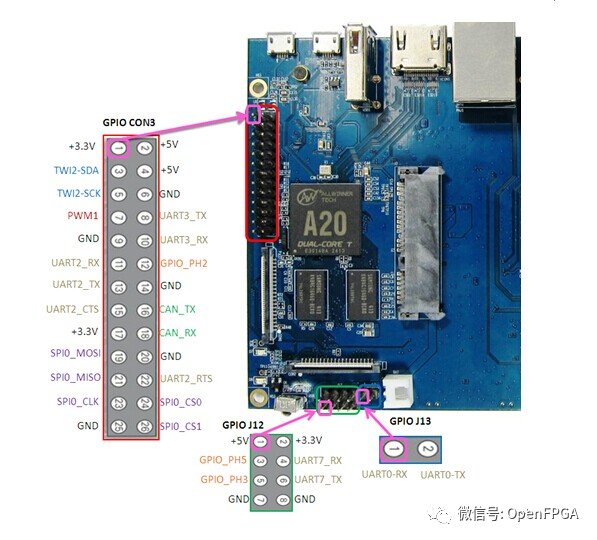

GPIO: General purpose input output, controllable at run time 通用输入输出,运行时可控

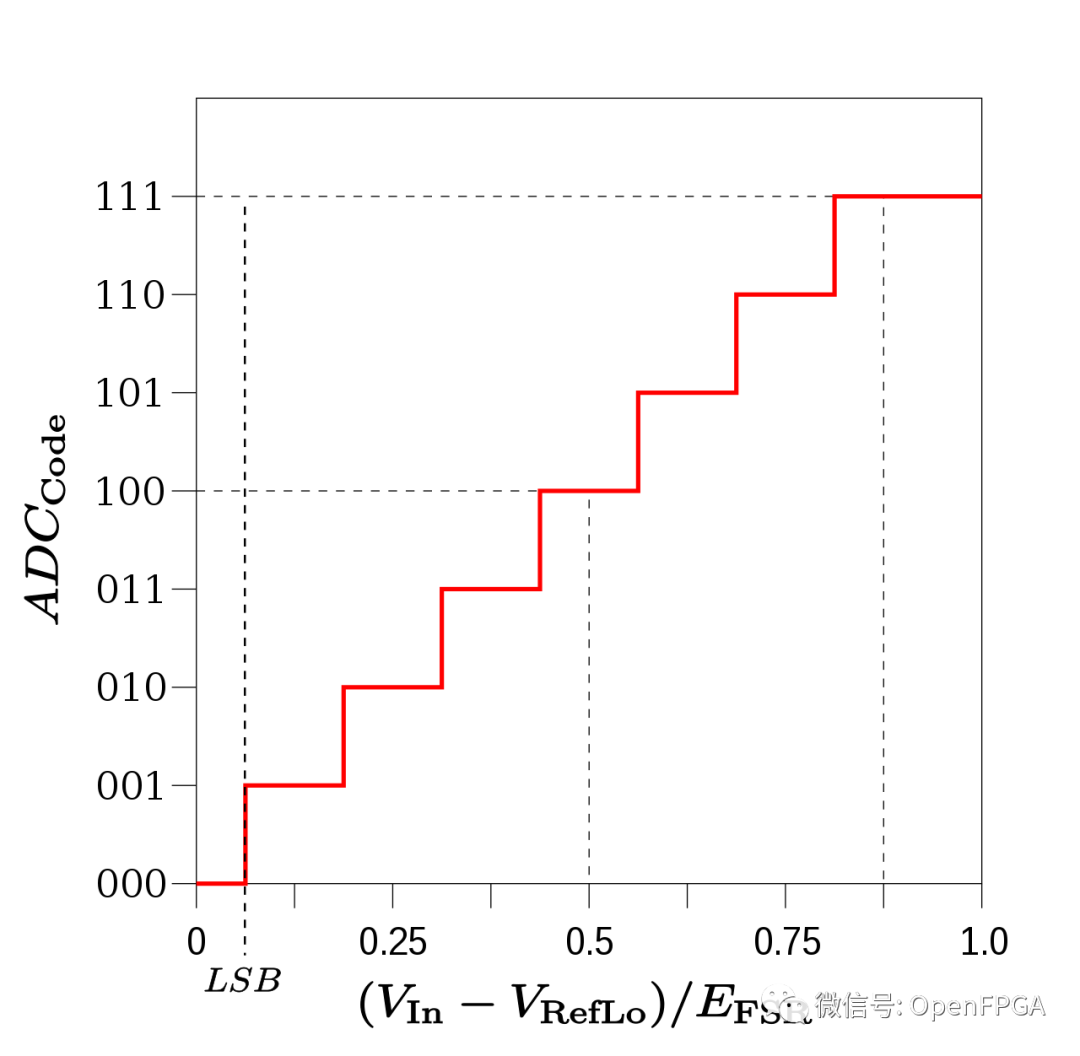

LSB: Least significant bit 最低有效位

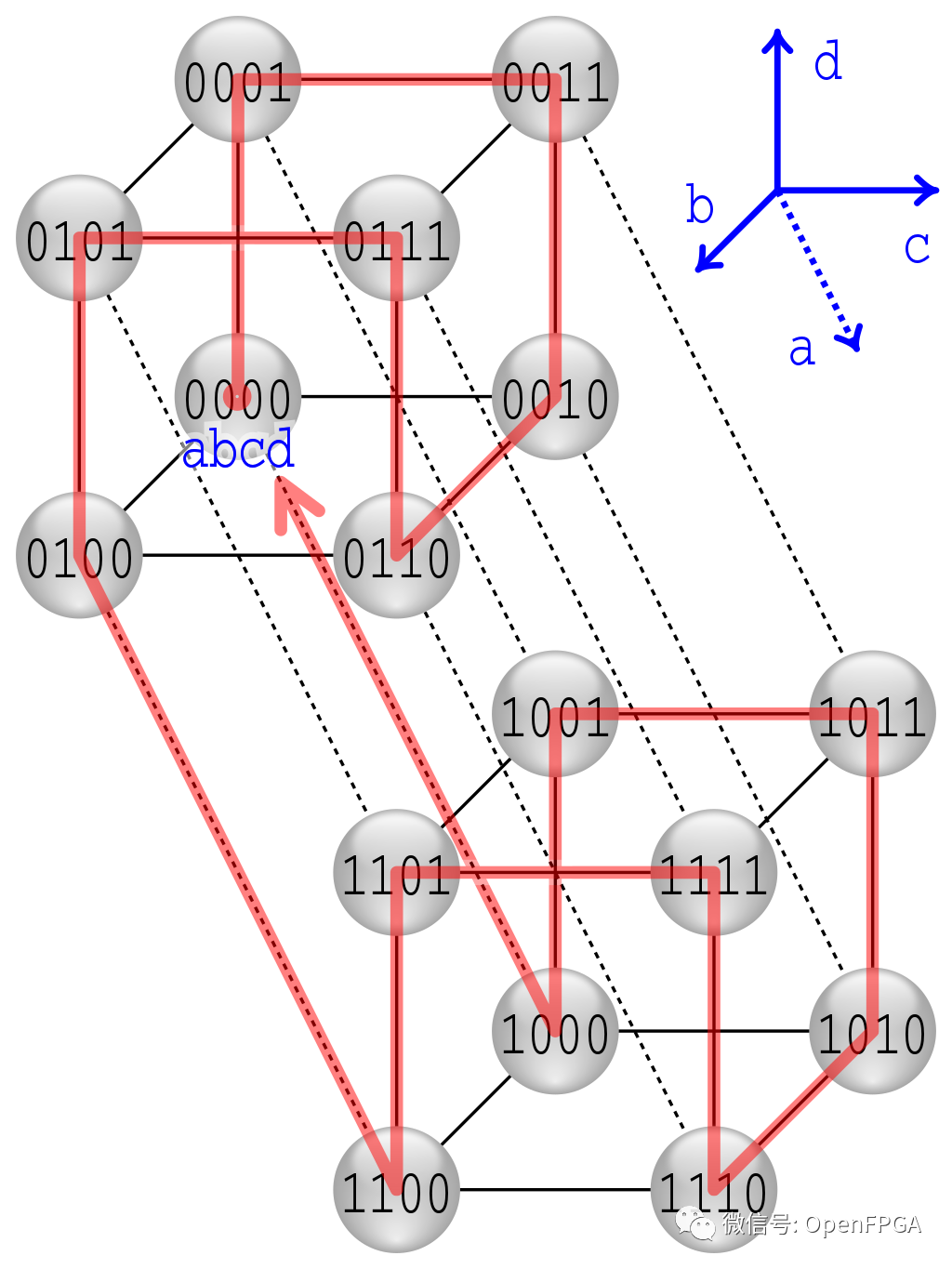

[LUT] (https://en.wikipedia.org/wiki/Lookup_table): An array that replaces runtime computation with a simpler array indexing operation 查找表(LUT) 是一个数组,它用更简单的数组索引操作代替运行时计算。

MSB: Most significant bit 最高有效位

MUX: Multiplexer 多路复用器

Multiplier: Binary multiplier 二进制乘数

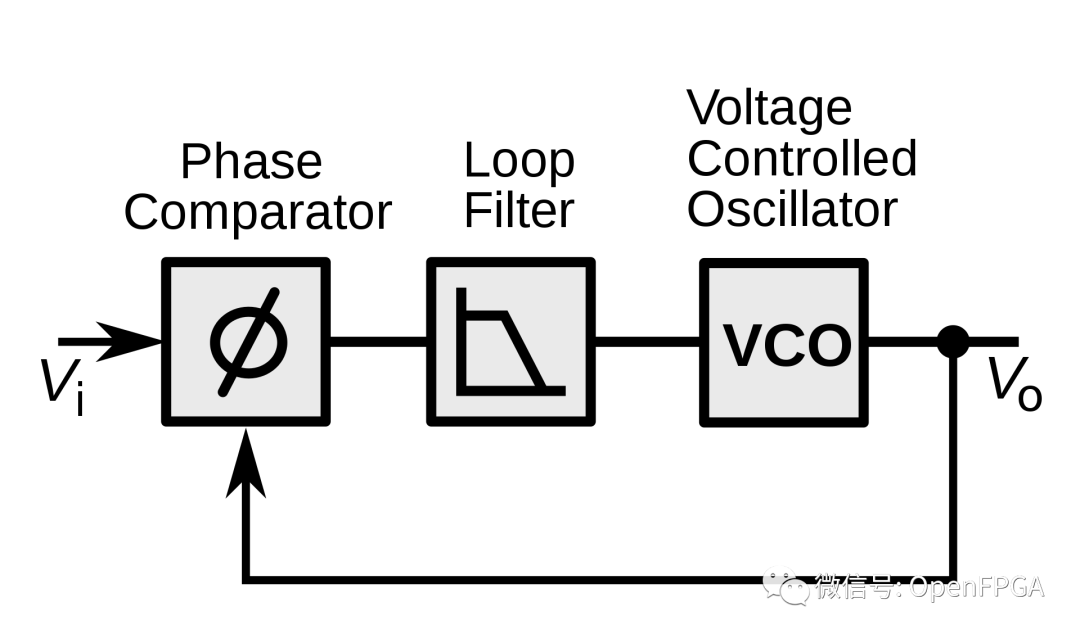

NCO: Numerically controlled oscillator 数控振荡器

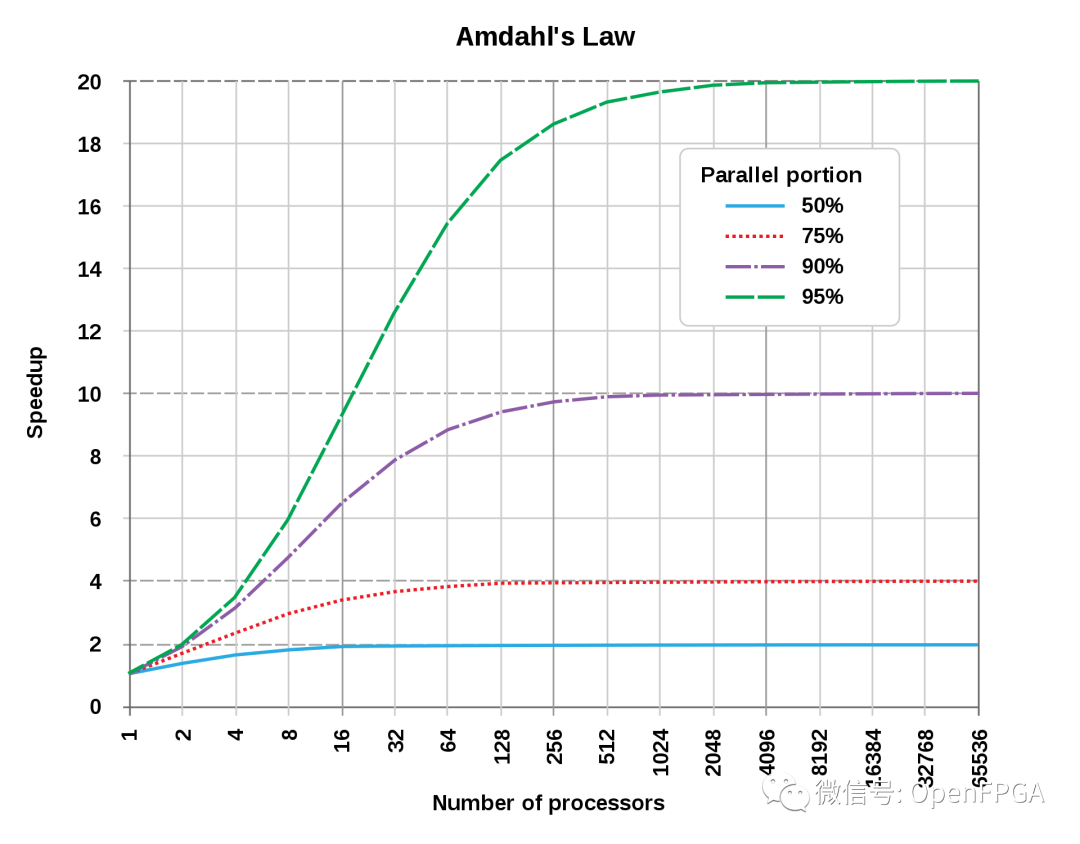

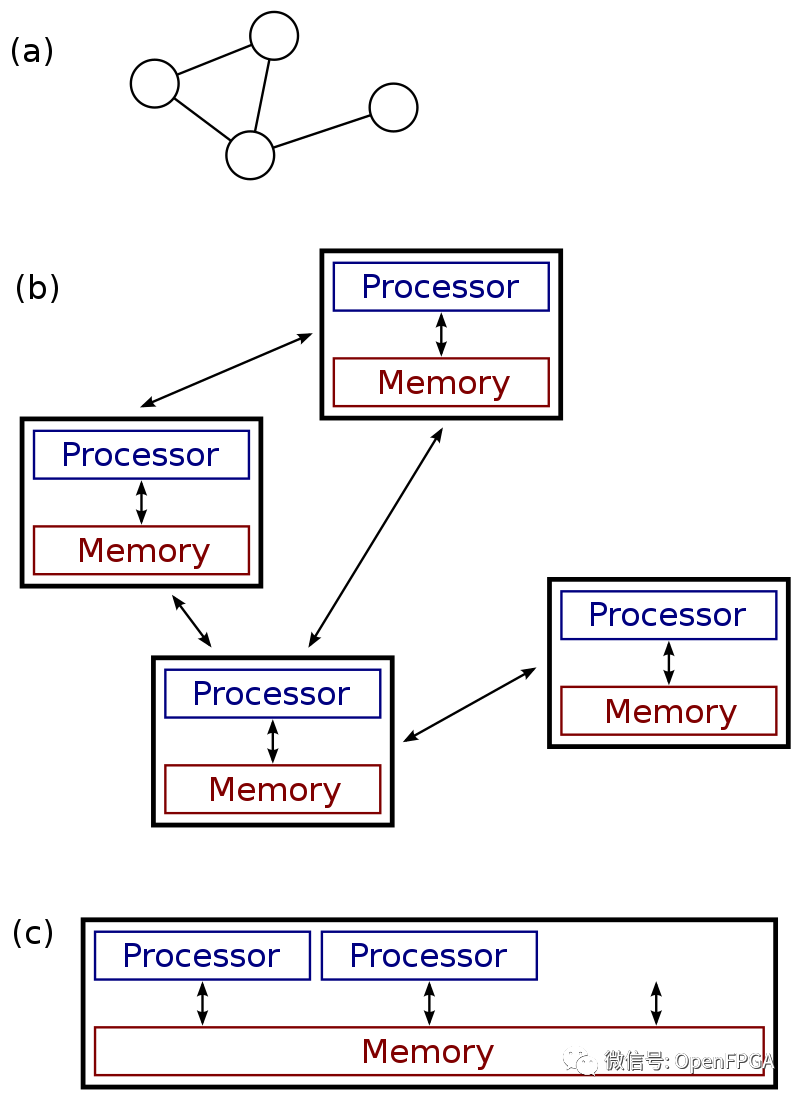

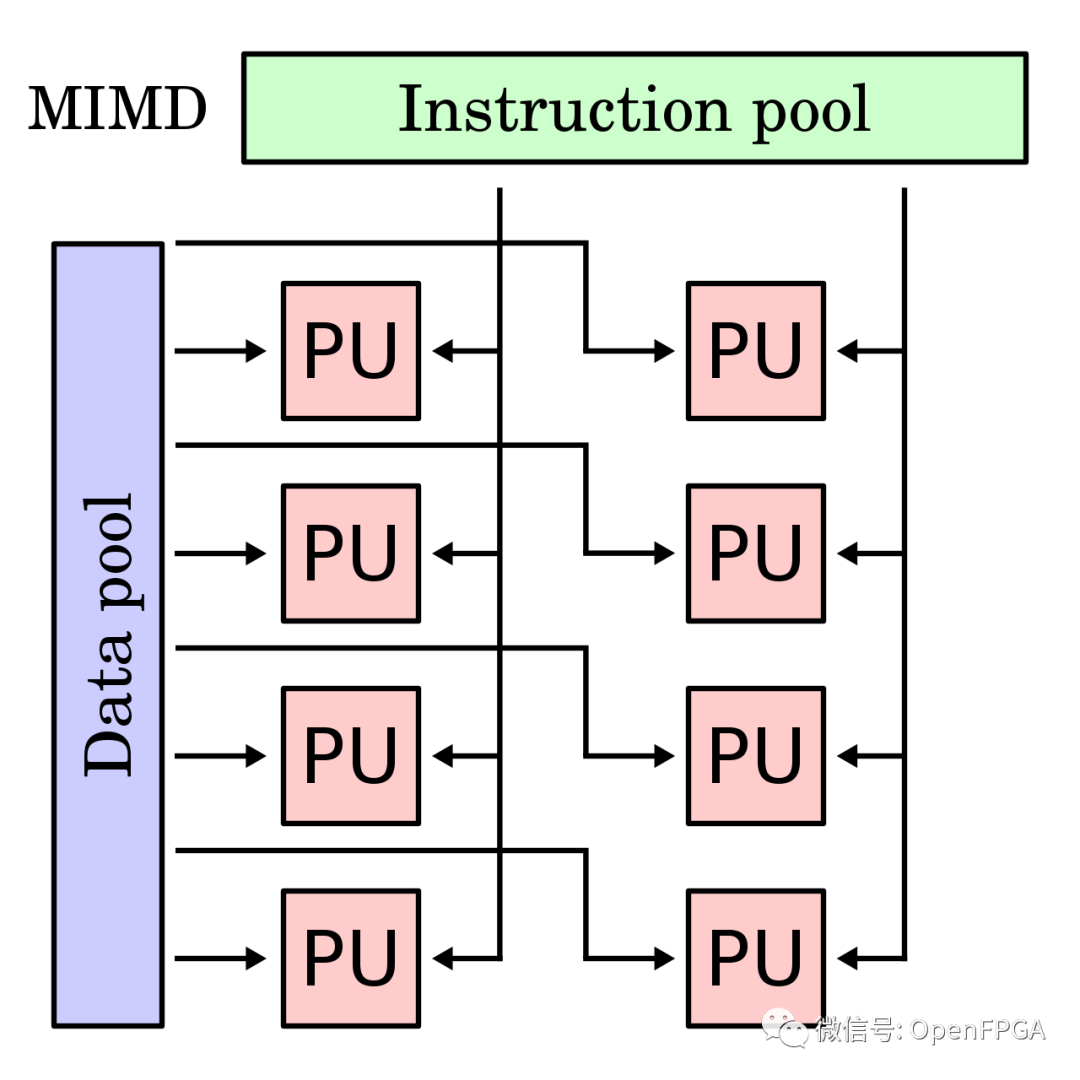

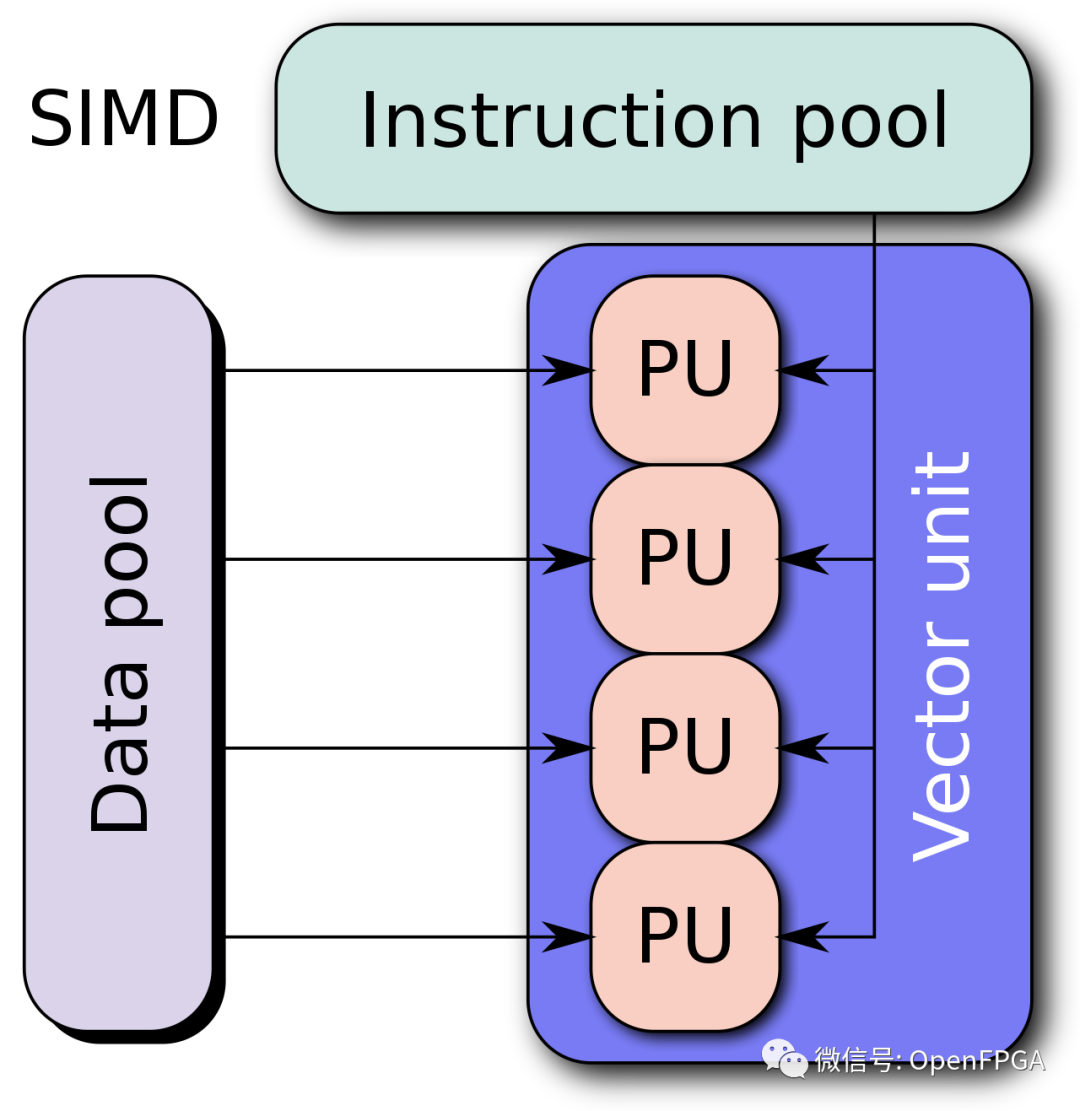

Parallel Computing: A type of computation where many operations are carried out simultaneously. 并行计算

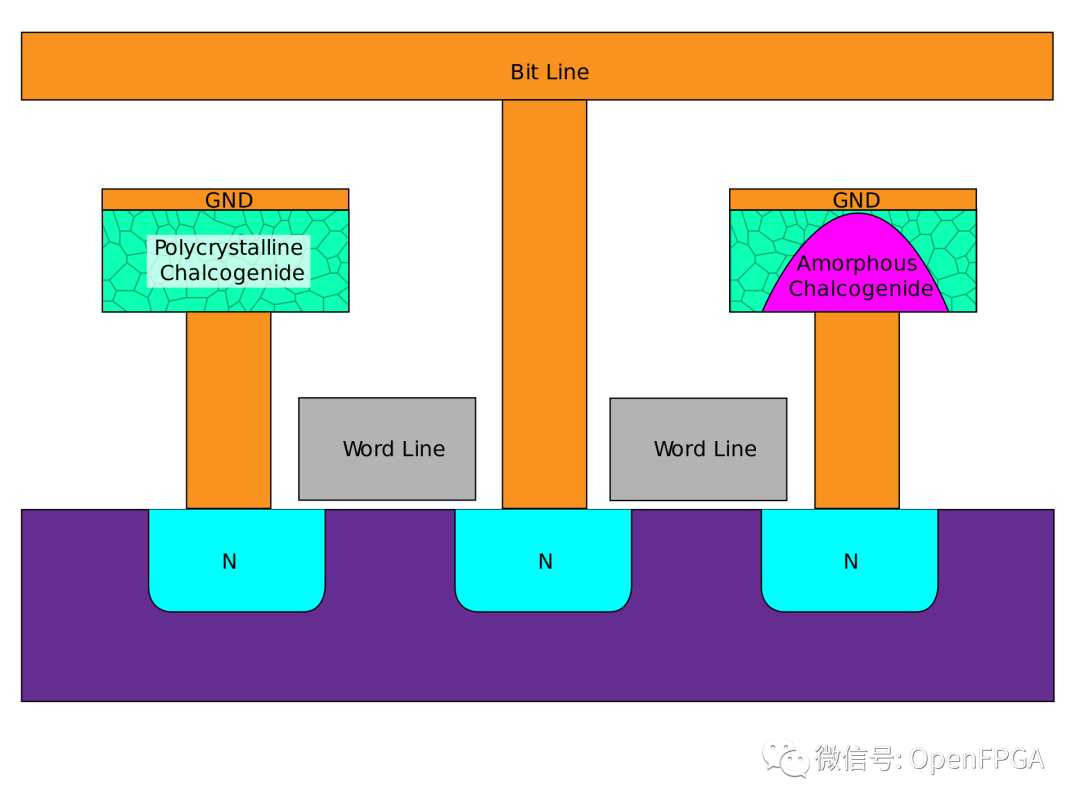

PCM: Phase change memory 相变存储器

PIC: Programmable interrupt controller 可编程中断控制器

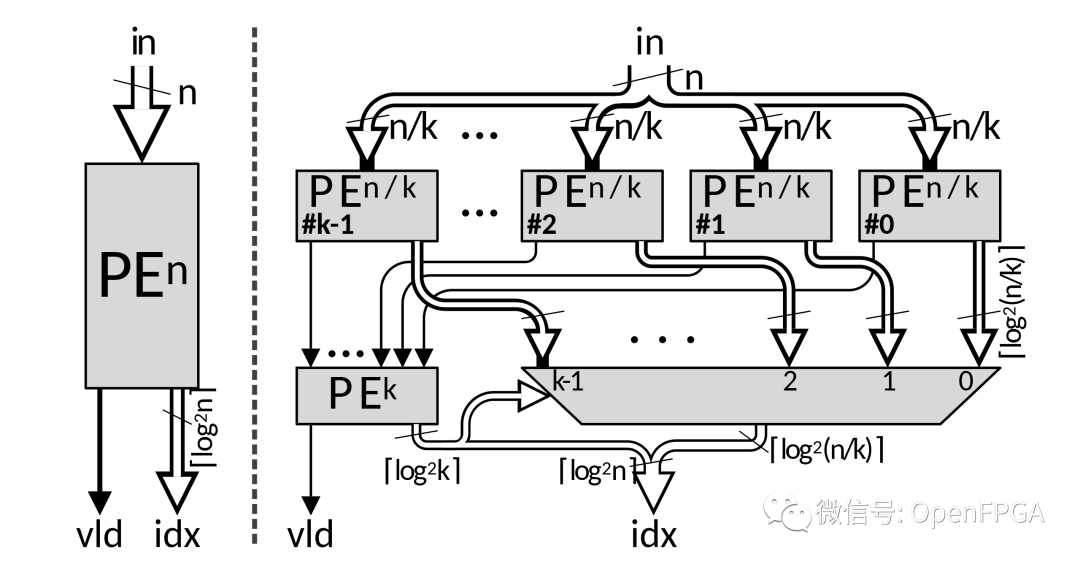

Priority Encoder: A circuit or algorithm that compresses multiple binary inputs into a smaller number of outputs 优先级编码器-将多个二进制输入压缩成较少数量输出的电路或算法

ROM: Read only memory (denser than RAM) 只读存储器(比 RAM 更密集)

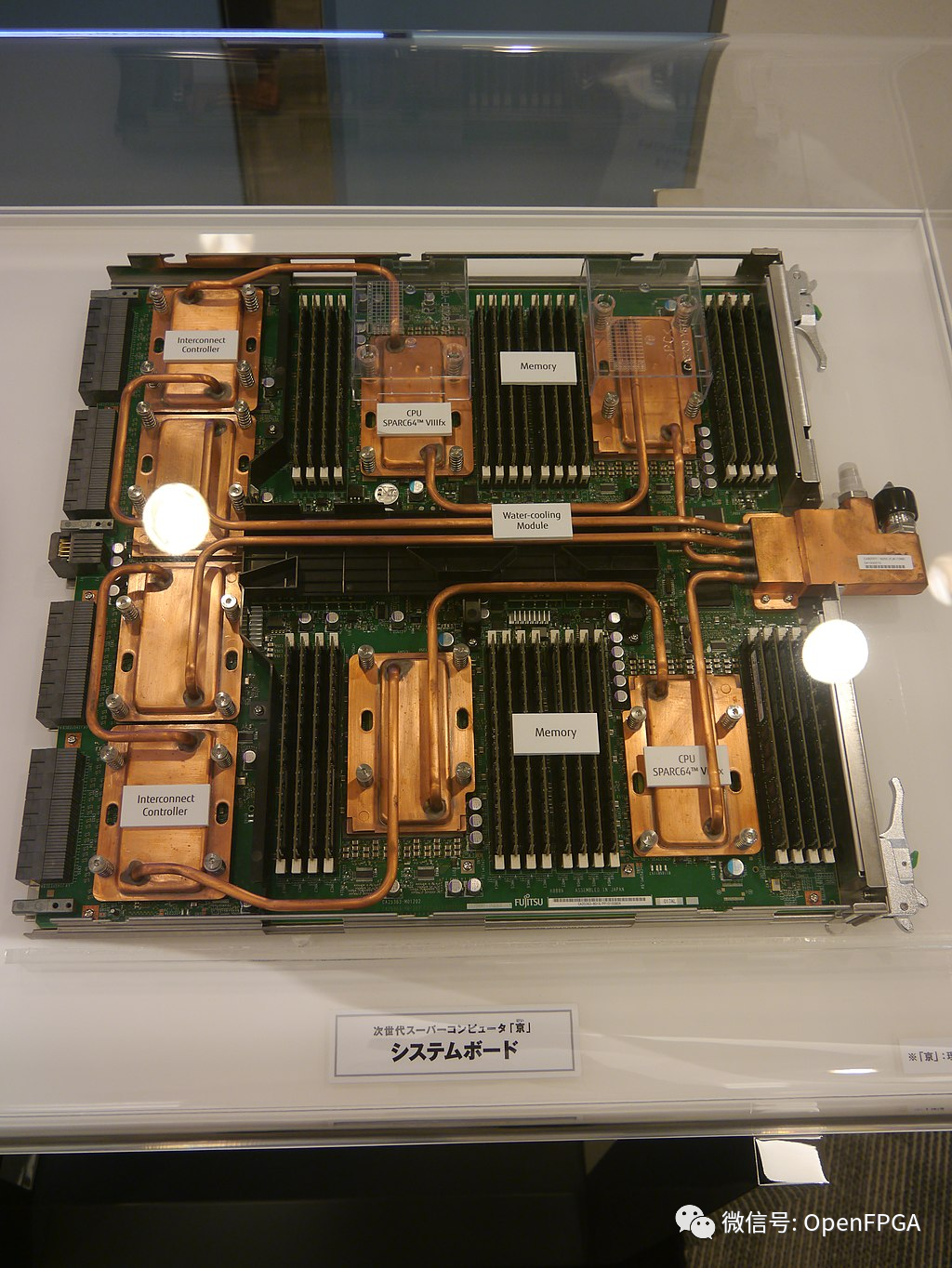

SBC: Single board computers 单板计算机

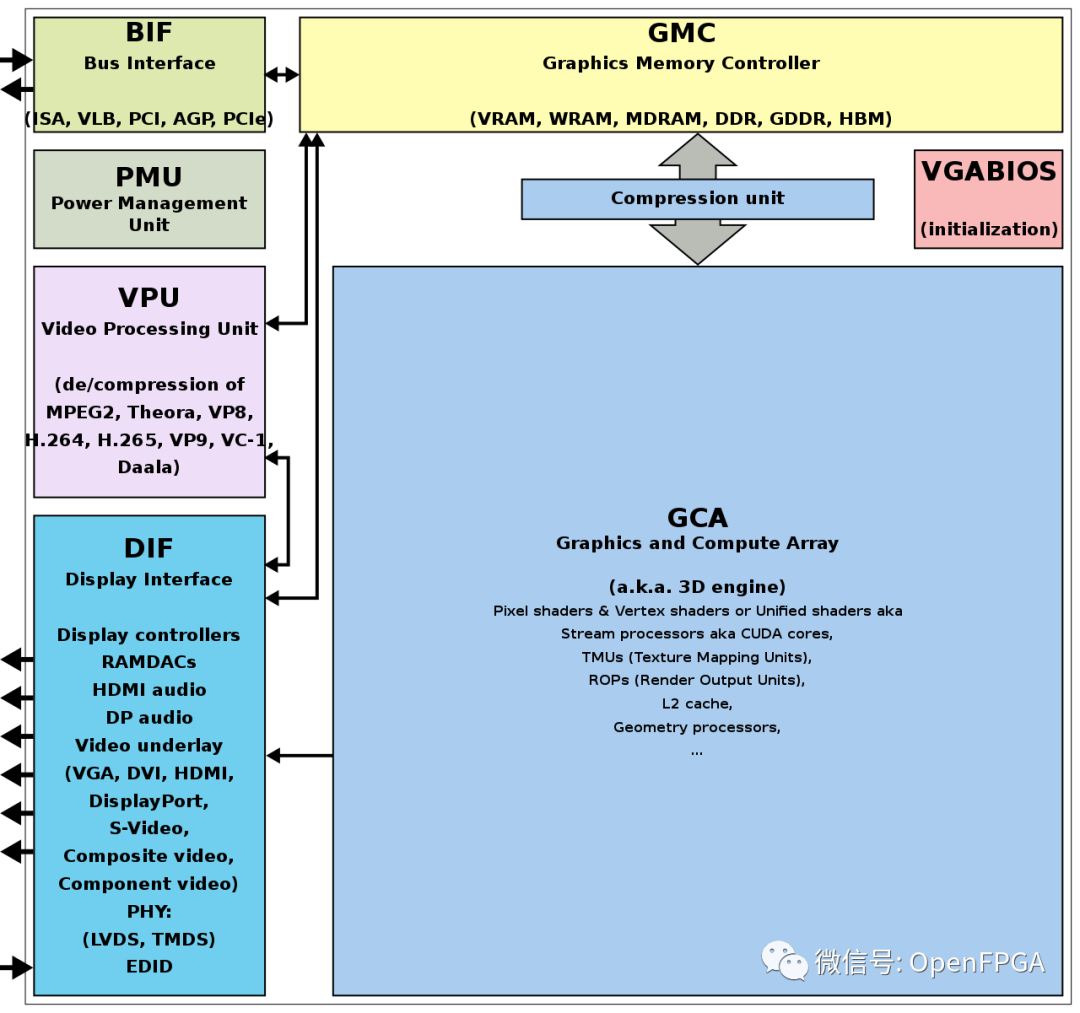

Video codec: Device/program that compresses/decompresses digital video 视频编解码器-压缩/解压缩数字视频的设备/程序

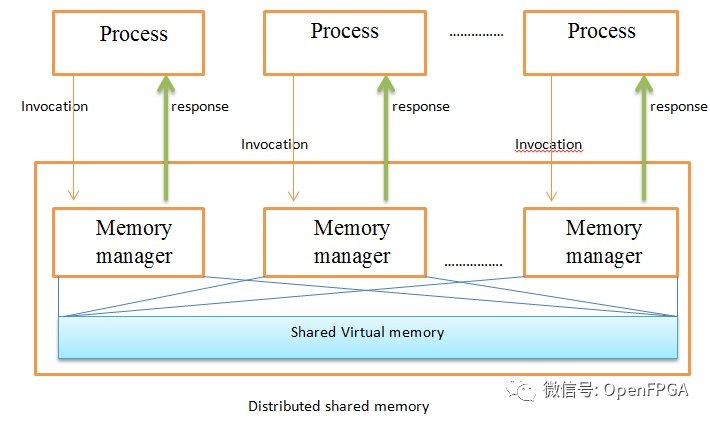

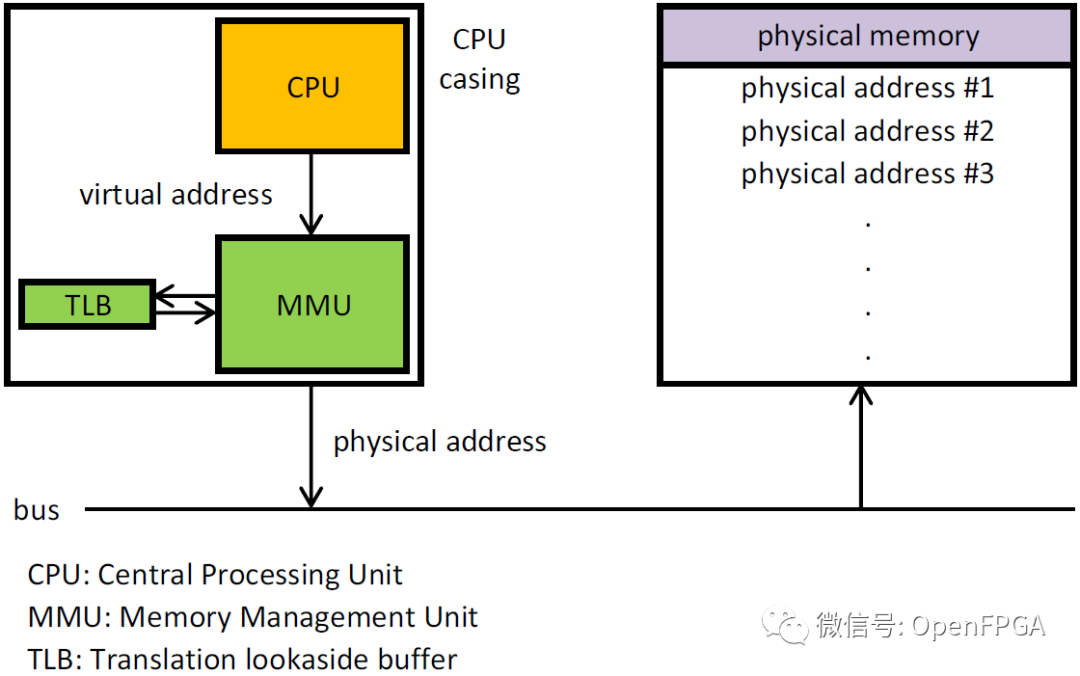

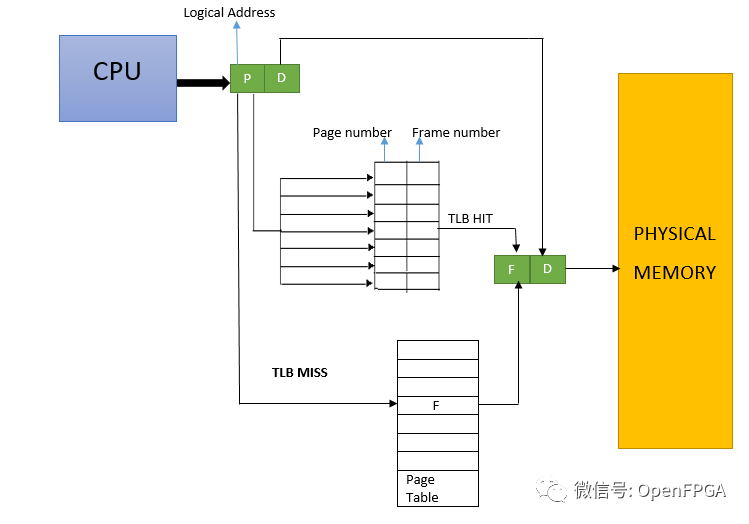

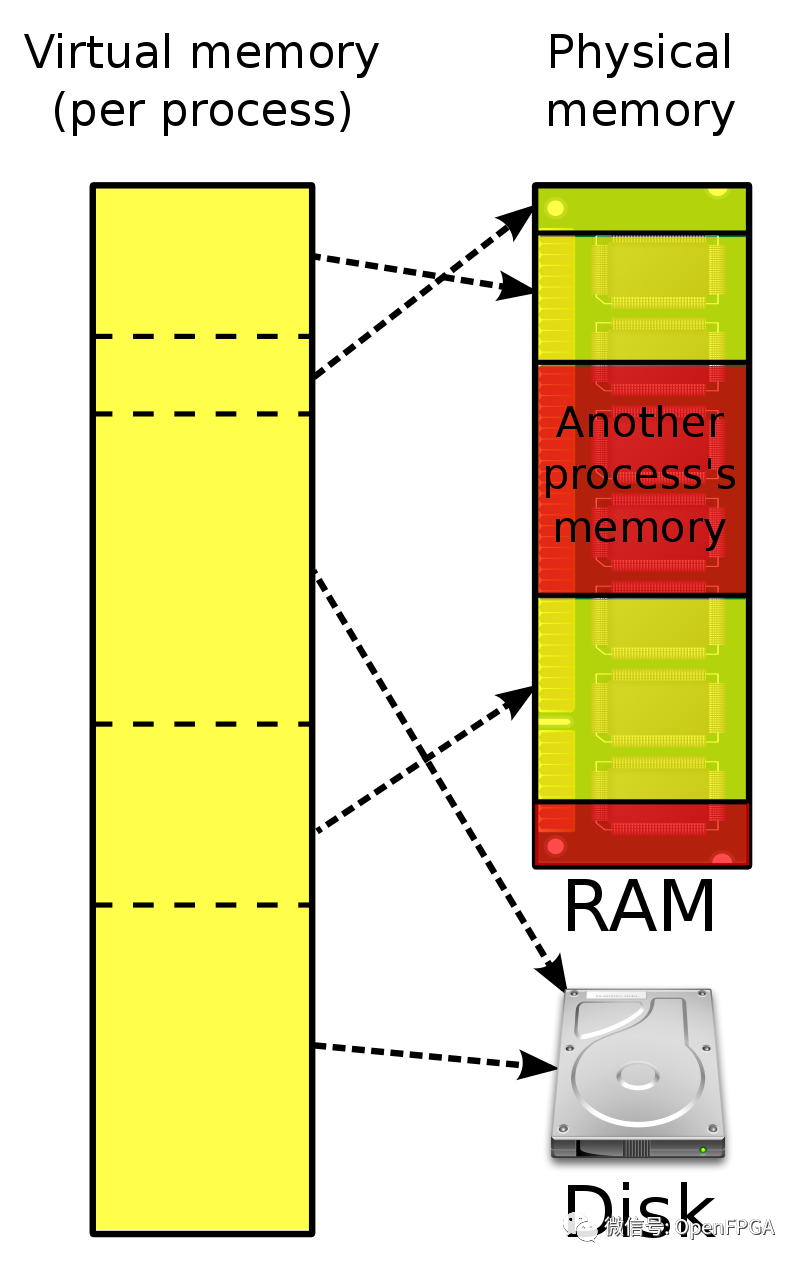

Virtual Memory: The automatic mapping of virtual program addresses to physical addresses 虚拟内存-虚拟程序地址到物理地址的自动映射

VLIW: Very long instruction level parallelism 长的指令级并行性

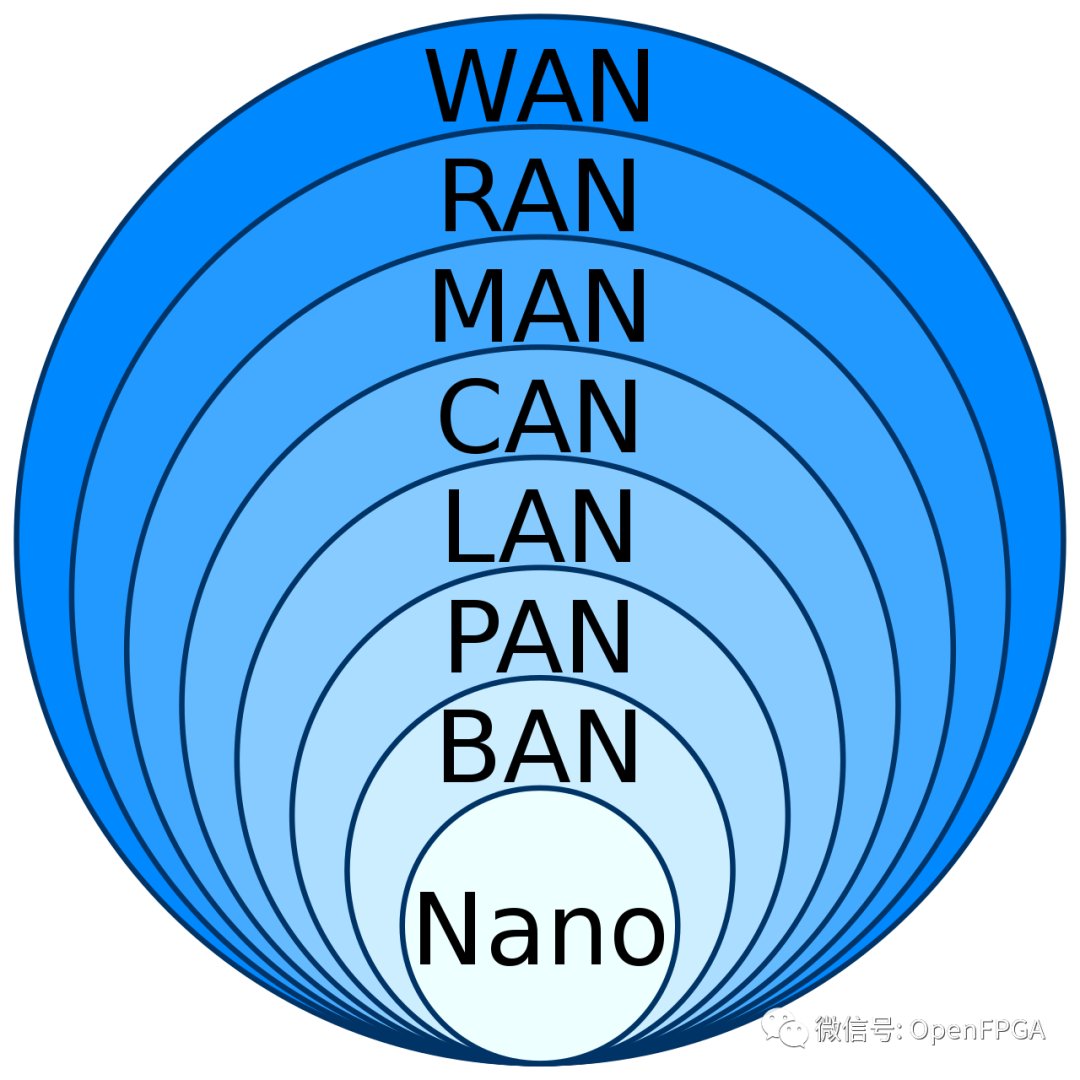

WAN: Wide area network 广域网

ATPG: Automatic test pattern generation 自动测试模式生成

BIST: Built in Self Test 内置自检

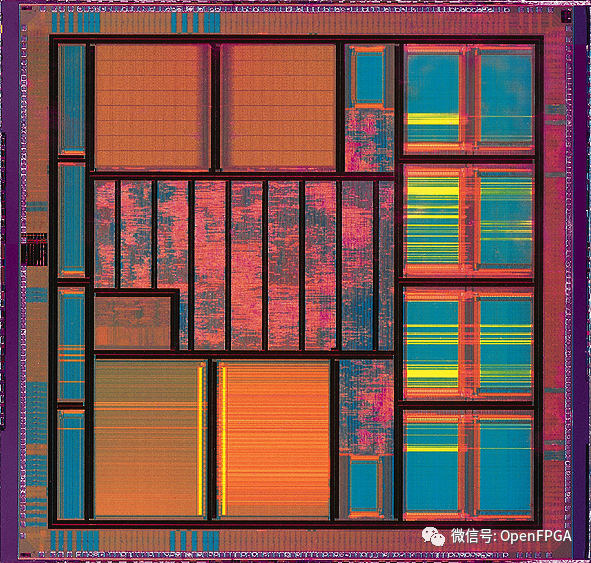

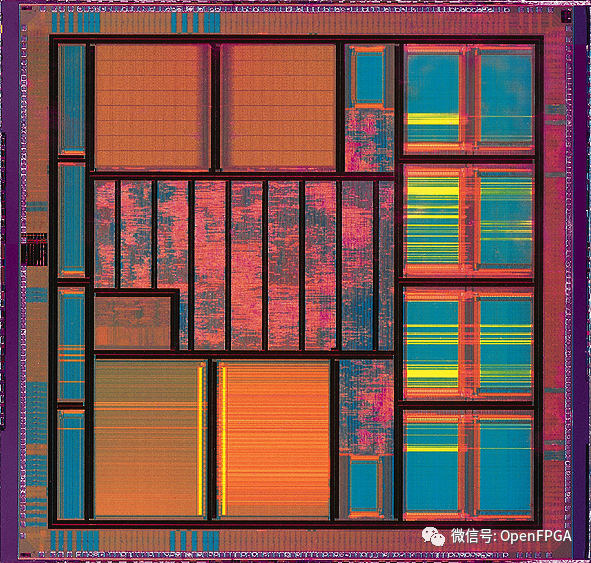

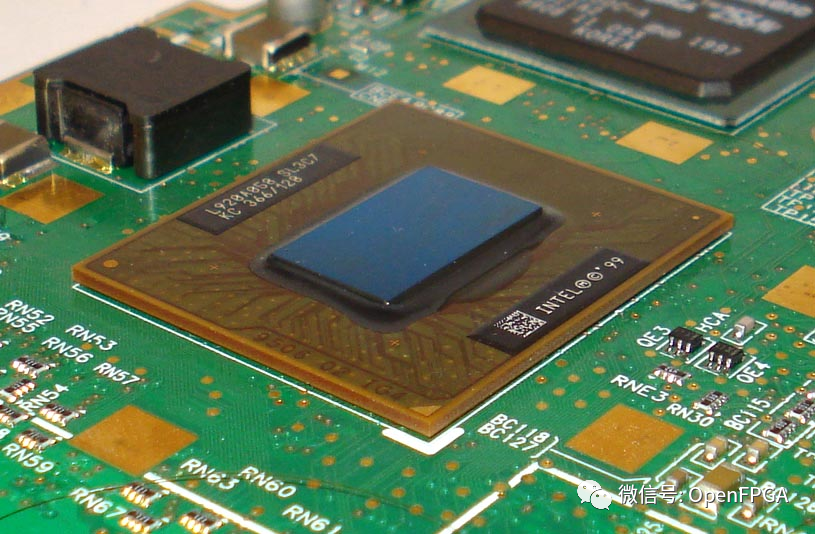

Chip: A set of electronic circuits on one small plate ("chip") of semiconductor material, normally silicon. 芯片

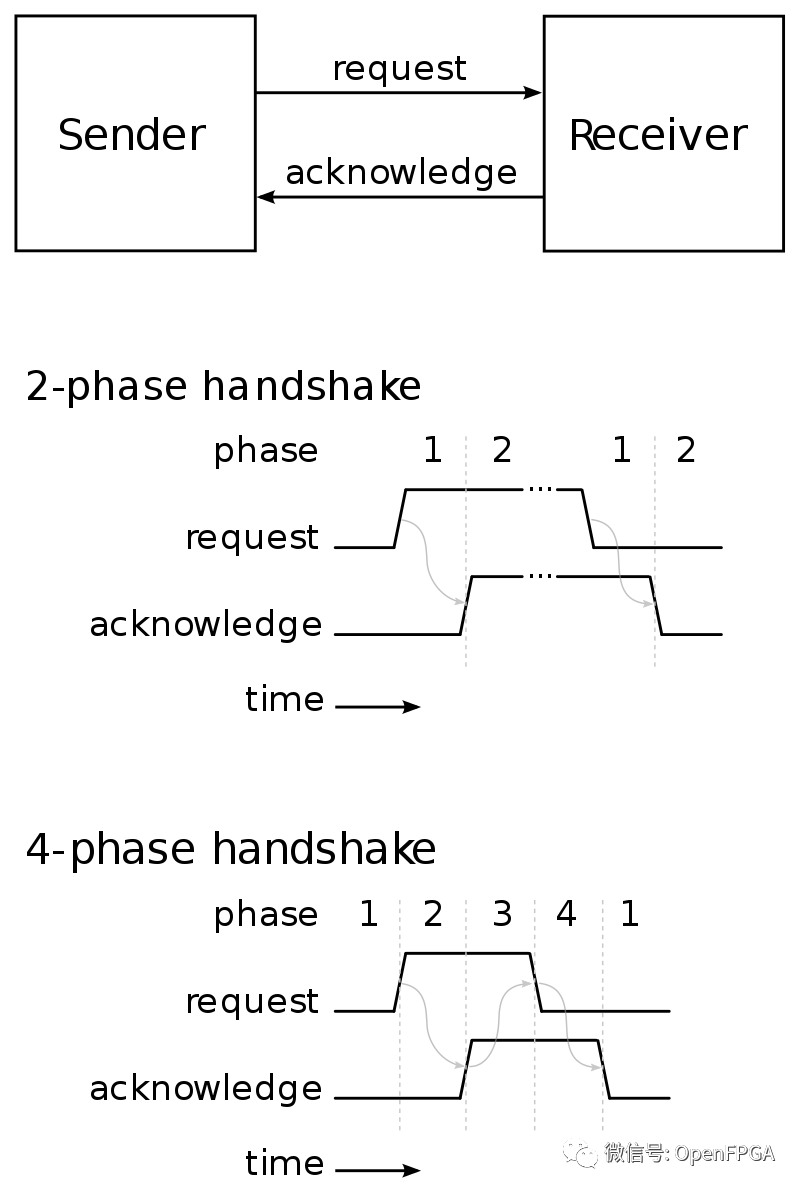

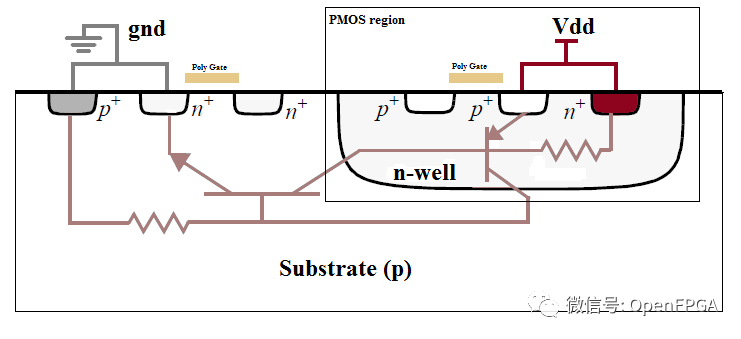

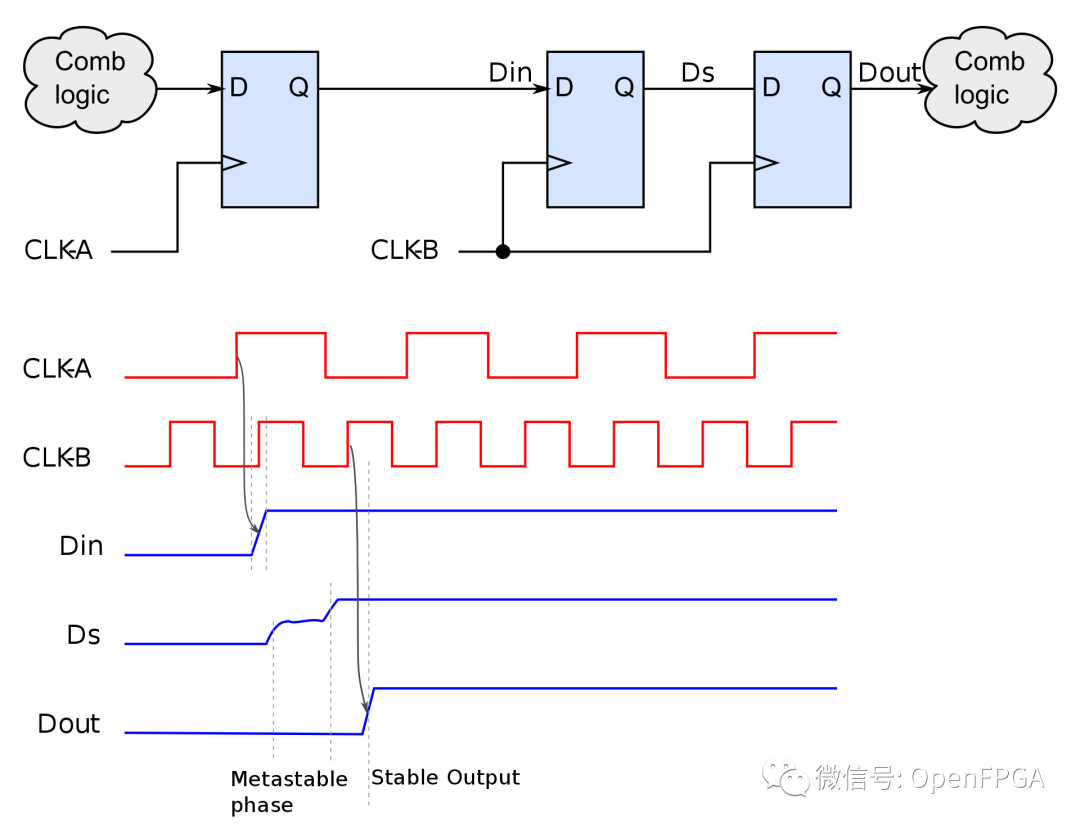

Clock domain crossing: Traversal of signal in synchronous digital ssytem from one clock domain to another.时钟域交叉-同步数字系统中的信号从一个时钟域到另一个时钟域的遍历。

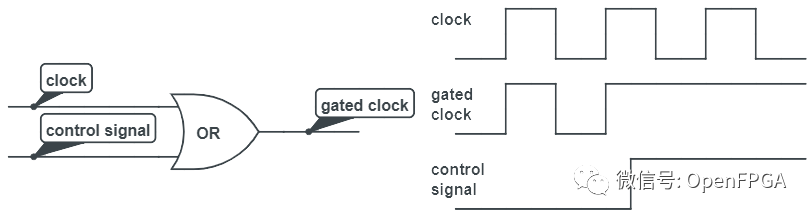

Clock gating: Technique whereby clock in synchronous logic is shut off when idle.门控时钟-同步逻辑中的时钟在空闲时关闭的技术。

CTS: Clock tree synthesis 时钟树合成

Domino logic: Fast clocked logic with reduced capacitive load 具有减少容性负载的快速时钟逻辑

DEF: Design Exchange Format for layout 布局的设计交换格式

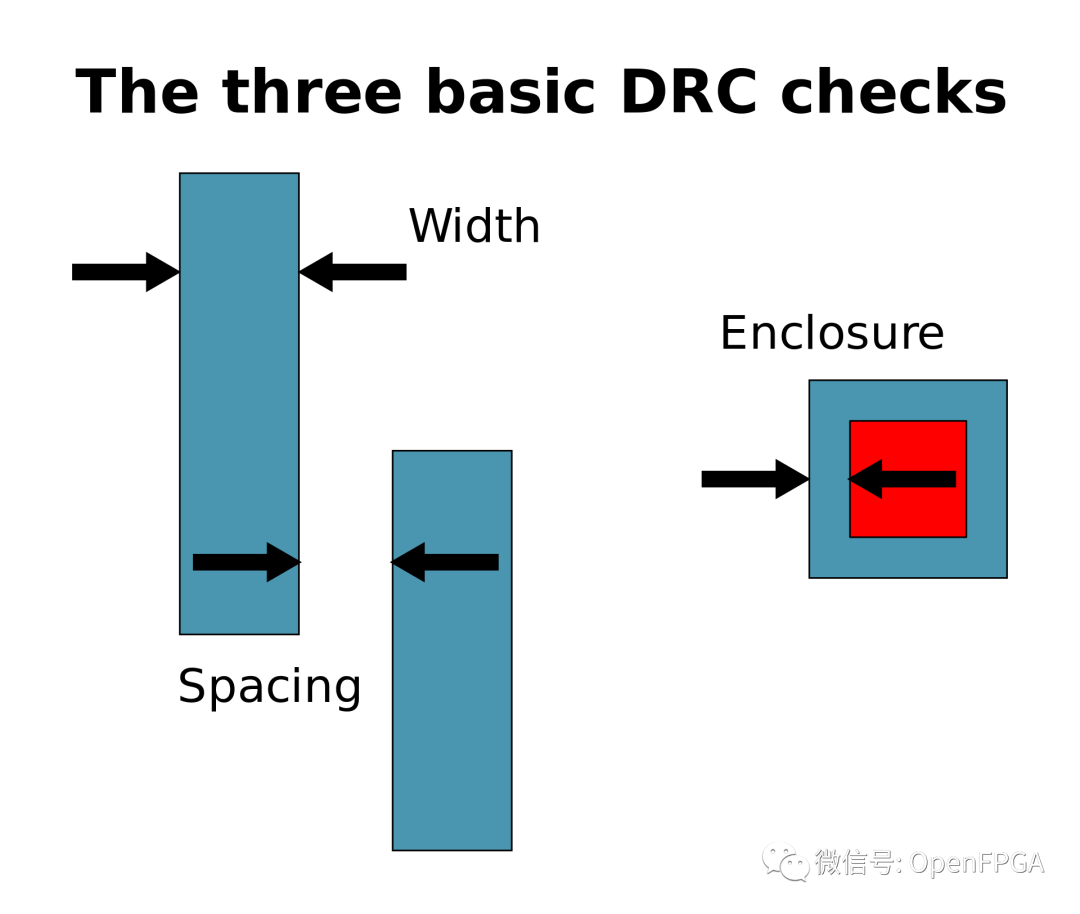

DFM: Extended DRC rules specifying how to make a high yielding design. 扩展的 DRC 规则,指定如何进行高产量设计。

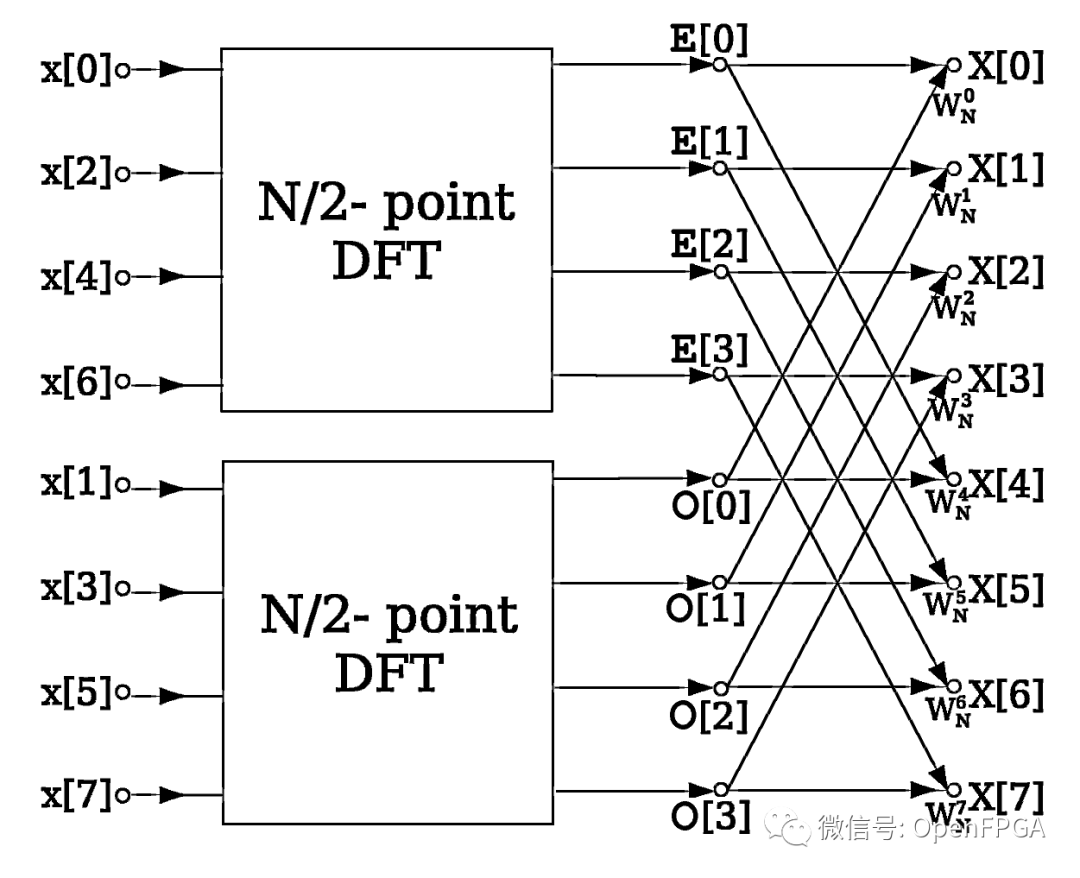

DFT: Design for test可测试性设计或可测试性设计

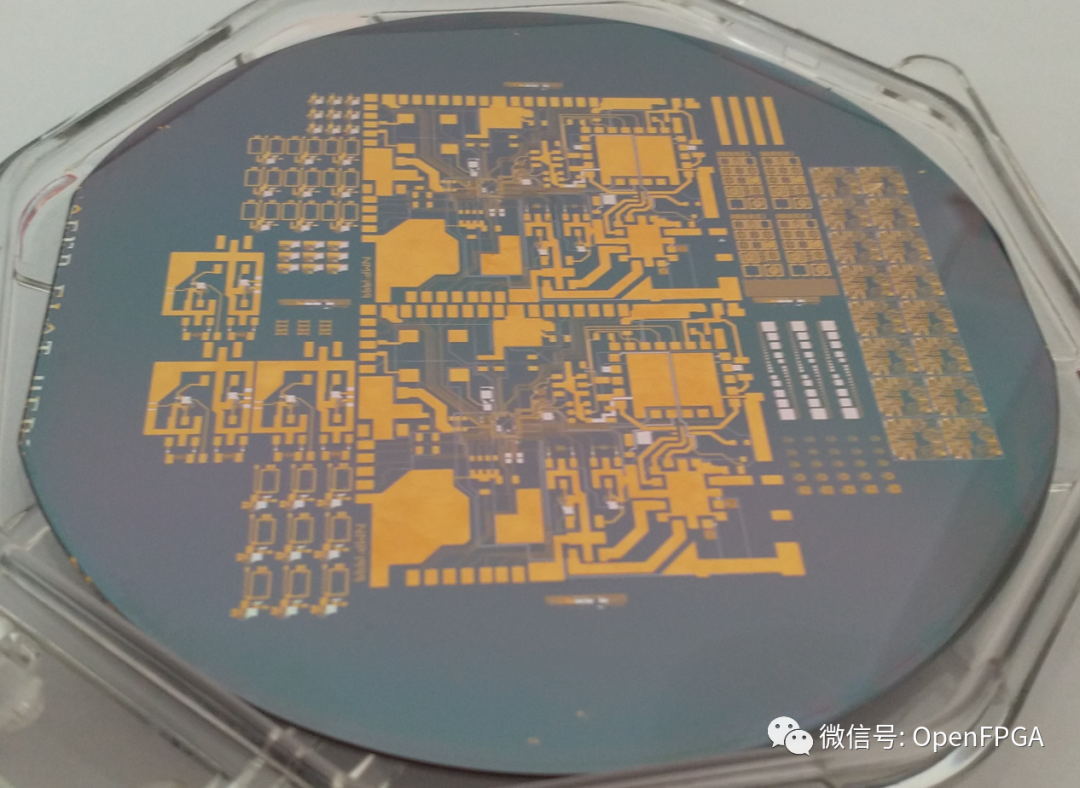

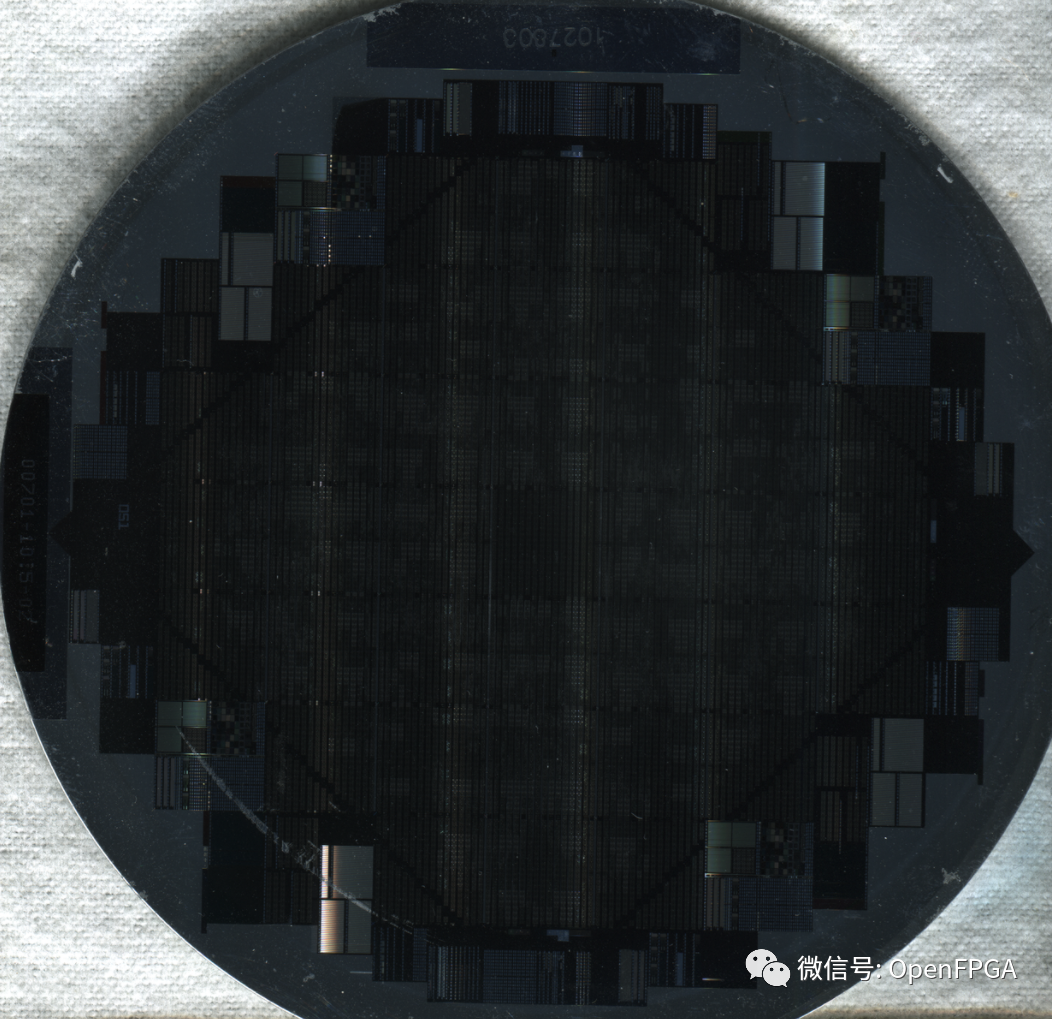

Die: Small block of semiconductor material that can be cut ("diced") from a silicon wafer.可以从硅晶片上切割(“切块”)的小块半导体材料

DV: Design verification is the process of verifying that the logic design conforms to specification. 设计验证是验证逻辑设计是否符合规范的过程

ECO: Engineering change order 工程变更单

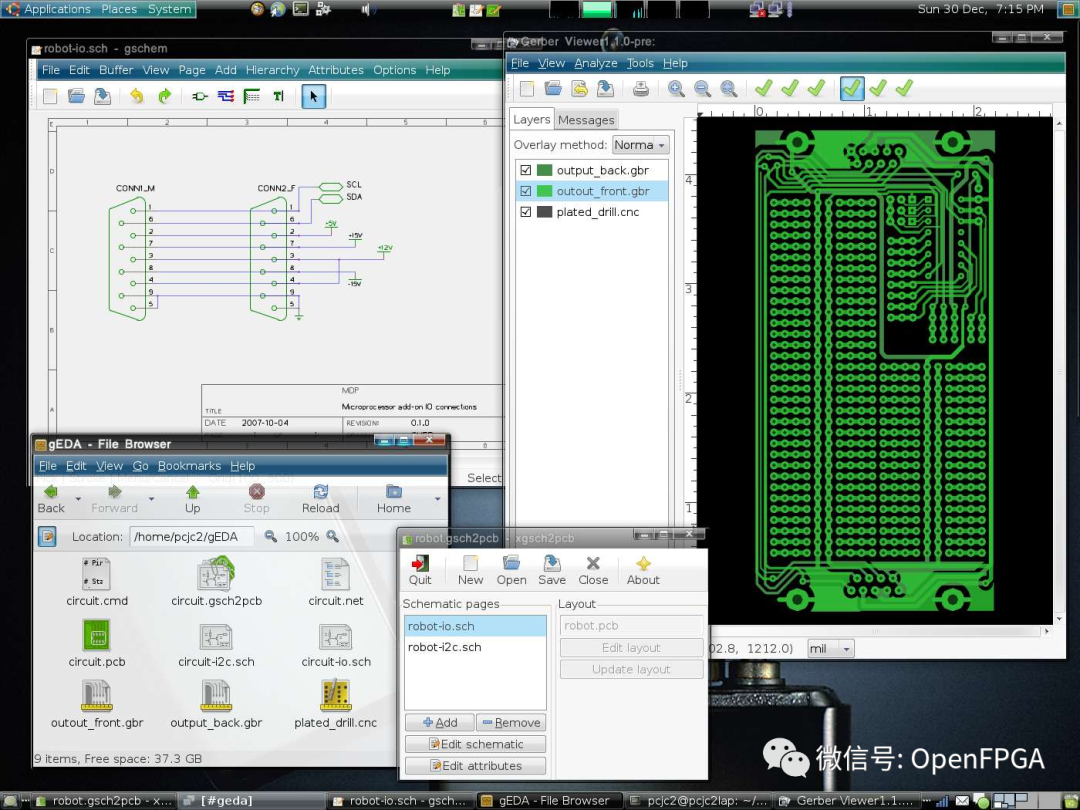

EDA: Electronic Design Automation tools used to enhance chip design productivity. 用于提高芯片设计生产力的电子设计自动化工具

EDA companies: List of EDA companies EDA 公司

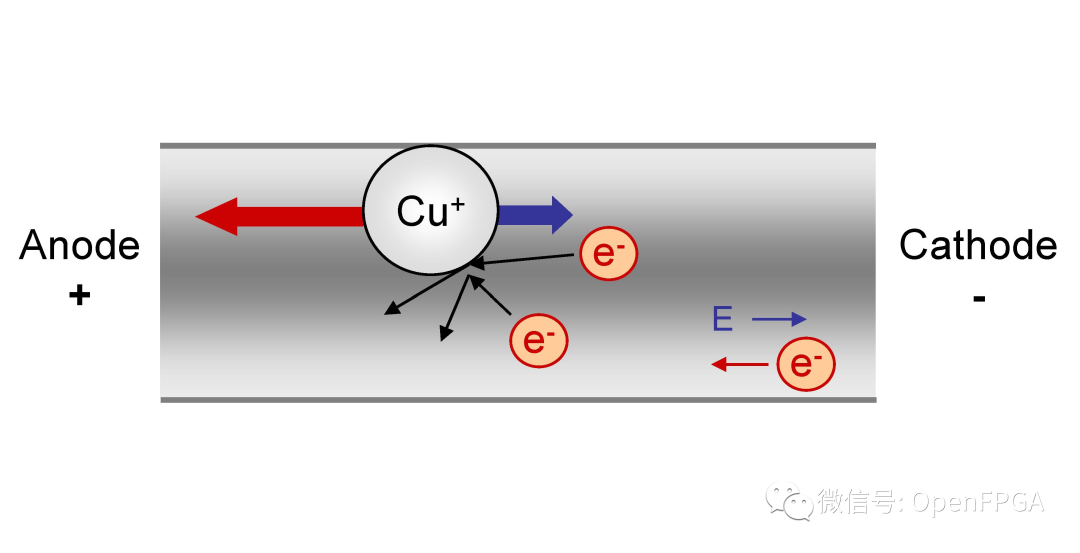

Electromigration: Transport of material caused by the gradual movement of the ions in a conductor. 由导体中的离子逐渐运动引起的物质传输。

Fabless: The design and sale of semiconductor devices while outsourcing the manufacturing to 3rd party. 半导体设备的设计和销售,同时将制造外包给第三方-无晶圆制造是硬件设备和半导体芯片的设计和销售,同时将其制造(或晶圆厂)外包给称为半导体代工厂的专业制造商.

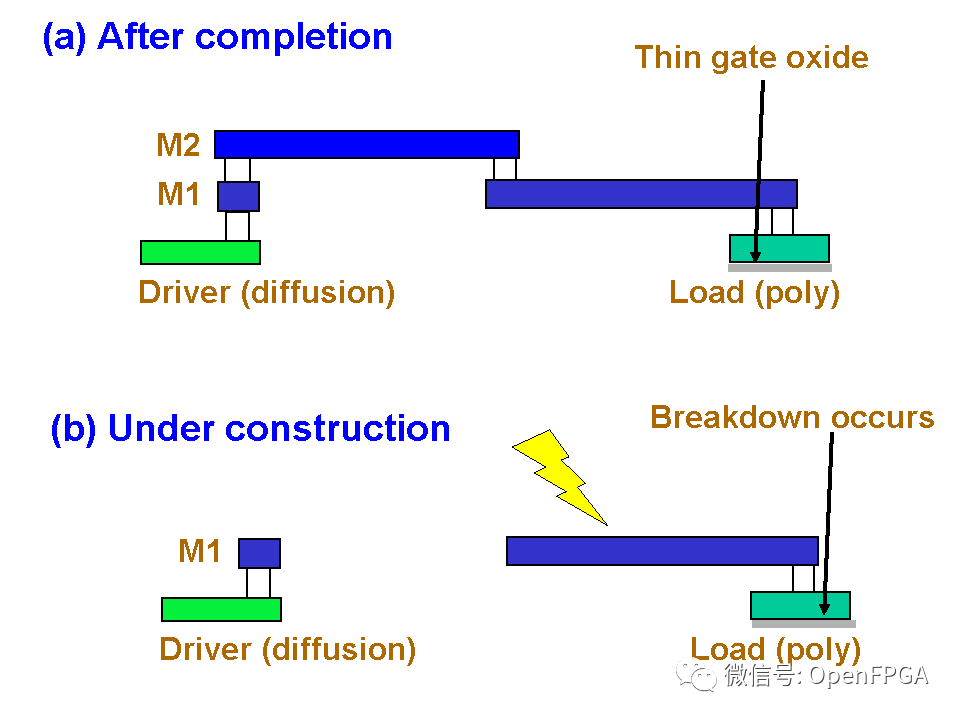

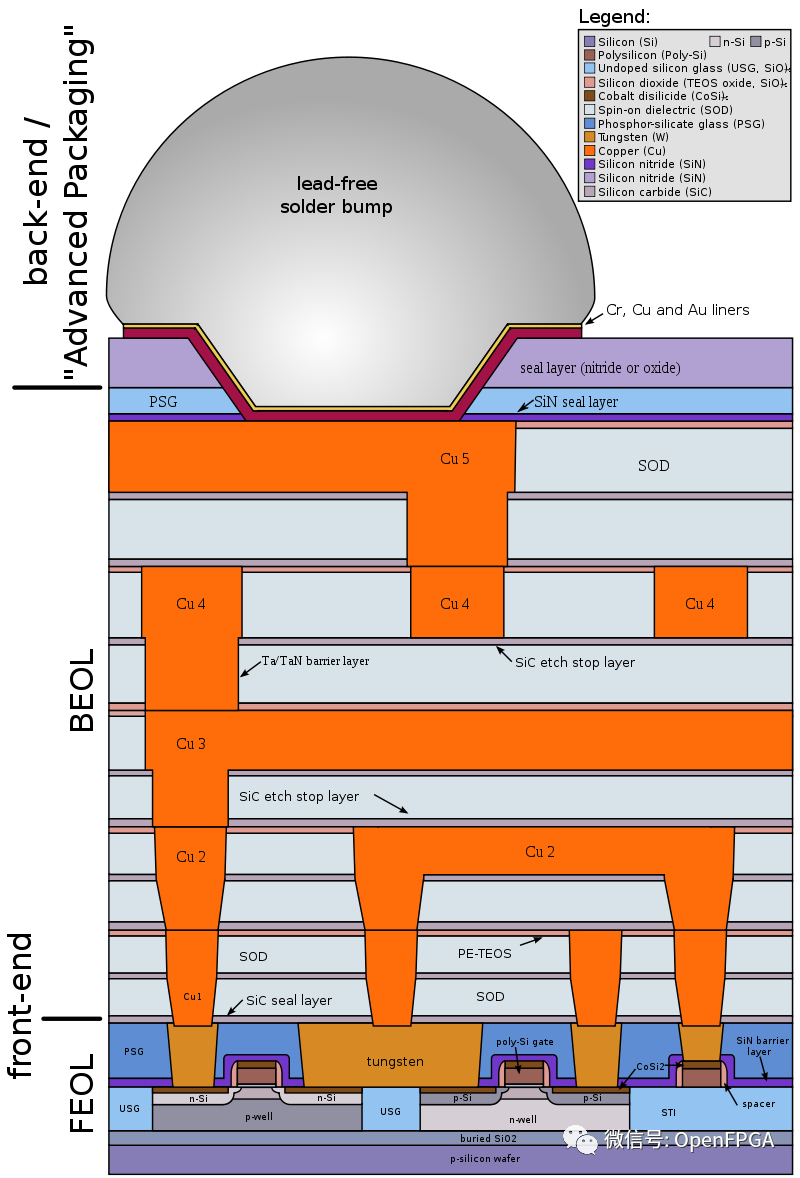

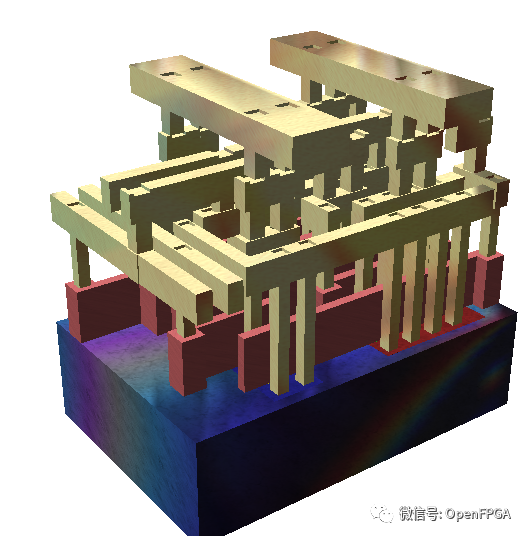

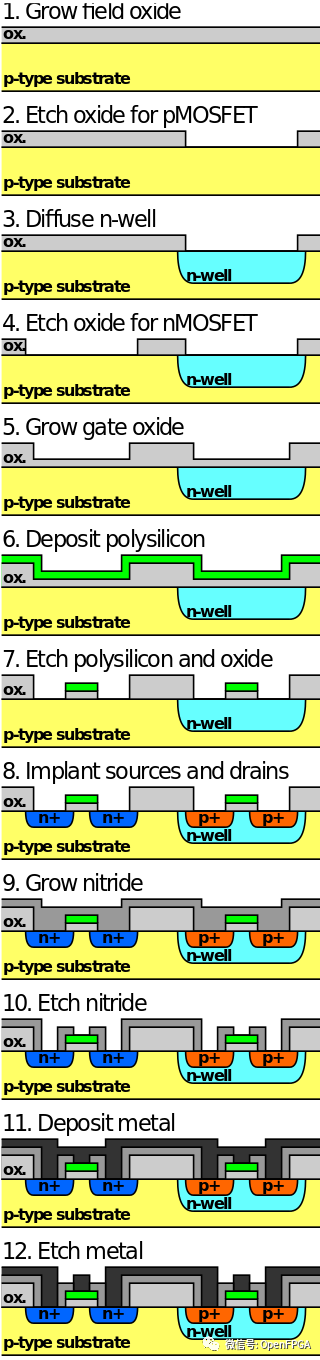

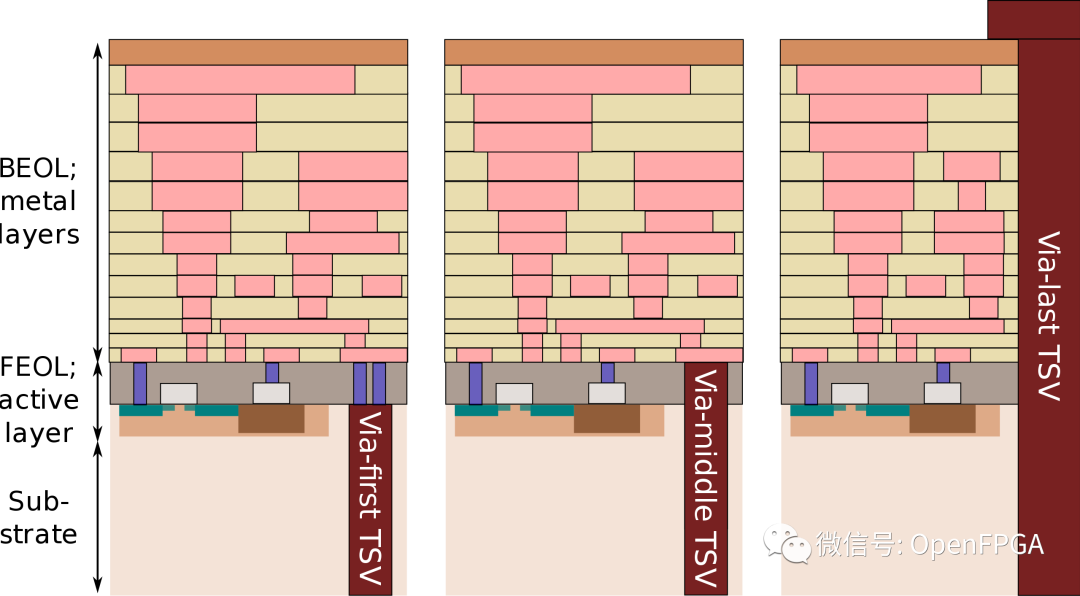

FEOL: Front end of line processing. Includes all chip processing up to but not including metal interconnect layers. 生产线前端处理。包括所有芯片处理,但不包括金属互连层。

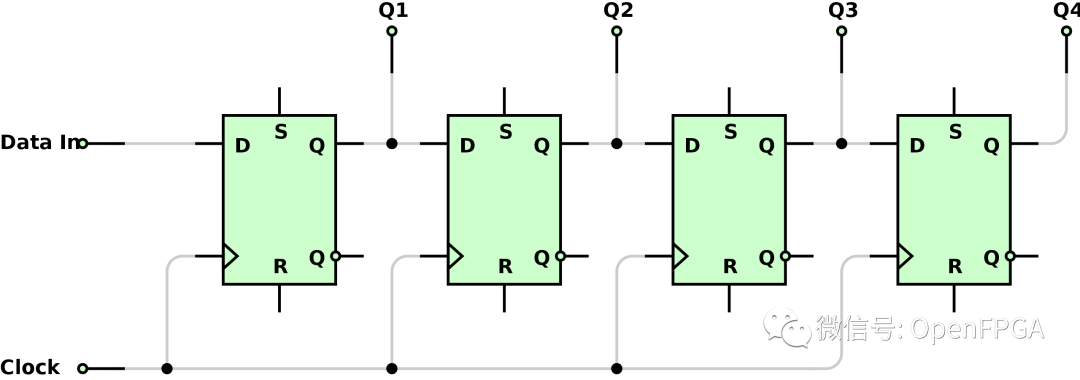

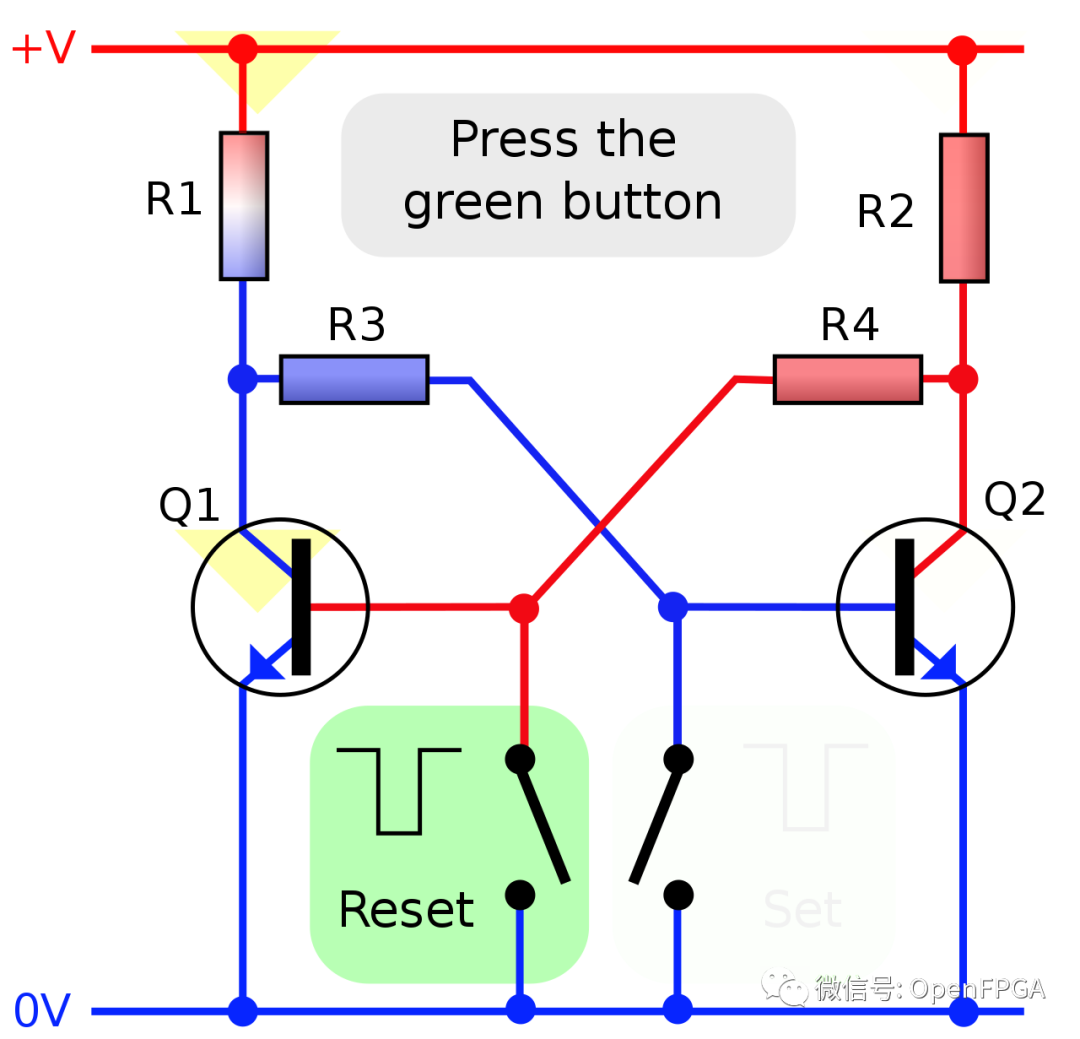

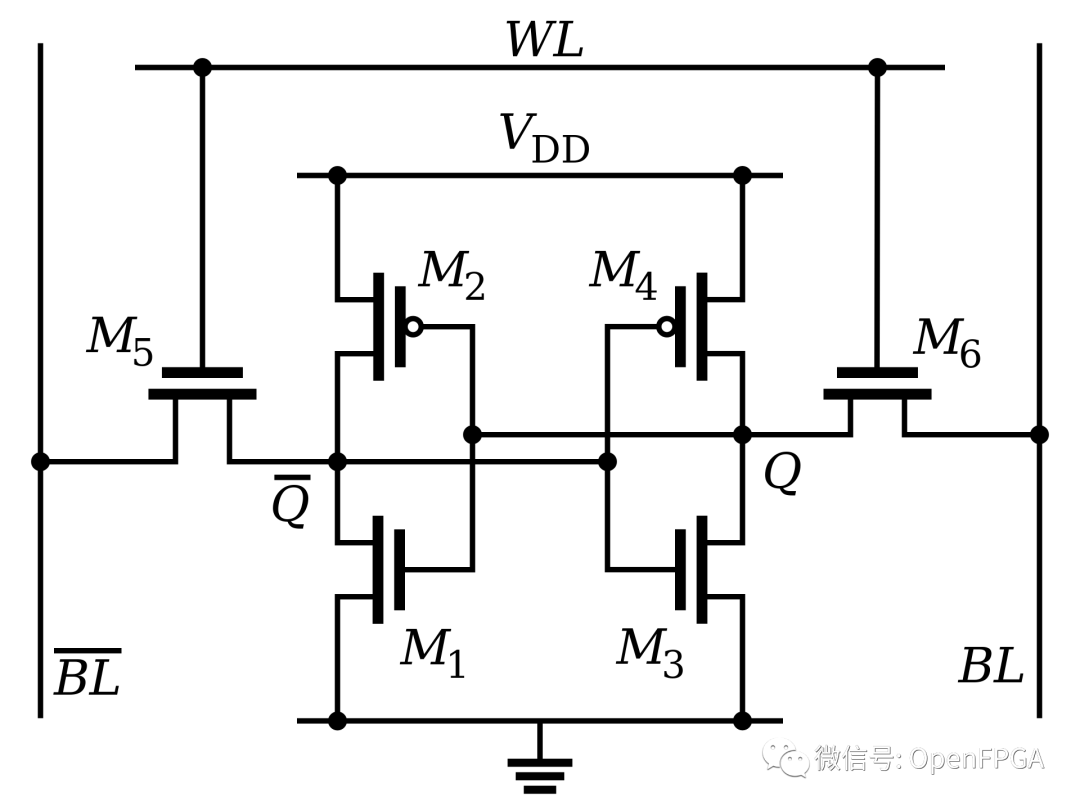

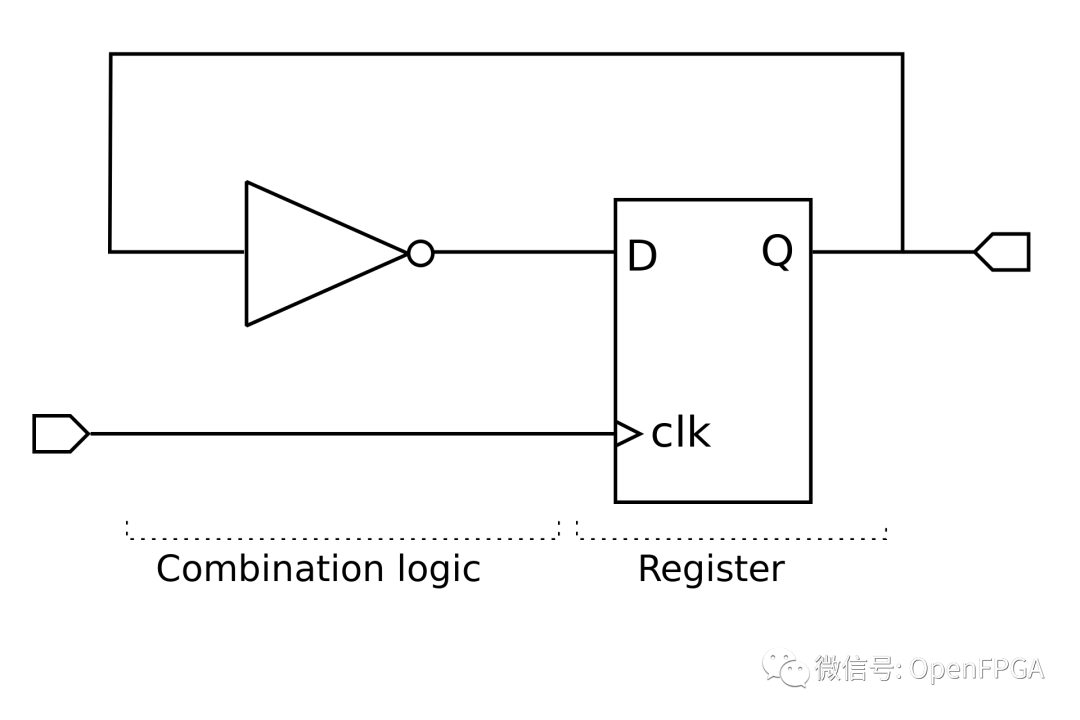

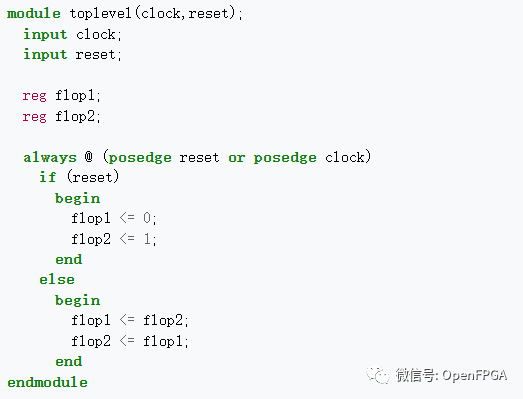

Flip-flop: A clocked circuit that has two stable states and can be used to store state information. 触发器

Foundry: Semiconductor company offering manufacturing services. 提供制造服务的半导体公司

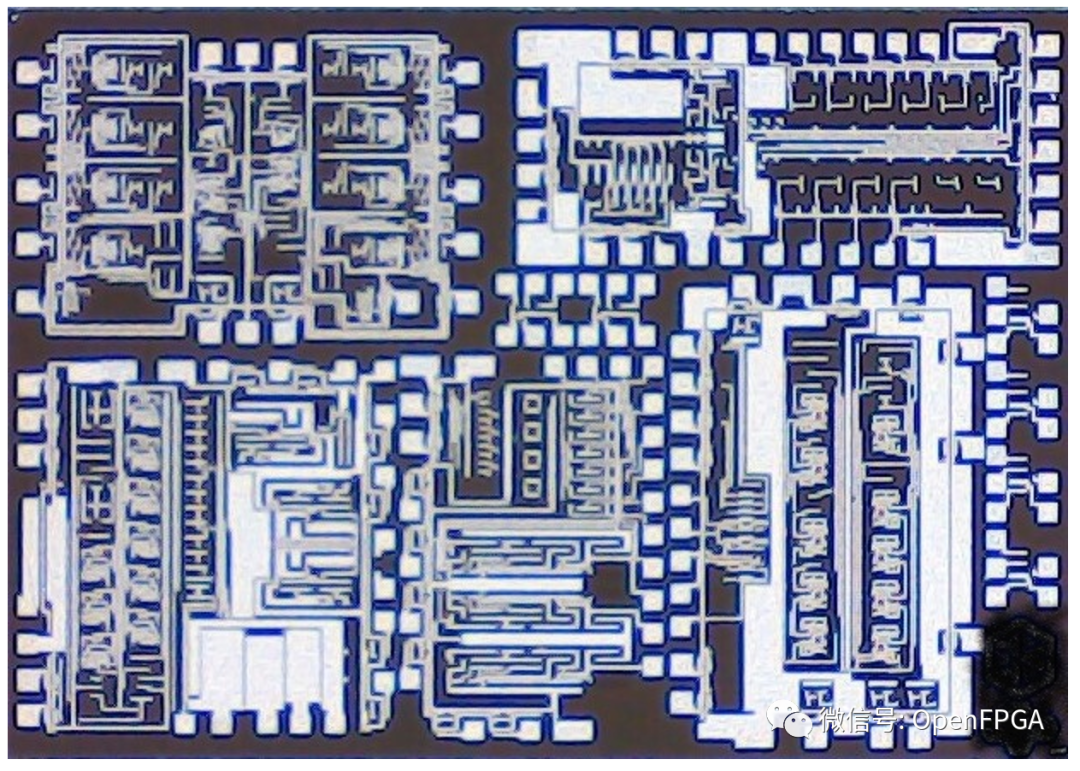

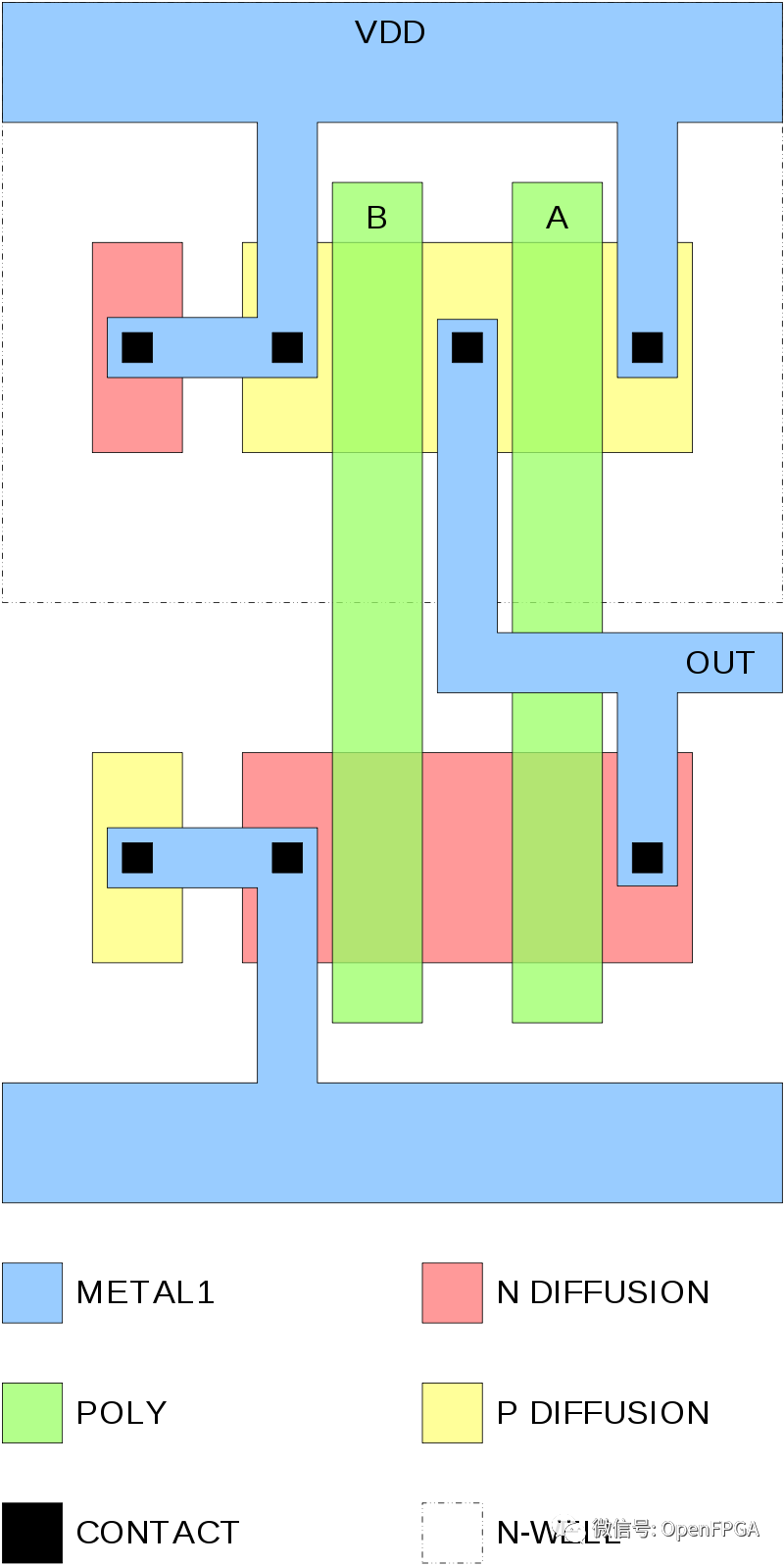

Full custom design: Design methodology involving layout and interconnection of individual transistors. 完全定制设计-涉及各个晶体管的布局和互连的设计方法

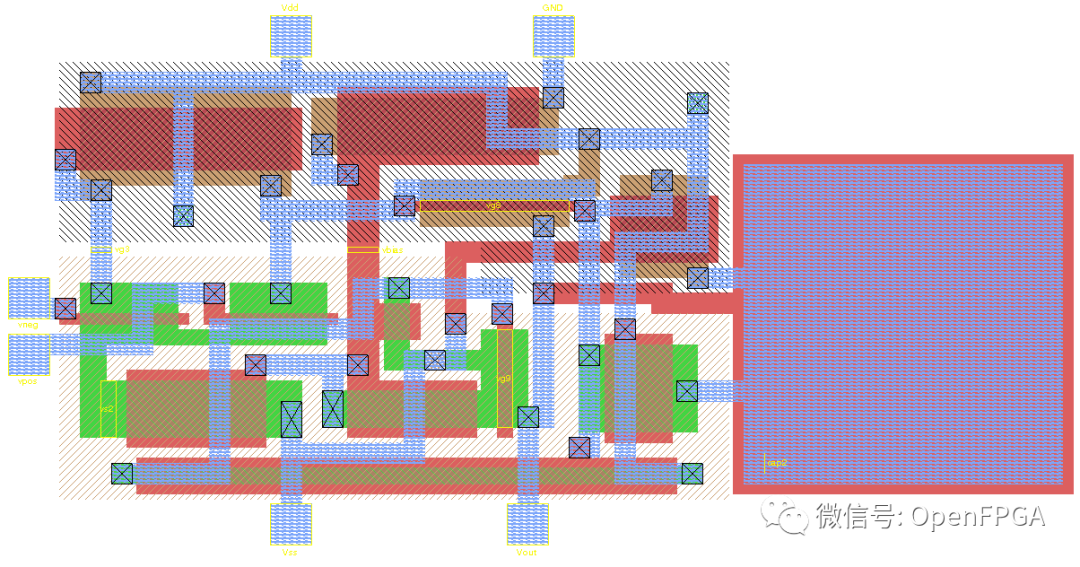

GDSII: Binary format of design database sent to foundry. 发送制造厂的设计数据库的二进制格式

IP: Semiconductor reusable design blocks containing author's Intellectual Property. 含作者知识产权的半导体可重复使用设计块

IP Vendors: List of commercial semiconductor IP vendors. IP 供应商

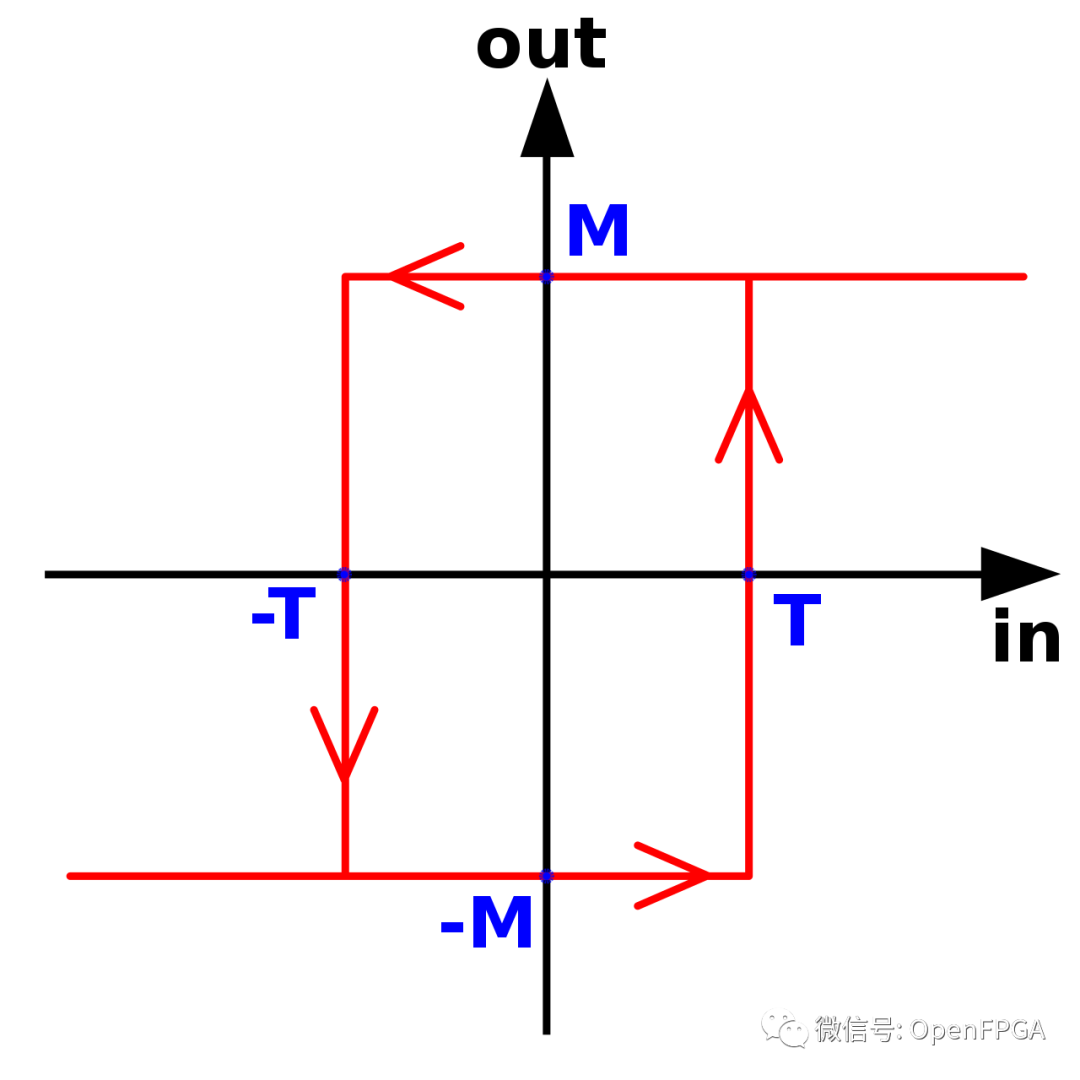

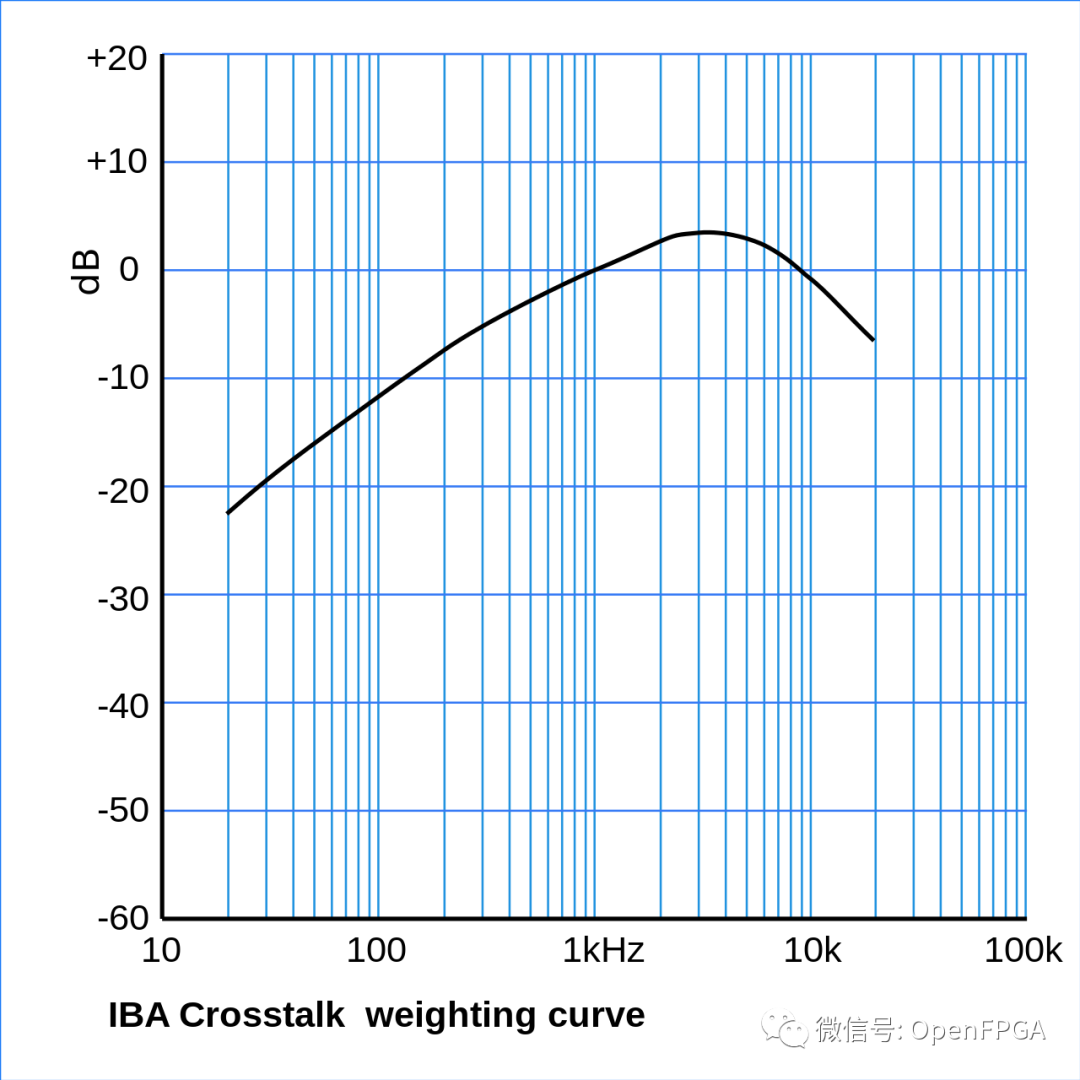

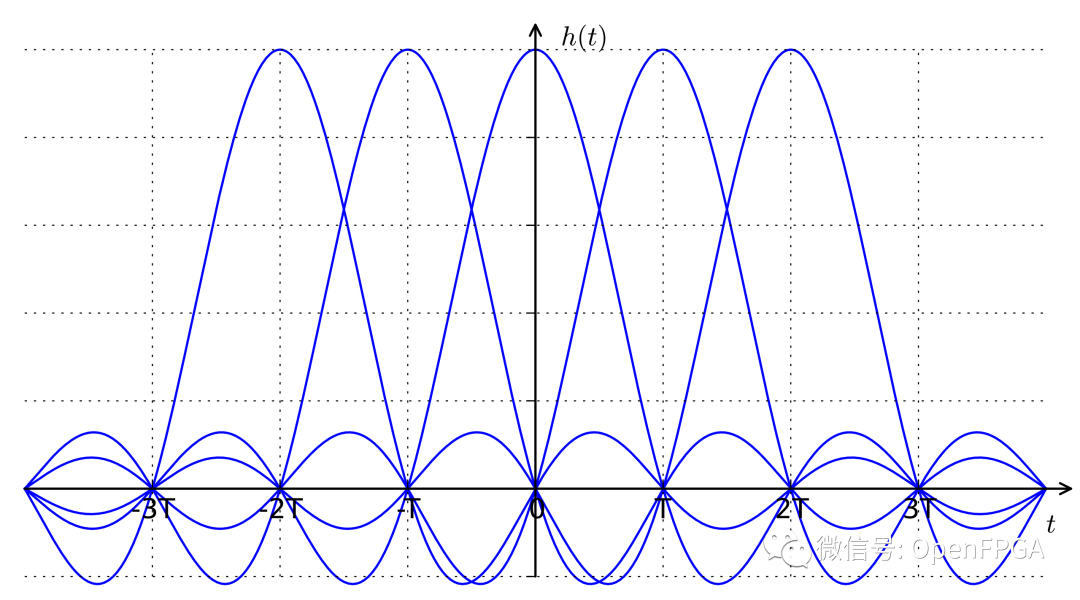

ISI: Intersymbol interference 符号间干扰( ISI ) 是一种信号失真形式,其中一个符号会干扰后续符号

LEF: Standard Cell Library Exchange Format layout.标准单元库交换格式布局。

Logical Effort: Technique used to normalize (and optimize) digital circuits speed paths. Logical Effort是Ivan Sutherland和Bob Sproull在 1991 年创造的一个术语,是一种用于估计CMOS电路延迟的简单技术

LVS: Layout Versus Schematic software checks that the layout is identical to the netlist.LVS : Layout Versus Schematic 软件检查布局是否与网表相同。

Mask Works: Copyright law dedicated to 2D and 3D integrated circuit "layouts". “掩模工作”-专门针对 2D 和 3D 集成电路“布局”的版权法。

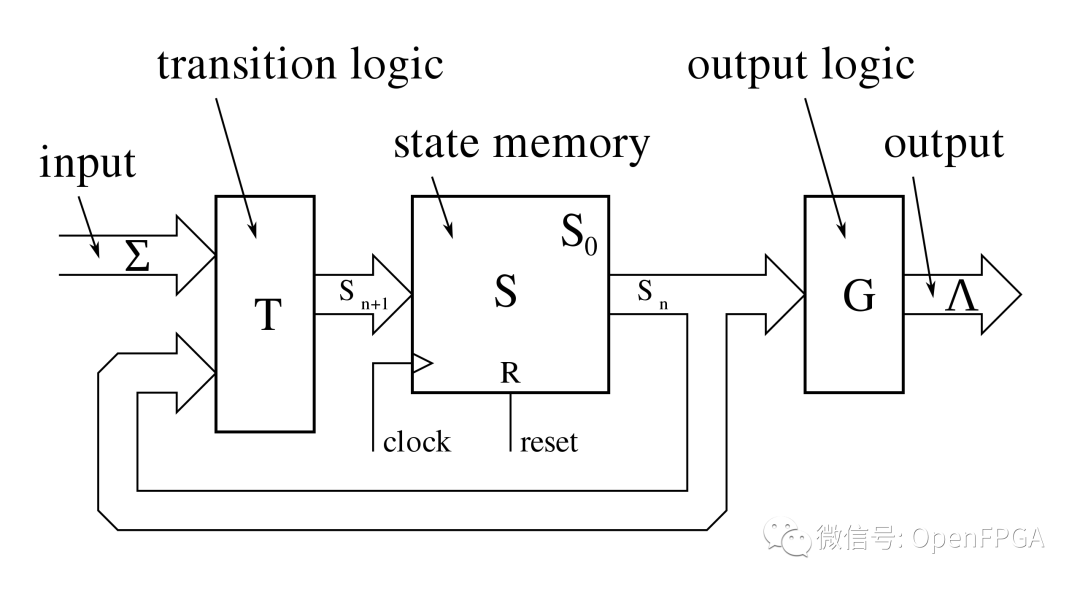

Mealy machine: A finite state machine whose outputs depend on current state and the current inputs. 一种有限状态机,其输出取决于当前状态和当前输入。

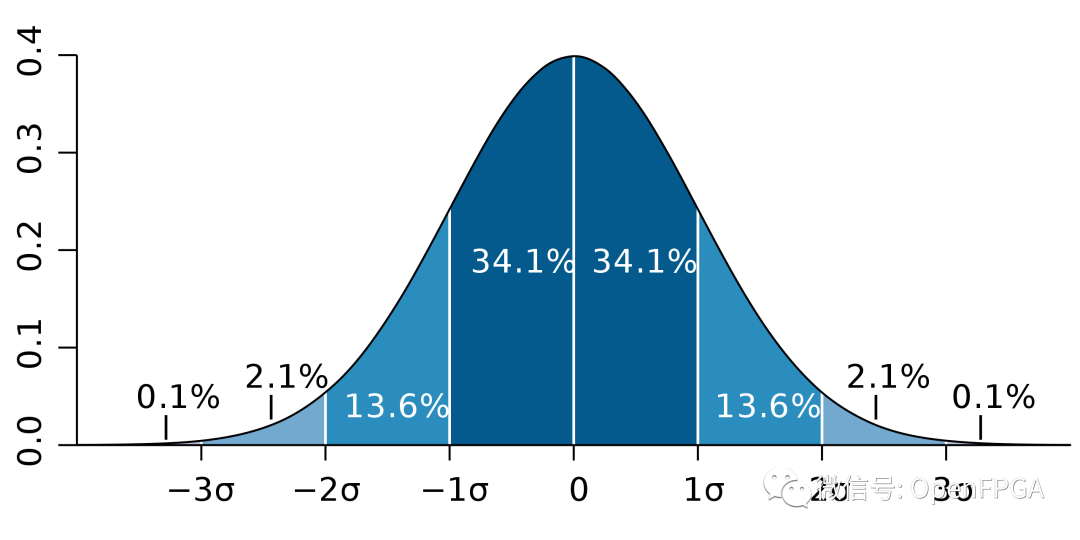

Metastability: Ability of a digital electronic system to persist for an unbounded time in an unstable equilibrium. 数字电子系统在不稳定平衡中持续无限时间的能力。

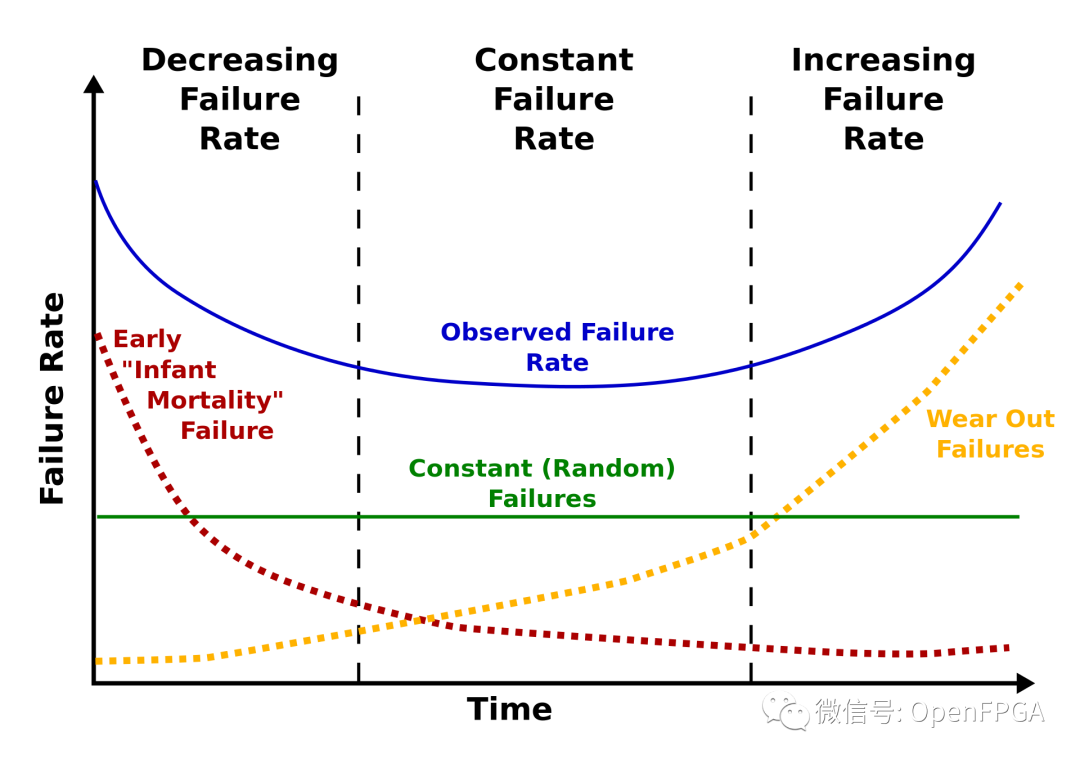

MTBF: Mean time between failures. 平均故障间隔时间。

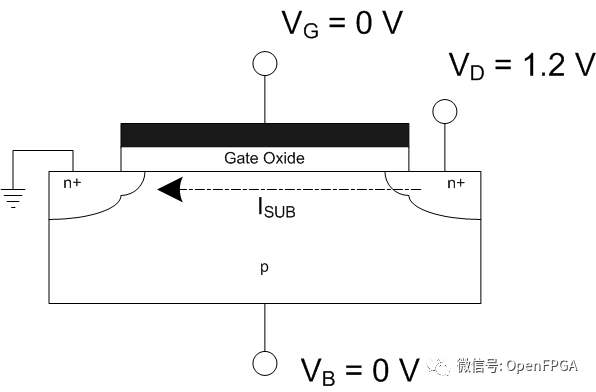

Multi-threshold CMOS: CMOS technology with multiple transistor types with different threshold voltages. 多阈值 CMOS:具有不同阈值电压的多种晶体管类型的 CMOS 技术。

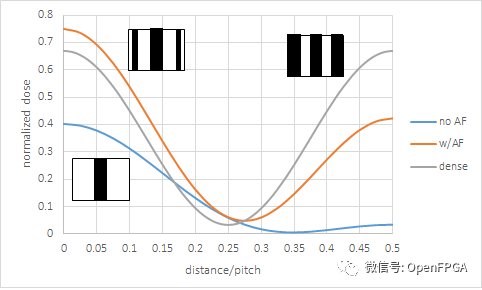

Optical proximity correction: Technique used to compensate for semiconductor diffraction/process effects. 光学邻近校正-用于补偿半导体衍射/工艺效应的技术。

PDK: Process design kits consisting of a minimum set of files needed to design in a specific process. 流程设计工具包,包含在特定流程中进行设计所需的最少文件集

Power gating: Technique used to reduce leakage/standby power by shutting of the supply to the circuit. 电源门控:用于通过关闭电路电源来减少泄漏/待机功率的技术

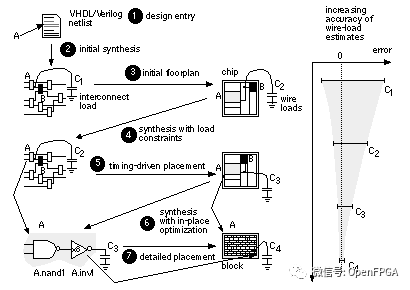

P&R: Automated Place and Route of a circuit using an EDA tool. 使用 EDA 工具自动布局和布线电路

PVT Corners: Represents the extreme process, voltage, temperature that could occur in a given semiconductor process. 表示给定半导体工艺中可能出现的极端工艺、电压、温度

Radiation Hardening: Act of making devices resistant to damage caused by ionizing radiation. 辐射硬化是使电子元件和电路能够抵抗由高水平电离辐射(粒子辐射和高能电磁辐射)引起的损坏或故障的过程

RTL: Design abstraction for digital circuit design. 寄存器传输级( RTL ) 是一种设计抽象,它根据硬件寄存器之间的数字信号(数据)流以及对这些信号执行 的逻辑操作对同步 数字电路进行建模

Setup time: Minimum time synchronous input should be ready before clock event. 建立时间-最小时间同步输入应在时钟事件之前准备好

SEU: Change of state caused by one single ionizing particle (ions, electrons, photons...). 由单个电离粒子(离子、电子、光子......)引起的状态变化

Signoff: The final approval that the design is ready to be sent to foundry for manufacturing. signoff(也写为sign-off )检查是设计在流片之前必须通过的一系列验证步骤的总称

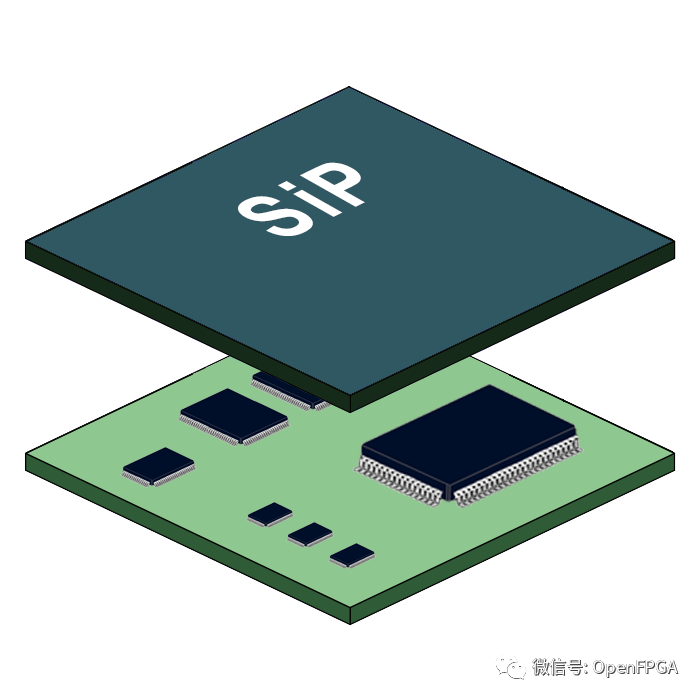

SOC: System On Chip 片上系统

Spice: Open source analog electronic circuit simulator. 开源模拟电子电路模拟器

STA: Method of computing the expected timing of a digital circuit without requiring full circuit simulation. 静态时序分析(STA)

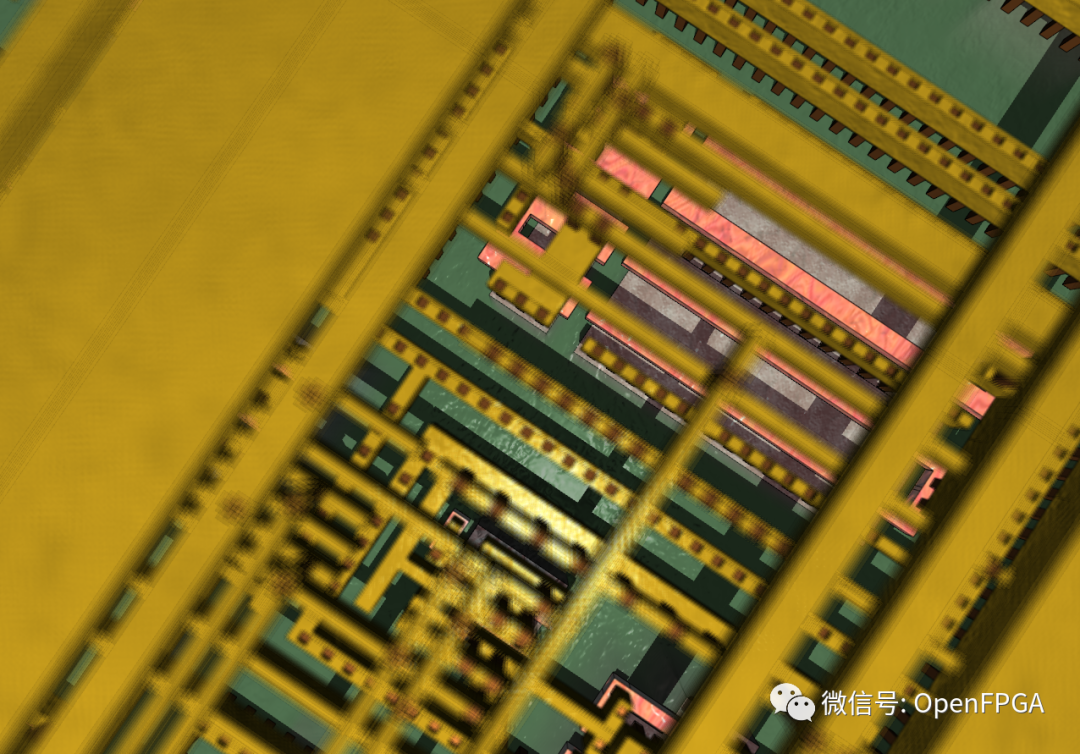

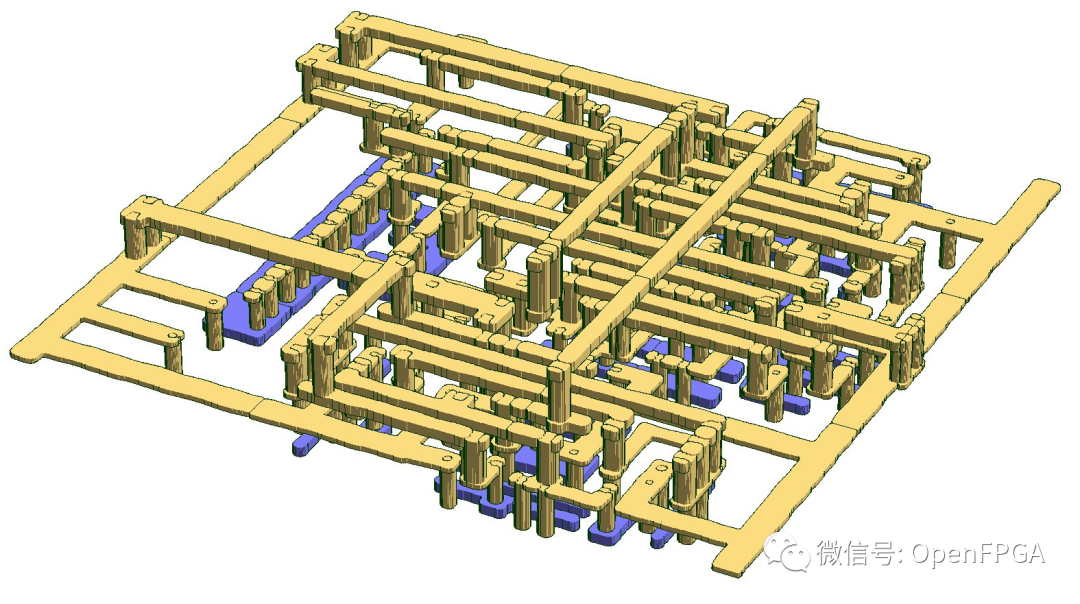

Standard Cell Design: Design process relying on a fixed set of standard cells. 标准单元设计-设计过程依赖于一组固定的标准单元

Synchronous logic: Logic whose state is controlled by a synchronous clock. 同步逻辑

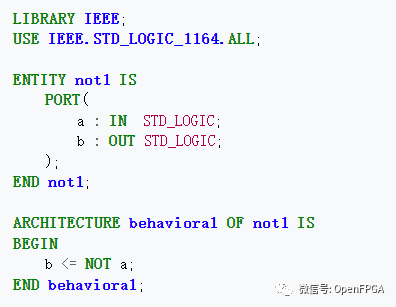

Synthesis: Translation of high level design description (e.g. Verilog) to a netlist format (e.g. standard cell gate level). 综合-将高级设计描述(例如 Verilog)转换为网表格式(例如标准单元门级)

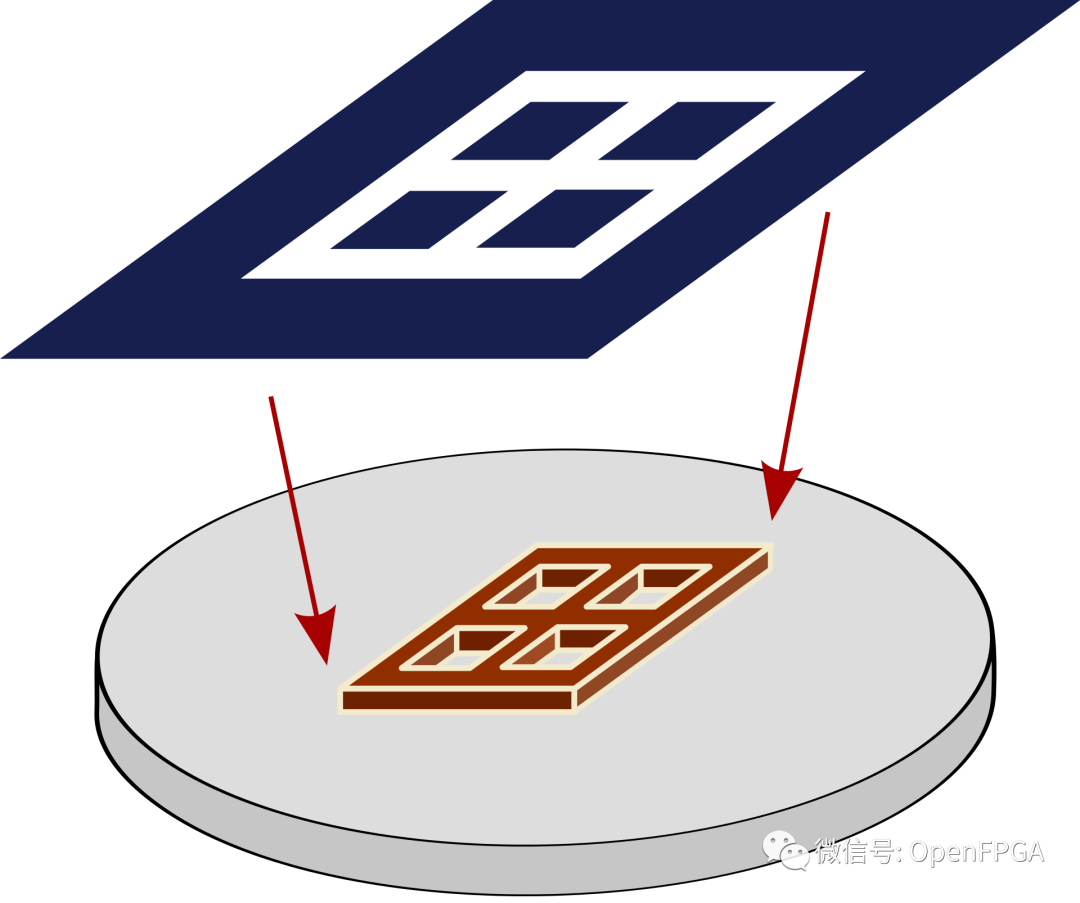

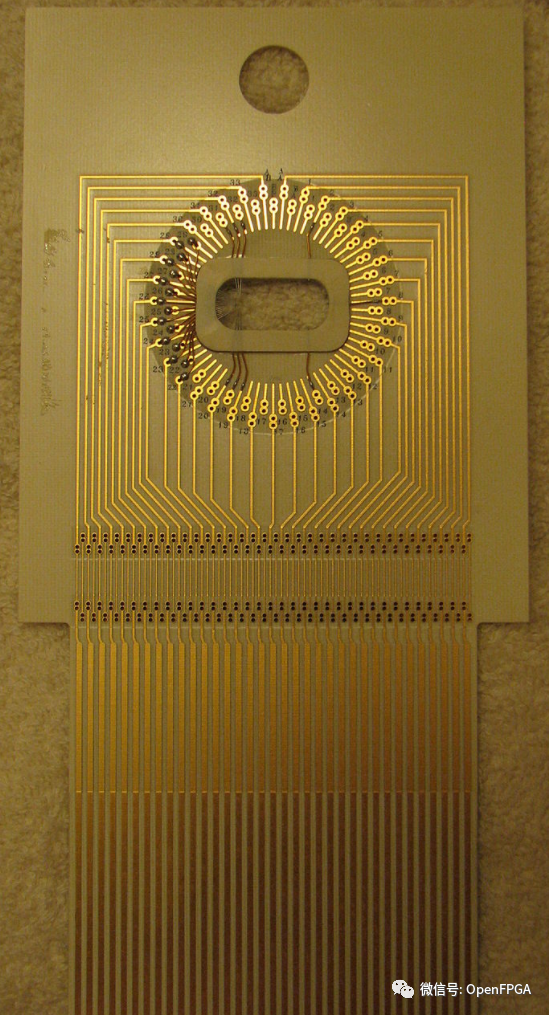

Tape-out: Act of sending photomask chip database ("layout") to the manufacturer. 流片:将光掩模芯片数据库(“布局”)发送给制造商的行为。

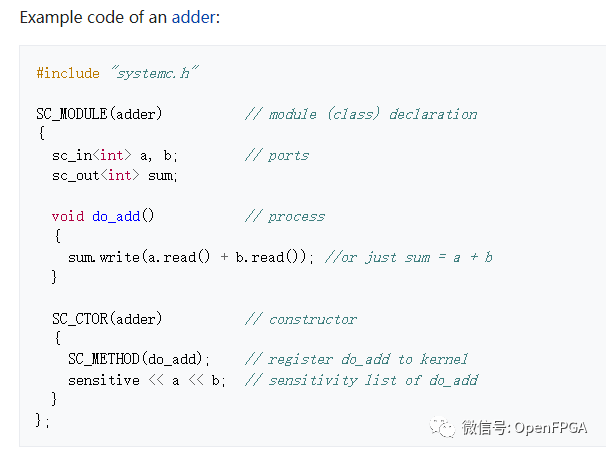

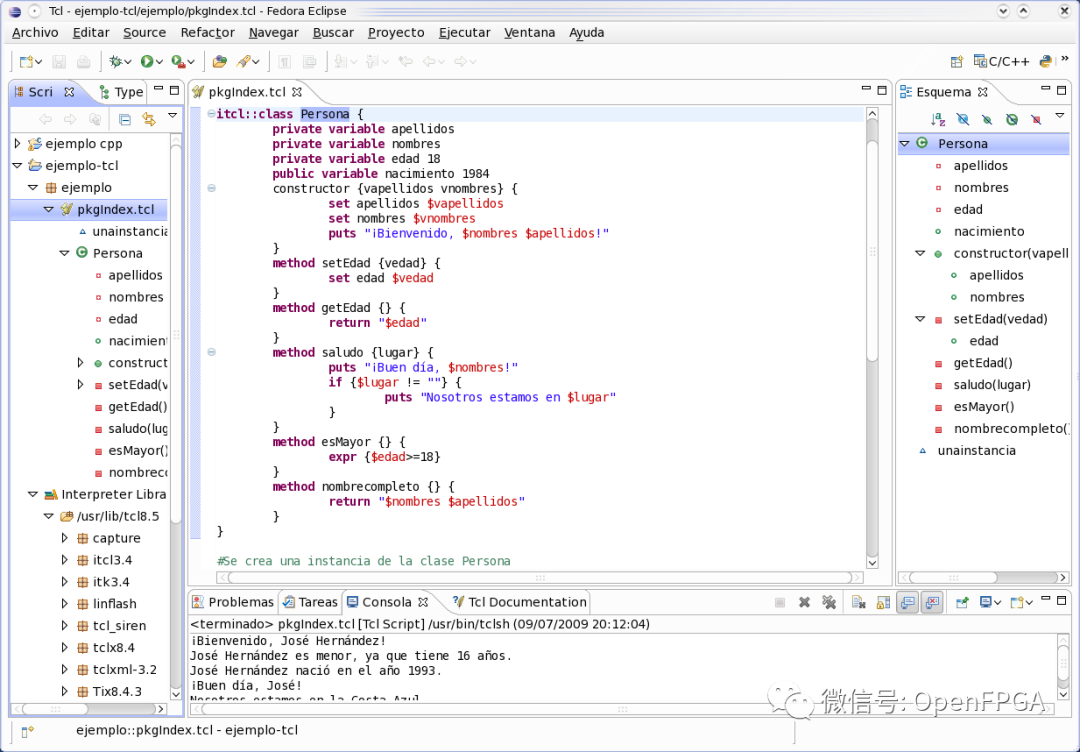

TCL: Scripting language used by most of the leading EDA chip design tools. 大多数领先的 EDA 芯片设计工具使用的脚本语言。

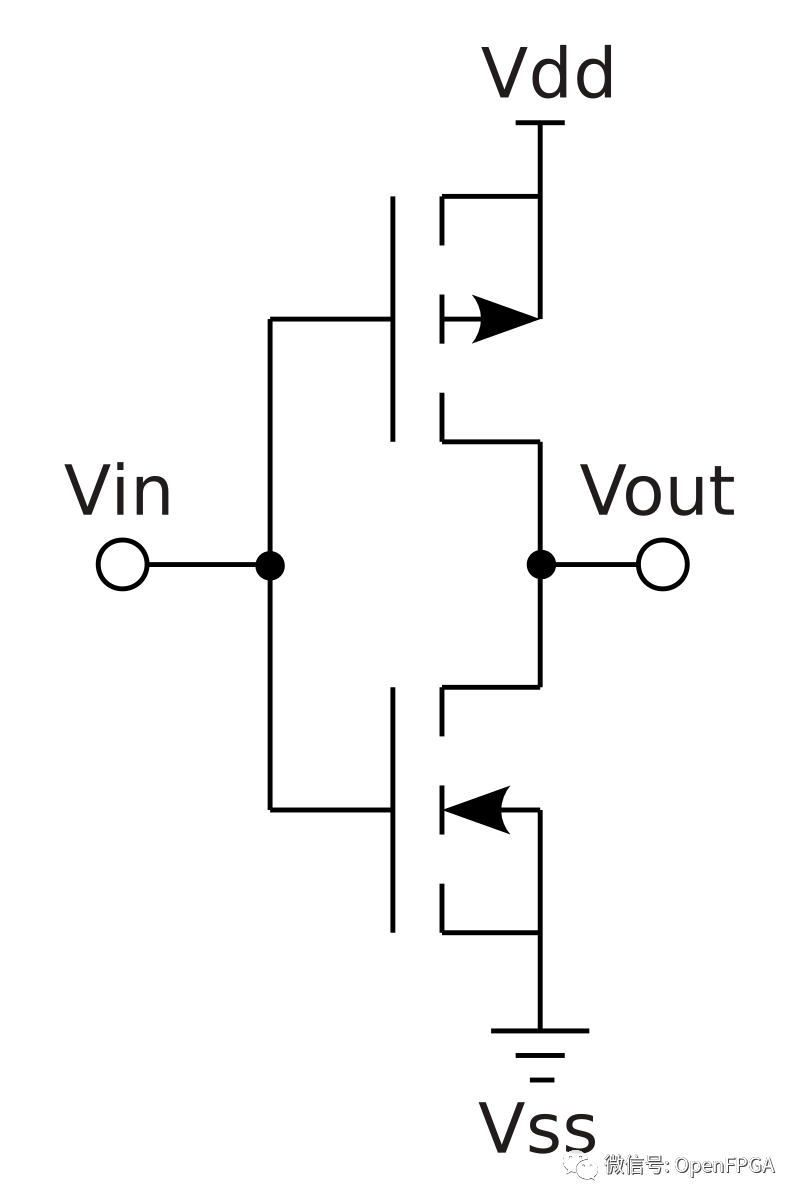

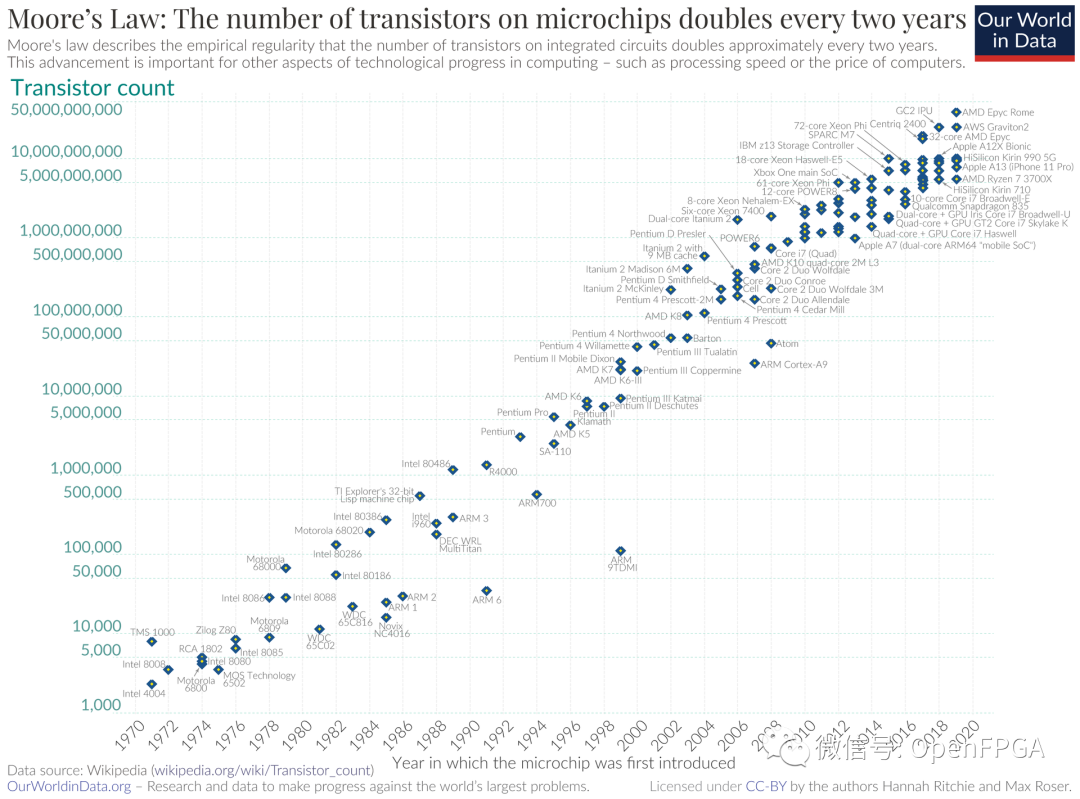

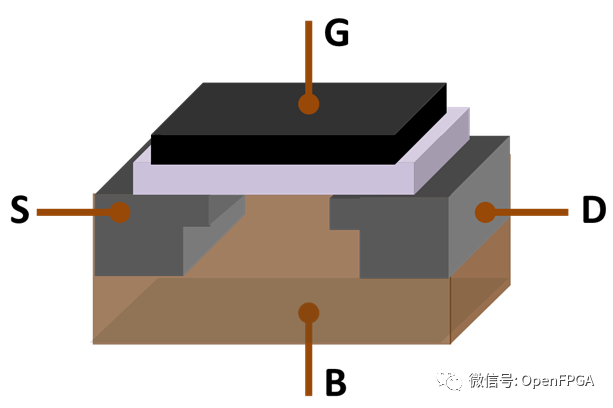

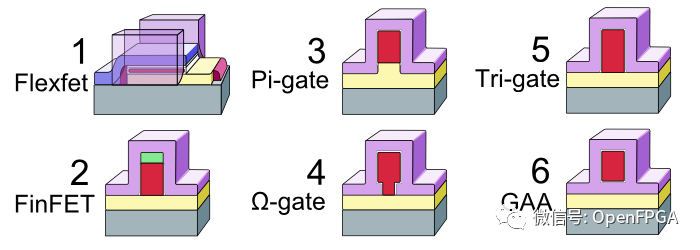

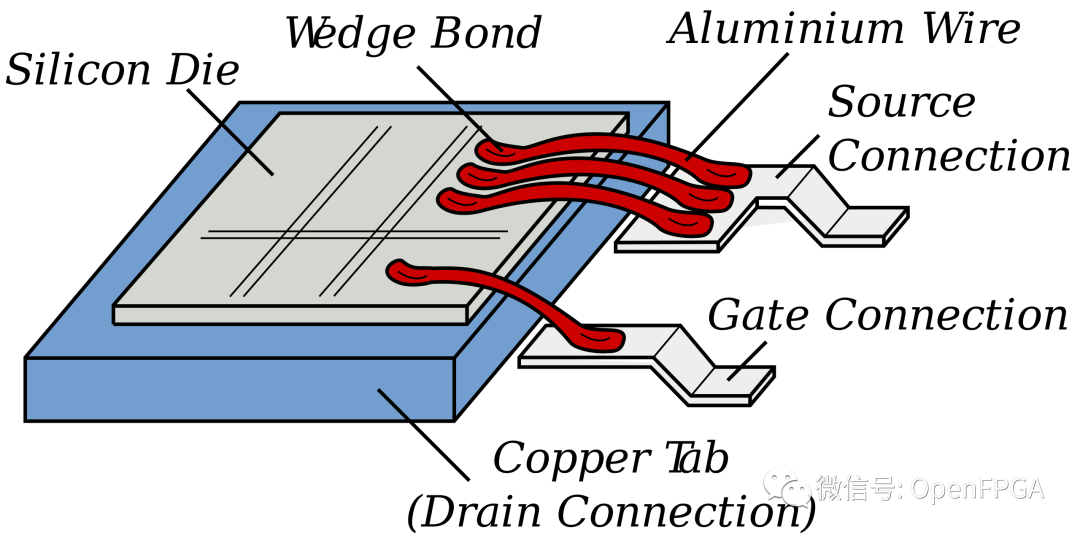

Transistor: A semiconductor device used to amplify/switch electronic signals. 晶体管

Verilog: The dominant hardware description language (HDL) for chip design. 用于芯片设计的主要硬件描述语言 (HDL)

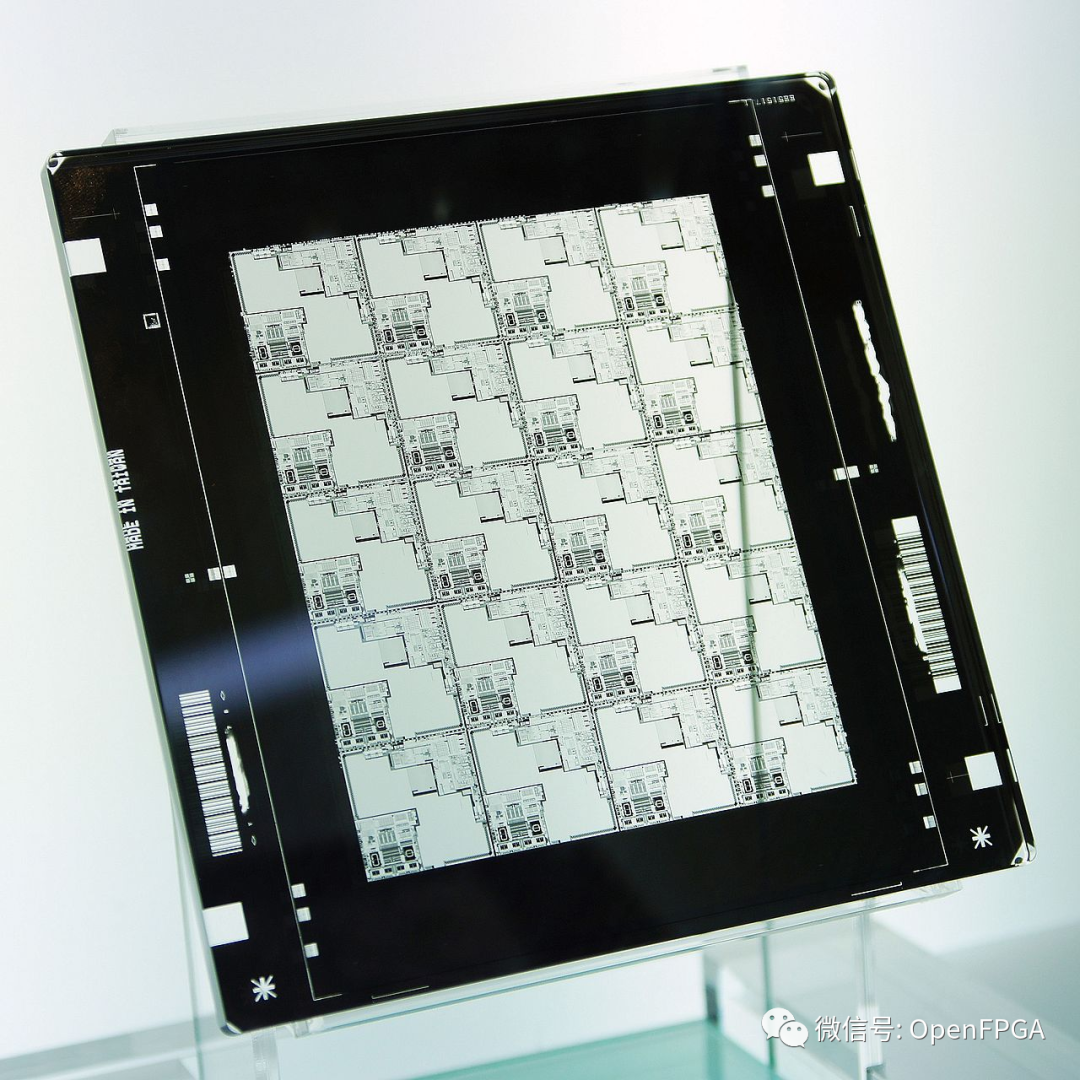

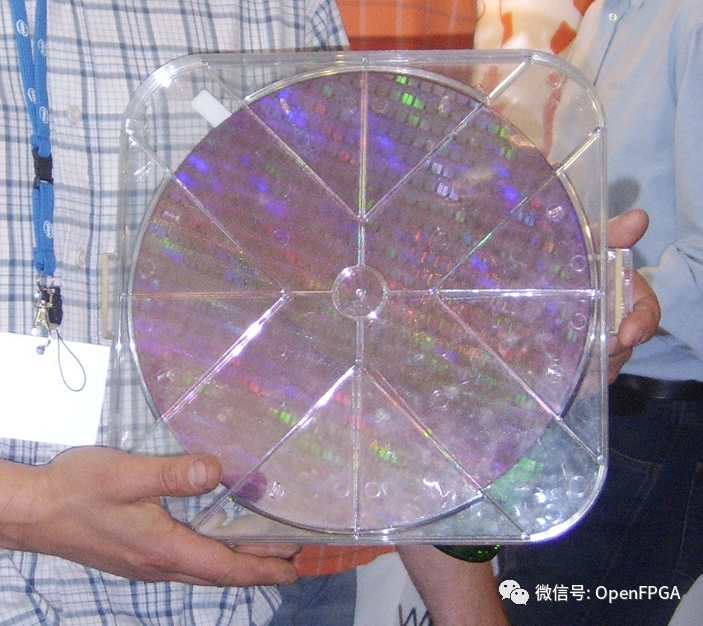

Reticle: A set of photomasks used by a stepper to step and print patterns onto a silicon wafer. 标线:步进机使用的一组光掩模,用于在硅晶片上步进和打印图案。

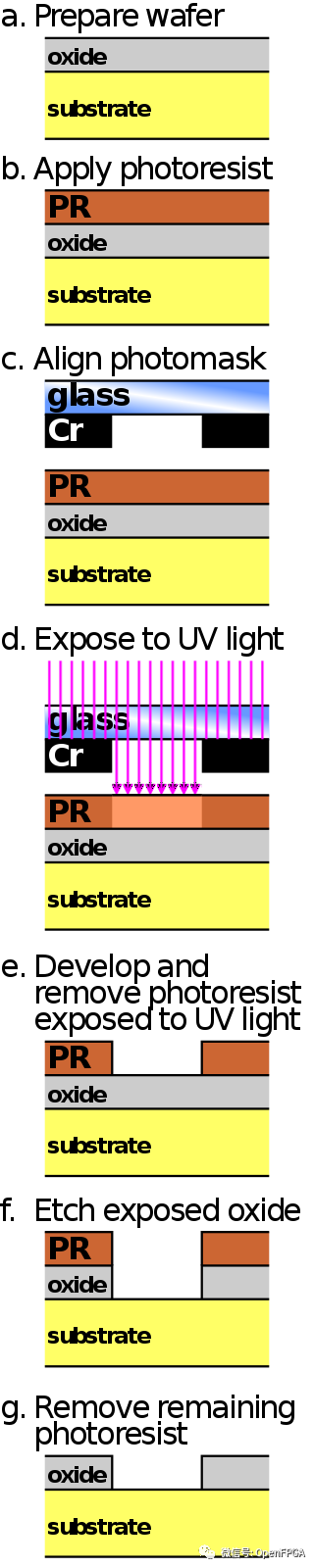

Semiconductor Fabrication: Process used to create the integrated circuits. 半导体制造:用于制造集成电路的工艺。

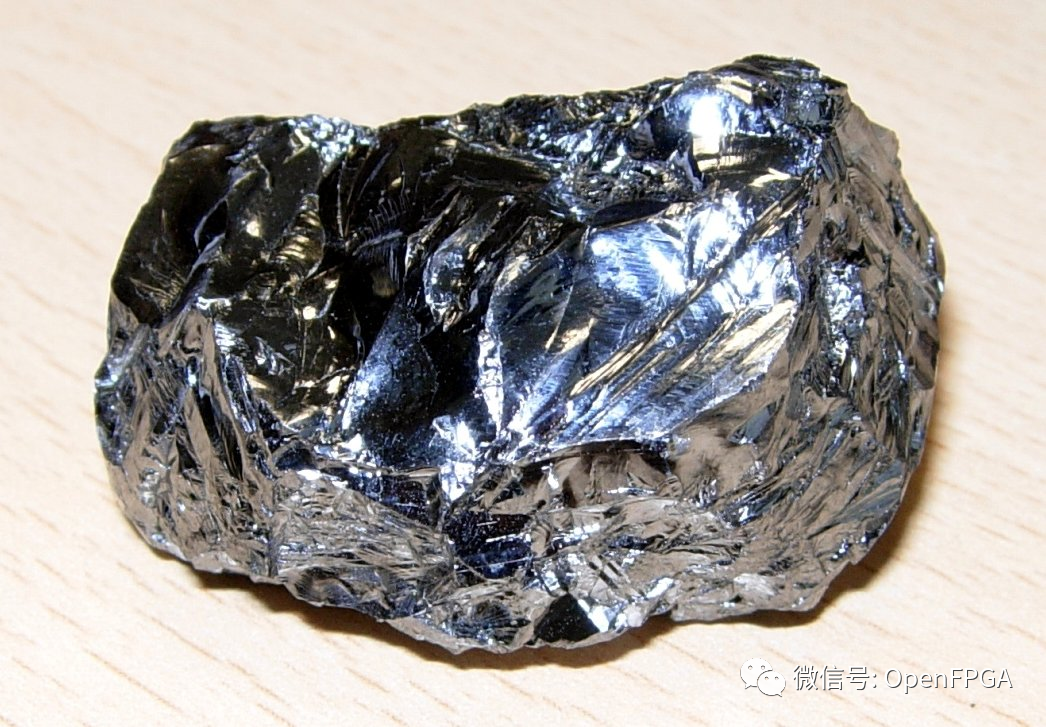

Silicon: Element (Si), forms the basis of the electronic revolution. 硅:元素 (Si),构成电子革命的基础。

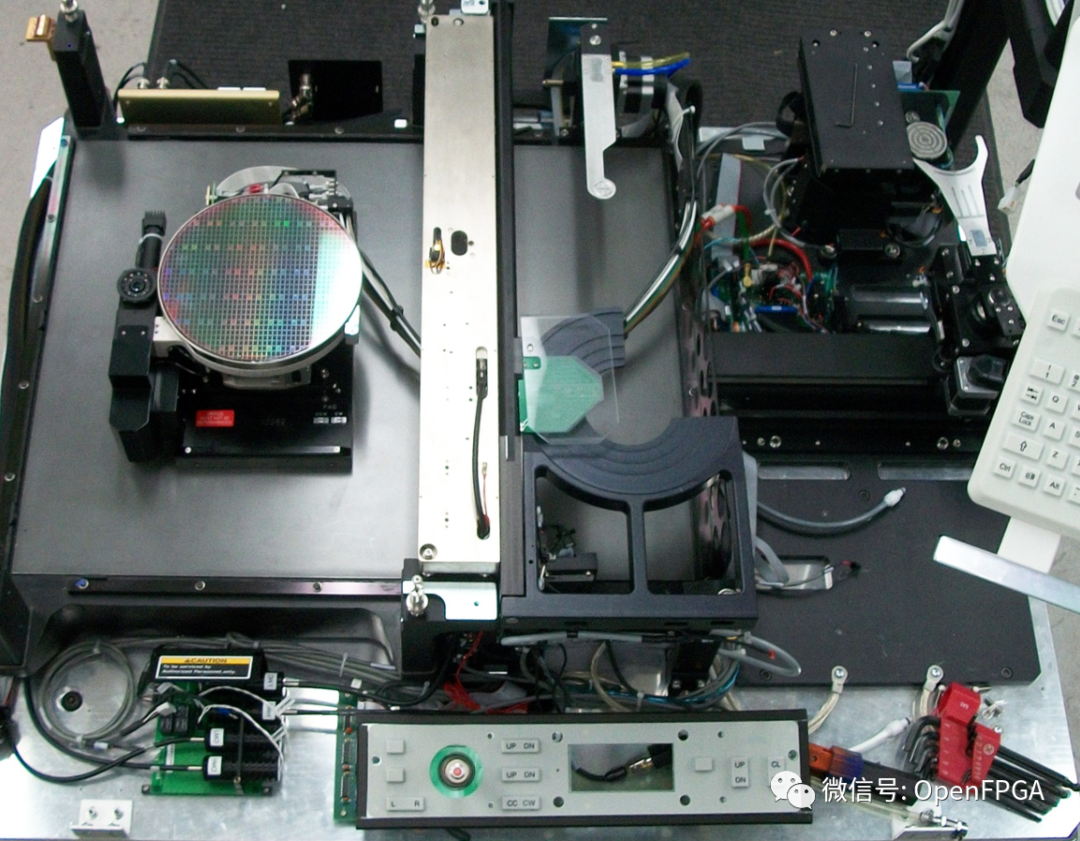

Stepper: Machine that passes light through reticle onto the silicon wafer being processed. 步进器:将光通过标线板传递到正在处理的硅晶片上的机器。

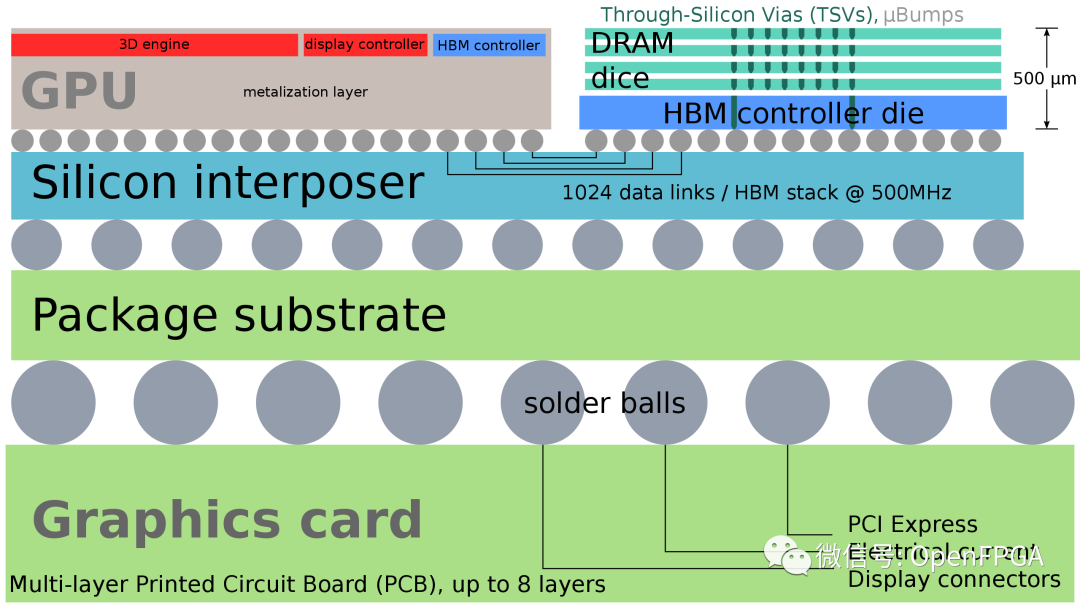

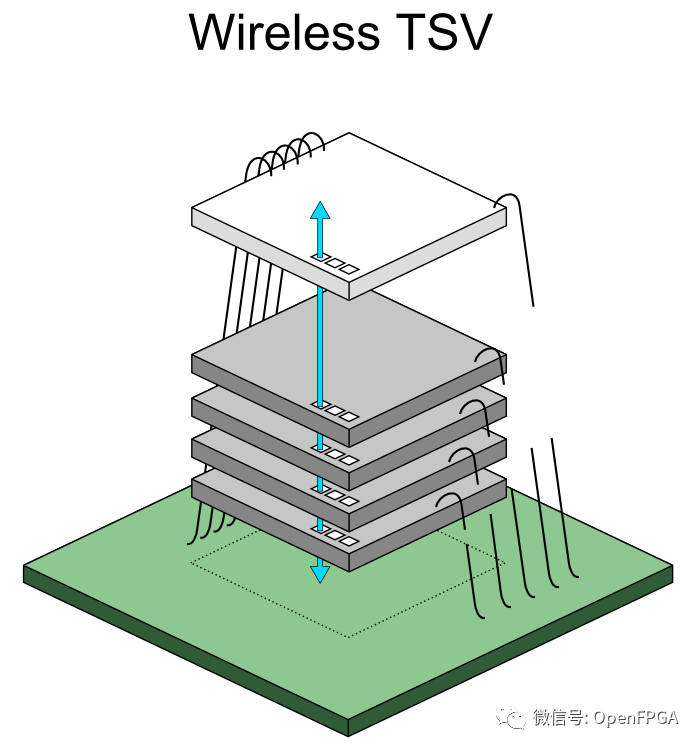

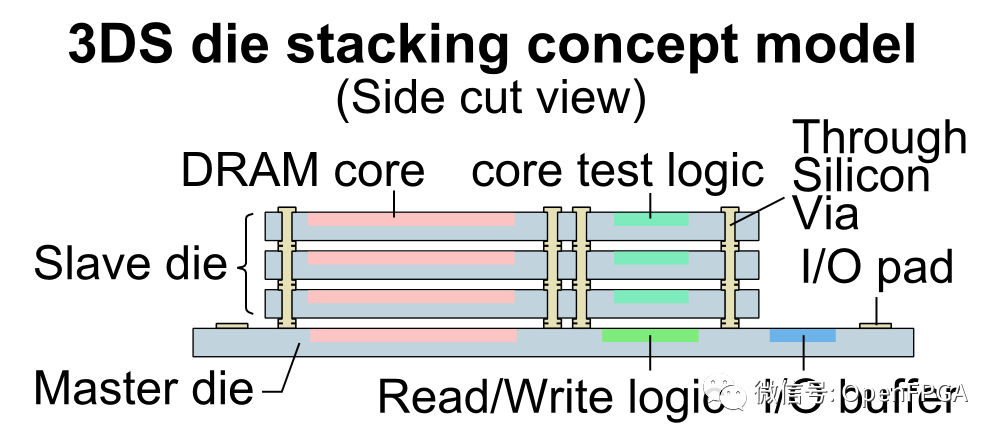

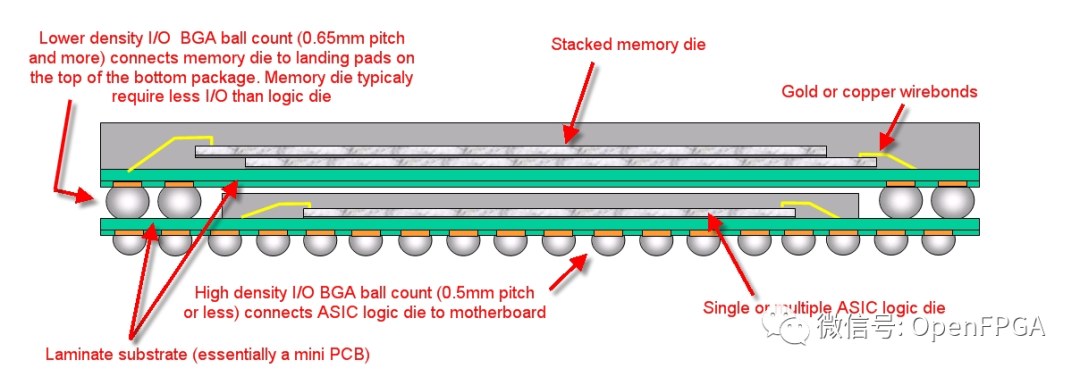

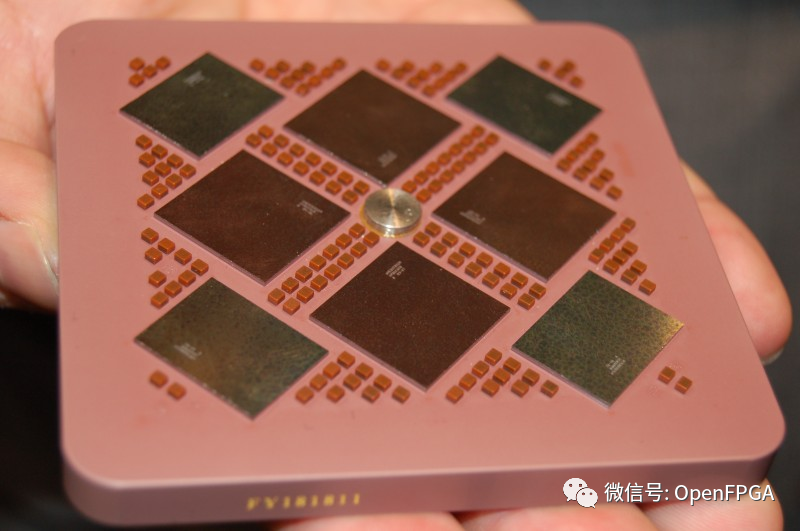

TSV: Vertical electrical connection (via) passing completely through a silicon wafer or die. 硅通孔( TSV ) 或芯片通孔是完全穿过硅晶片或芯片的垂直电连接(通孔)。

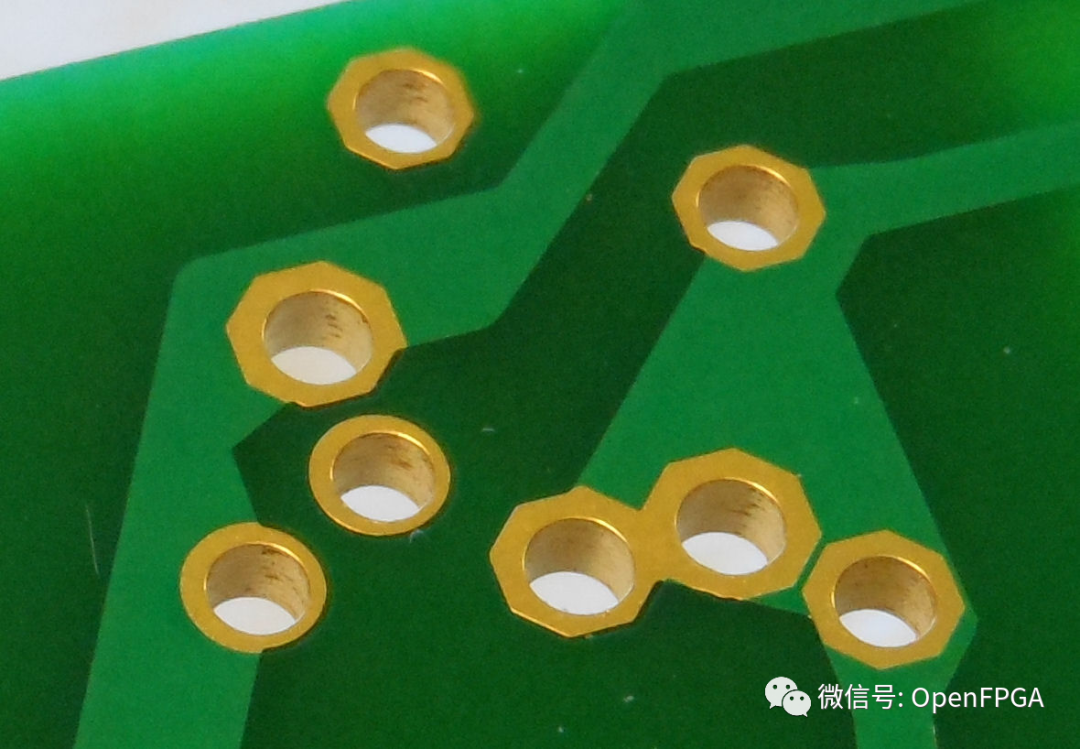

BGA: Ball grid array is a type of surface-mount packaging (a chip carrier) used for integrated circuits. 球栅阵列是一种用于集成电路的表面贴装封装(芯片载体)

BGA substrate: A miniaturized PCB that mates the silicon die to BGA pins. 将硅芯片与 BGA 引脚配对的小型化 PCB

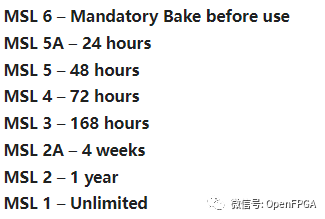

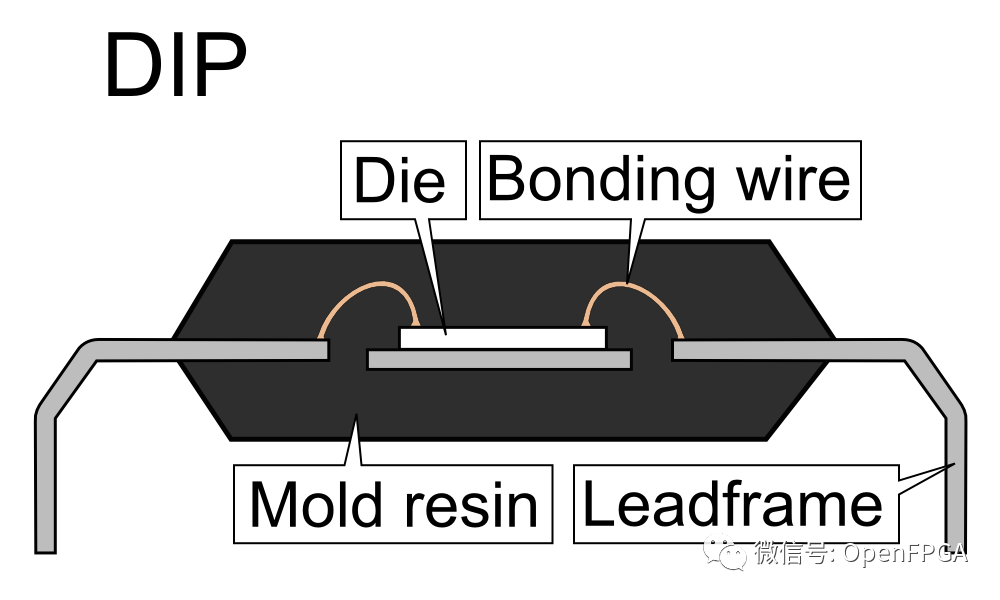

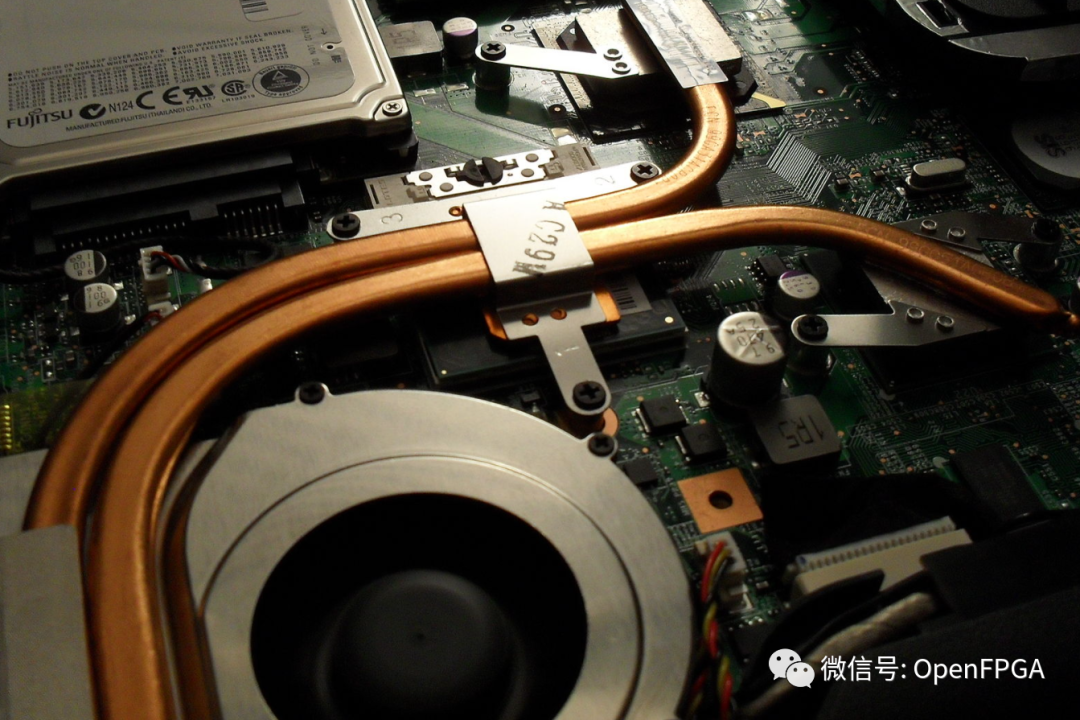

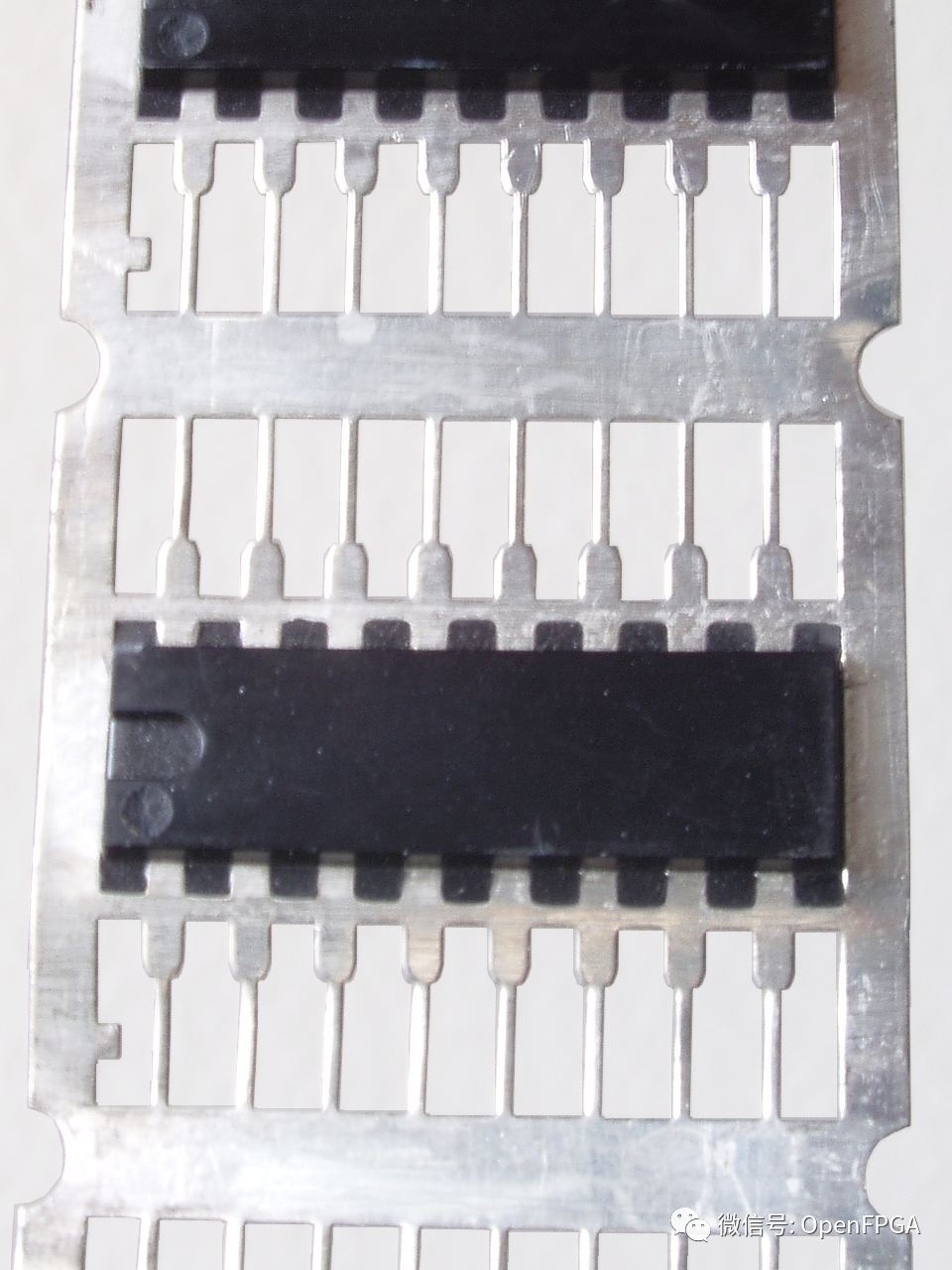

IC Assembly: Semiconductor die is encased in a supporting case "package". IC 组装

Interposer: Electrical interface used to spread a connection to a wider pitch. 用于将连接扩展到更宽间距的电气接口

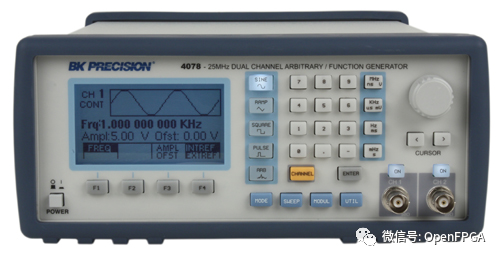

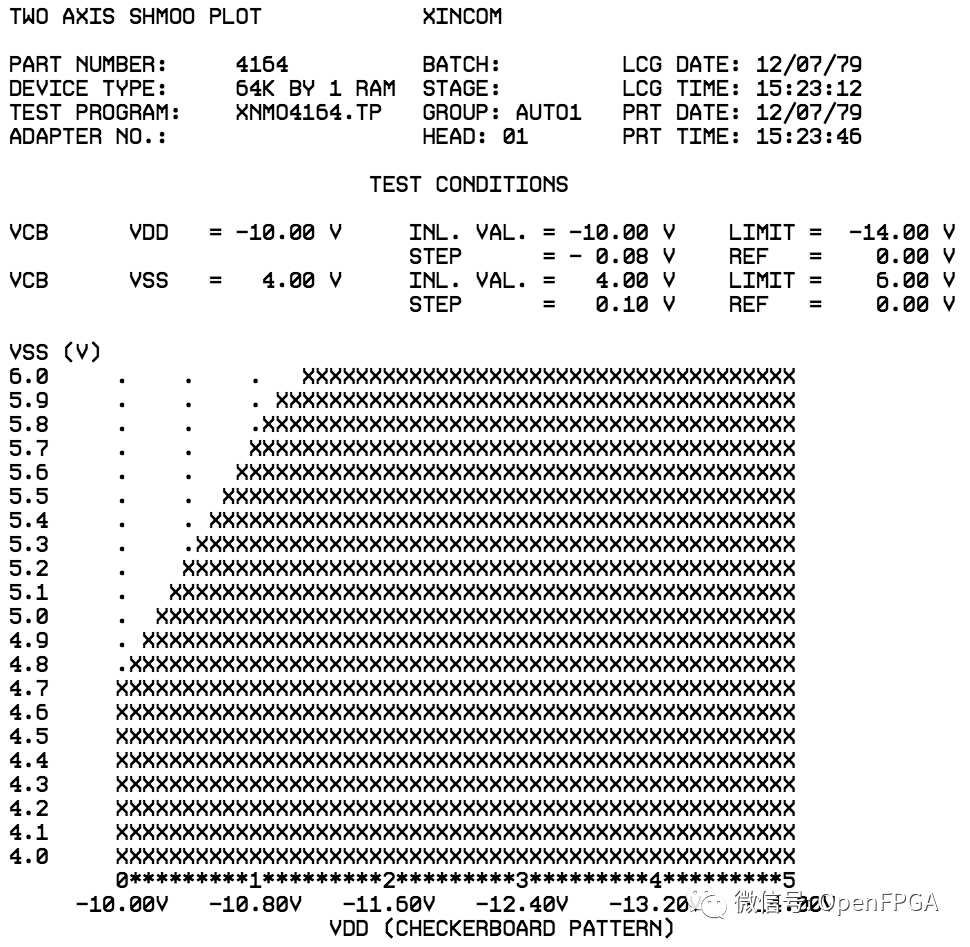

DUT: Device under test 被测设备

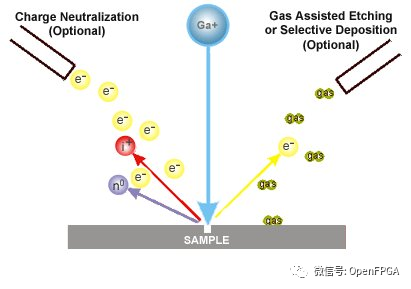

FIB: Focused ion beam 聚焦离子束

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群