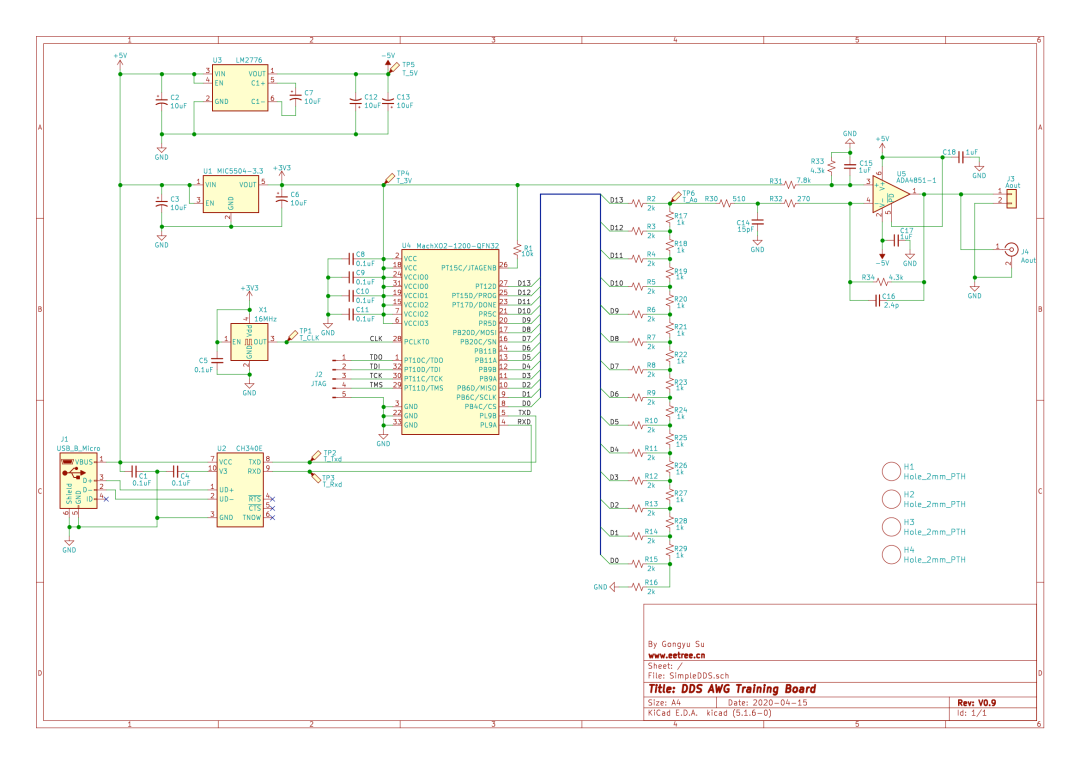

前期设计的一些电路相对都比较简单,在A4的一页图纸里就能够搞定,因此没有用到层级图。比如下面这个配合我的“入门PCB设计的正确姿势”课程的“简易DDS AWG”的设计。

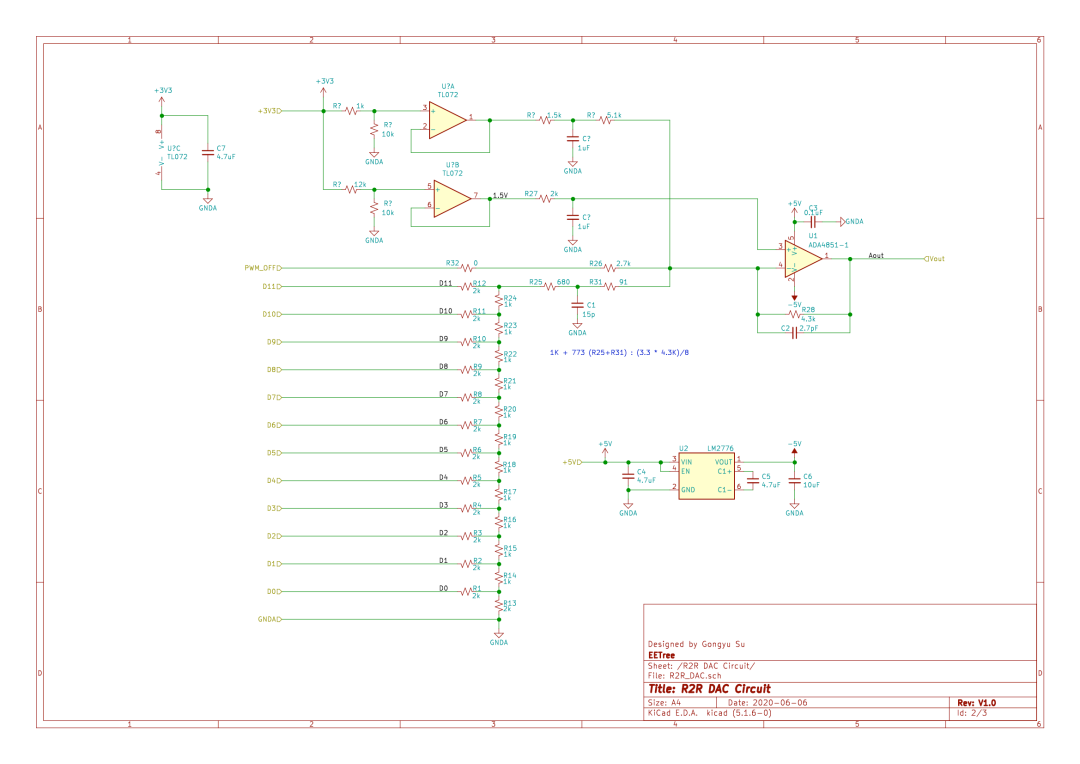

其原理图为:

A4纸,一页搞定。

细心的读者会看到这个设计中FPGA是用外部的适配器通过一个5针的插座进行JTAG配置的,在新的设计中我想将JTAG配置这部分电路也放在板子上,只需要一个USB端口,就可以完成FPGA的配置、板子的供电以及通过USB的UART数据通信,在后期我还打算扩展键盘和按键的接口。

JTAG的配置电路我计划用STM32F103来实现,这个器件的常用封装是TQFP48,粗略估计了一下如果将所有这些功能放置在一张图纸中,会非常拥挤(肯定也能放得下,尤其是可以调整为采用A3的图纸)绘制和修改起来相对都比较麻烦,为了方便连接,需要调节STM32或FPGA的管脚排列位置。

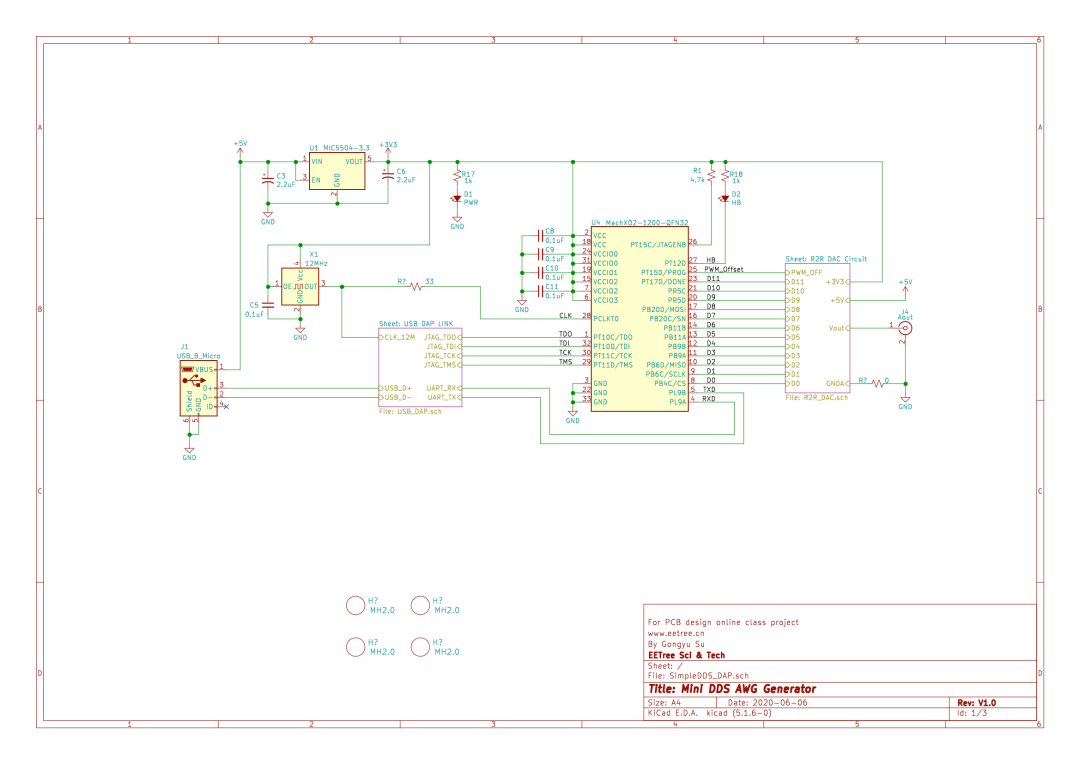

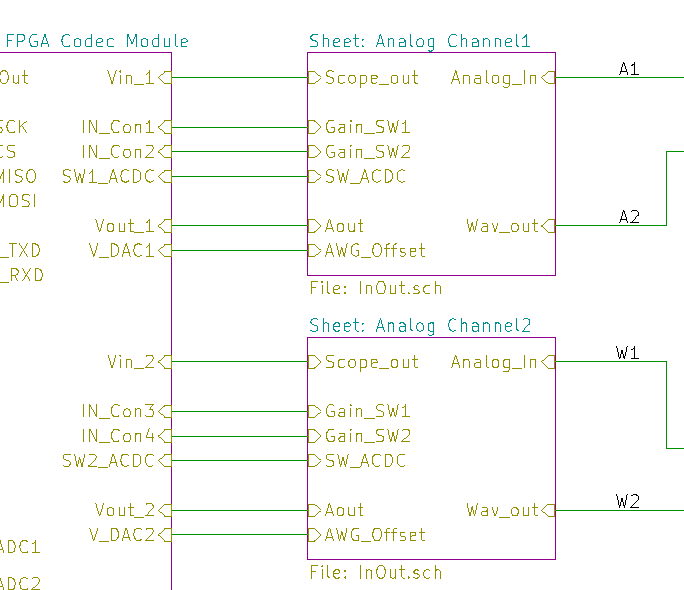

因此我打算采用层级图的方式来做这个工程,于是加上了JTAG配置电路的工程就成了这样:

顶层原理图,其中有两个“模块”

双击这两个模块,可以进入到相应的原理图:

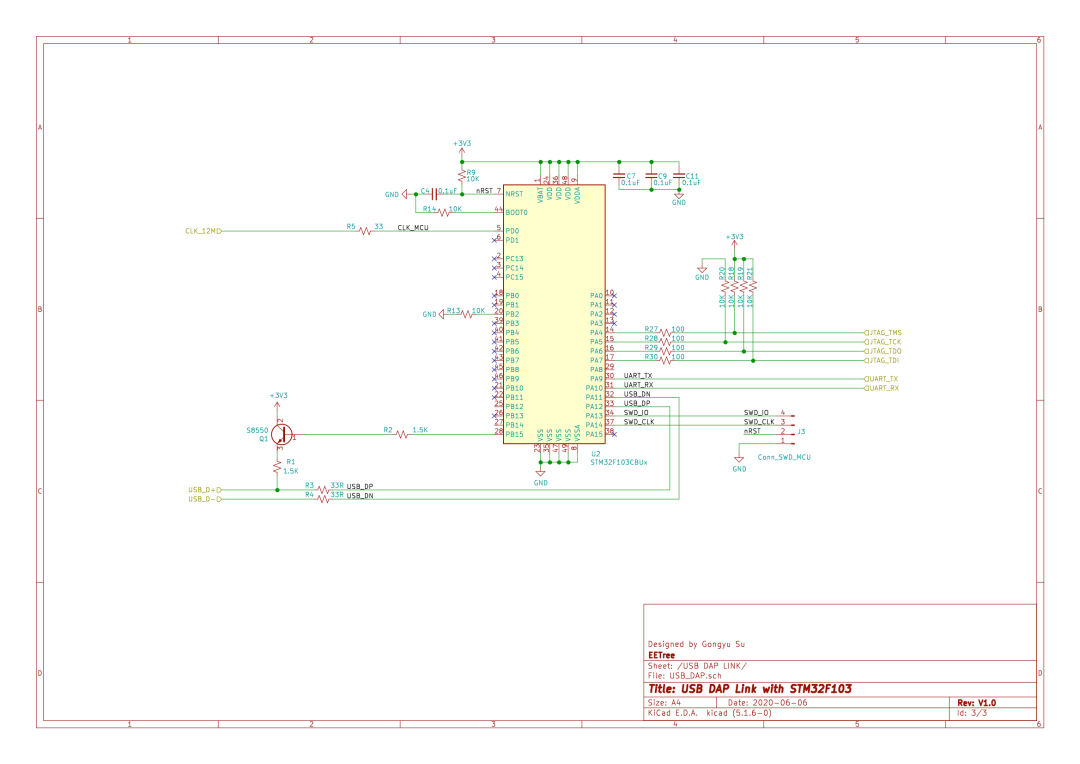

使用STM32F103,支持JTAG下载和数据通信原理图

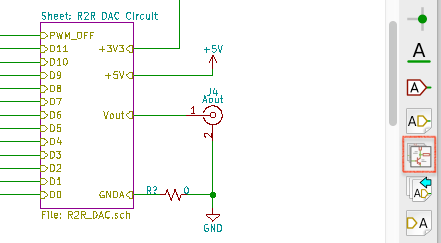

12bit的R2R DAC电路原理图

使用层级图设计的好处:

模块化设计,功能清晰

避免了在一张图纸上不得不用文字标注net进行连接带来的混乱,可以通过将某些信号连接到模块的端口,模块和模块之间用“连线”直接连接,逻辑非常清晰,降低出错的几率

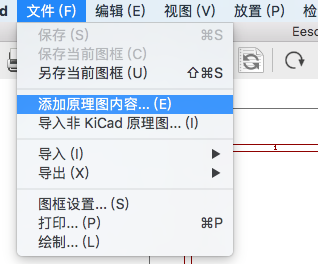

方便复用已经经过验证的功能电路,比如R2R DAC是我们已经用在其它项目中的功能模块,可以做成标准化的单页原理图(封装成标准的功能模块),被其它项目来调用(如下图中的菜单功能)。

在多个通道的电路都是一样的情况下,这种模块化的方式就更方便了,如果修改电路,只需要点击一个模块,进入其原理图,修改,则多个相同功能模块的原理图同步进行了更改。比如下图中,inout.sch模块里,每个模块都包含一个ADC通道和一个DAC通道,如果修改电路,只需要修改其中一个通道的即可。

如何操作呢?

1 在任何一页图纸中,点击右侧的“创建分层图框”的按钮(下图中红色所示)

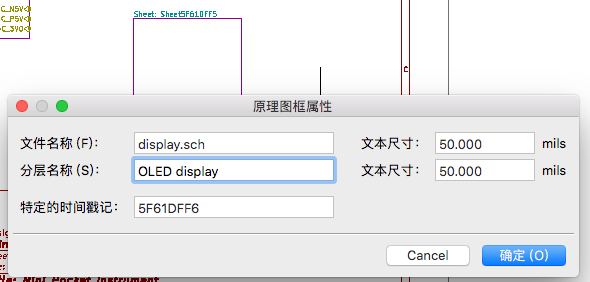

在原理图上就会出现一个方框,并弹出如下图的对话框,你可以给定该模块原理图文件的名字以及分层的名称 - 一看就懂的说明性文字。

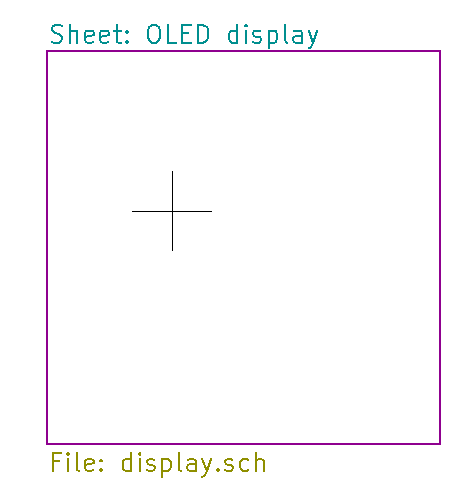

点击确定以后,图纸上就会出现下面的一个功能模块

悬浮鼠标在这个框上,右键 --》“进入分页”,即可在这个模块对应的原理图页面中进行原理图的编辑。

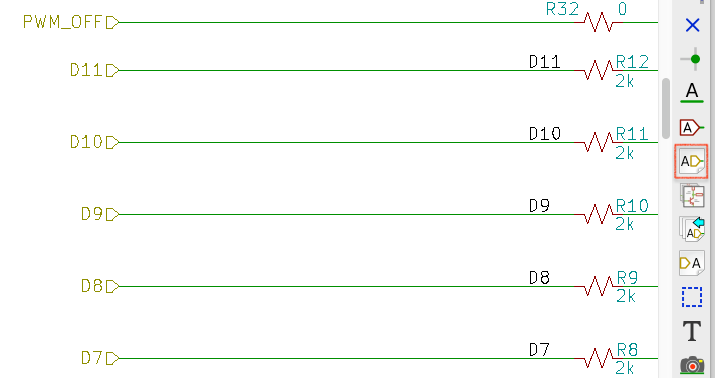

绘制好原理图,可以添加模块的输入输出端口(类似Verilog Module中定义的端口一样),点击上图中右侧红色框定的功能按钮“放置一个层次标签”,添加如上图左侧一样的端口标签(net名)

编辑完毕,鼠标在图纸任何地方,右键 --》 “离开图框”,就会到上一级的模块符号页面,将鼠标悬浮在模块的符号框上,点击右键 --》 “导入图框连接”,即可将在下一级原理图中添加的端口net一一添加在模块符号的左、右侧,并可方便用鼠标对这些端口符号进行上下移动操作,当然也可以调整符号图框的大小。

你可以自己体验一下,非常方便。

Enjoy!

祝大家周末愉快!