PCI Express(PCIe) 串行通信标准支持最多 16 路全双工数据传送。标准要求接收机容忍一定的通路间时延,如果超过这个限制,就会损害链路稳定性和性能。本文介绍了怎样准确测量最大数据速率为 32 GT/s (Gen5) 的PCIe 发射机中的通路间时延。这些规程可以简便地加以调整,支持数据速率更低的测量。在第一部分,我们展示了怎样校正测量系统(实时示波器)的时延;在第二部分,我们介绍了怎样配置被测器件 (DUT),执行准确的通路间时延测量。

第一部分:校正实时示波器通道时延

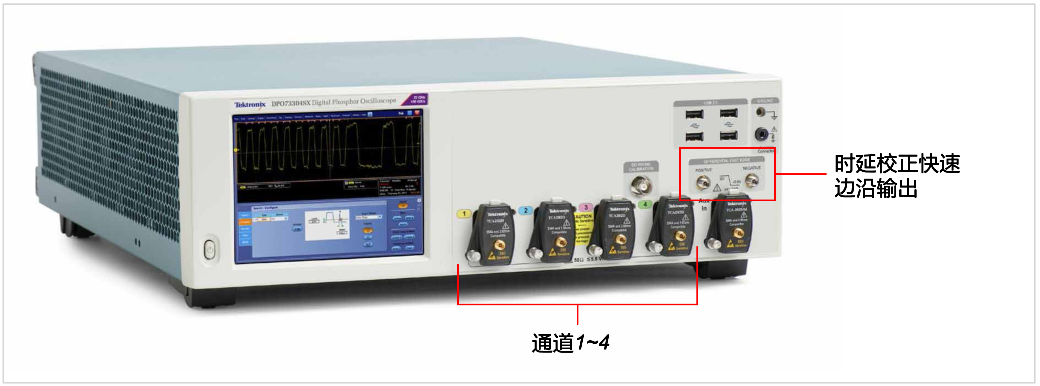

为准确地测量 DUT 的时延,我们必须先校正测量仪器的时延。一般来说,我们会使用 4 条示波器通道,进行通路间时延测量。在本指南中,我们使用泰克 DPO73304SX,这是一台 4 通道实时示波器。我们将根据一条目标通道来校正全部 4 条通道的时延。下面的步骤描述了怎样根据通道 1 校正通道 2、3、4 的时延。

1. 通过一对相位匹配的 2.92 电缆,把 Fast Edge Positive 正快速边沿连接到示波器通道 1,把 Fast EdgeNegative 负快速边沿连接到通道 2。

● 注:相位匹配的电缆对建议在 ±1 ps 时延范围内。泰克产品编号:PMCABLE1M

2. 调节垂直刻度,使用满刻度。注意根据规范,Fast Edge 输出为 440 mV ± 20 % 到 50W 负载。

3. 调节水平设置如下:

● Mode: Manual

● Sample Rate: 100 GS/s

● Record Length: 100K

4. 可以使用默认的触发设置,否则设置如下,然后点击 Set to 50% 按钮,自动设置触发电平。

● Trigger type: Edge

● Source: Ch1

● Slope: Rising

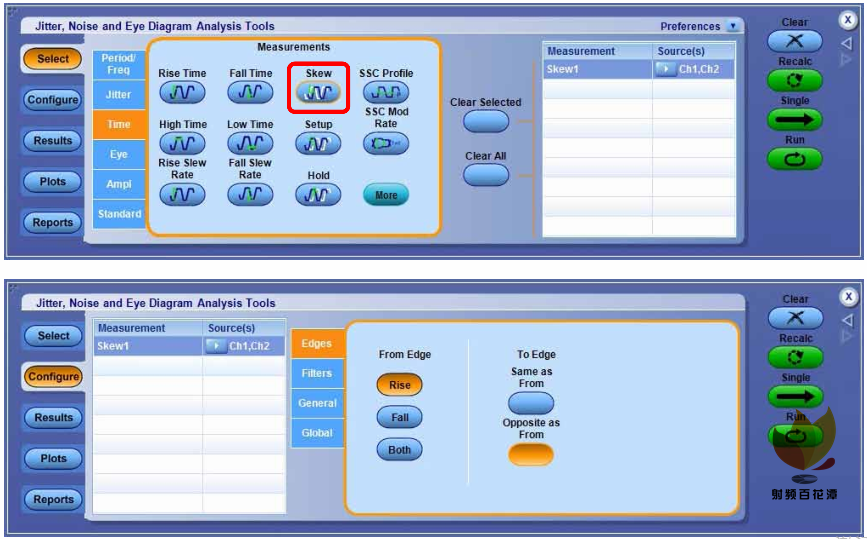

5. 启动 DPOJET,配置 Skew Measurement 时延测量。

● 进入 Analyze -> DPOJET

● 在 DPOJET 中:Select -> Time -> Skew Measurement

● 配置 Sources -> Ch1, Ch2

● 配置 Edges -> From Edge to Rise, To Edge to Opposite From.

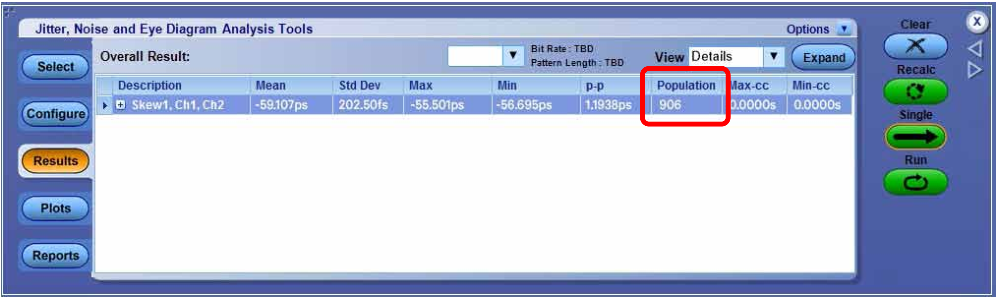

6. 点击右面的 Run 运行按钮。观察 DPOJET 结果中的样本数。在样本数达到 1000 时,点击 Stop 停止按钮。

● 注:在执行这个程序时,DPOJET 会一直显示红色 X 错误指示灯。错误表明测量没有足够的边沿执行时钟恢复。时延测量不要求时钟恢复,所以这个错误完全可以忽略。

8. 把时延测量值设置成 Deskew。

● 进入 Vertical -> Deskew

● 从 Channels list 通道列表中选择 Ch2。

● 输入时延测量值。

9. 到现在,我们已经完成从 Ch2 到 Ch1 的时延校正。

10. 把连接示波器 Ch2 的电缆移到 Ch3,现在 Fast Edge Negative 负快速边沿连接到 Ch3。

11. 进入 Vertical -> Vertical Setup,把 Ch2 设置成 Display Off,把 Ch3 设置成 Display On。

12. 重复第 2 步到第 8 步,完成从 Ch3 到 Ch1 的时延校正。

13. 把连接示波器 Ch3 的电缆移到 Ch4,现在 Fast Edge Negative 负快速边沿连接到 Ch4。

14. 进入 Vertical -> Vertical Setup,把 Ch3 设置成 Display Off,把 Ch4 设置成 Display On。

15. 重复第 2 步到第 8 步,完成从 Ch4 到 Ch1 的时延校正。

第二部分:执行通路间时延测量

在完成示波器通道时延校正后,我们可以配置 DUT 进行通路间时延测量。在下面的程序中,我们先介绍所需的设备,以及控制 DUT 发射机输出信号的信号路由。然后,我们介绍 DUT 及执行通路间时延测量的推荐配置。

1. 准备以下设备,用来生成切换信号 (100 MHz 脉冲,1 ms 突发时间 )。

● PCIe Gen 5 CEM 测试夹具 (PCI-SIG Rev 3);和

● 任意函数发生器 ( 泰克 AFG31252);或

● 任意波形发生器 ( 泰克 AWG7122C)

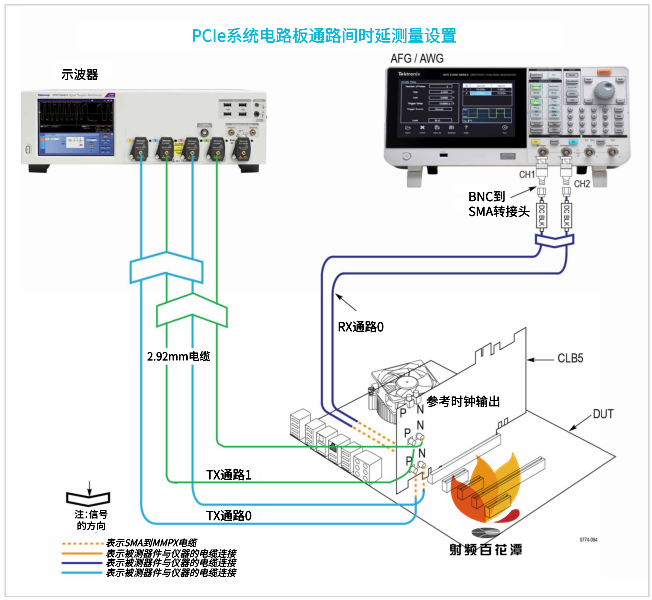

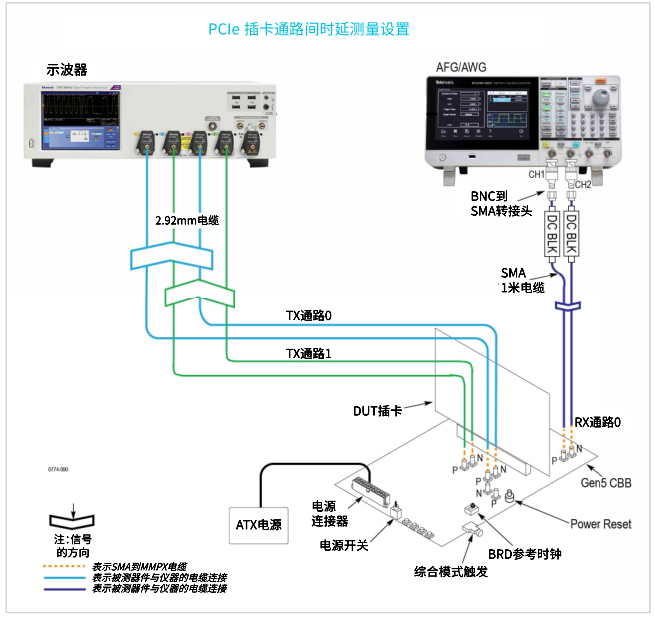

2. 对发射机 / 接收机信号接入,根据 DUT 类型设置以下项目:

● 对 BASE DUT - PCIe Gen 5 评估平台

● 对 CEM DUT - PCIe Gen 5 CEM 测试夹具

- 系统电路板 - 一致性测试负载电路板 (CLB)

- 插卡 - 一致性测试基本电路板 (CBB)

3. 信号路由

● 把切换信号连接以 Rx 通路 0。

- 切换信号正 -> Rx 通路 0 正;切换信号负 -> Rx 通路 0 负

● 例如,为测量通路 0 到通路 1 时延,与示波器的连接如下。

- Tx 通路 0 正 -> 示波器 Ch1

- Tx 通路 0 负 -> 示波器 Ch3

- Tx 通路 1 正 -> 示波器 Ch2

- Tx 通路 1 负 -> 示波器 Ch4

● 注:电缆要尽可能短,以最大限度地降低插入损耗。

系统电路板 DUT 的连接图

插卡 DUT 的连接图

4. 把切换信号 (100 MHz 脉冲,1 ms 突发时间 ) 发送到 DUT 接收机通路 0,控制 DUT 发射机输出信号。

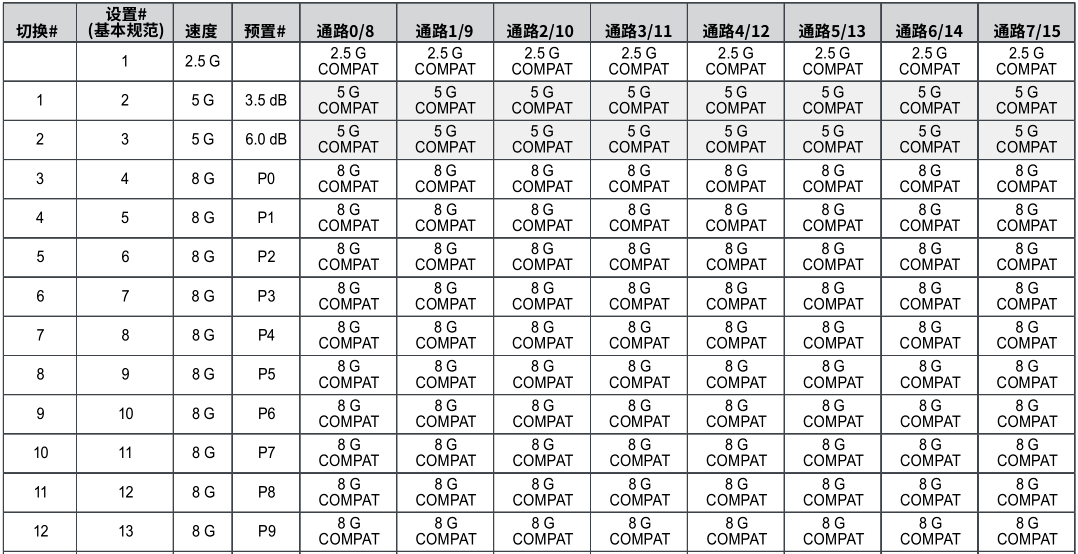

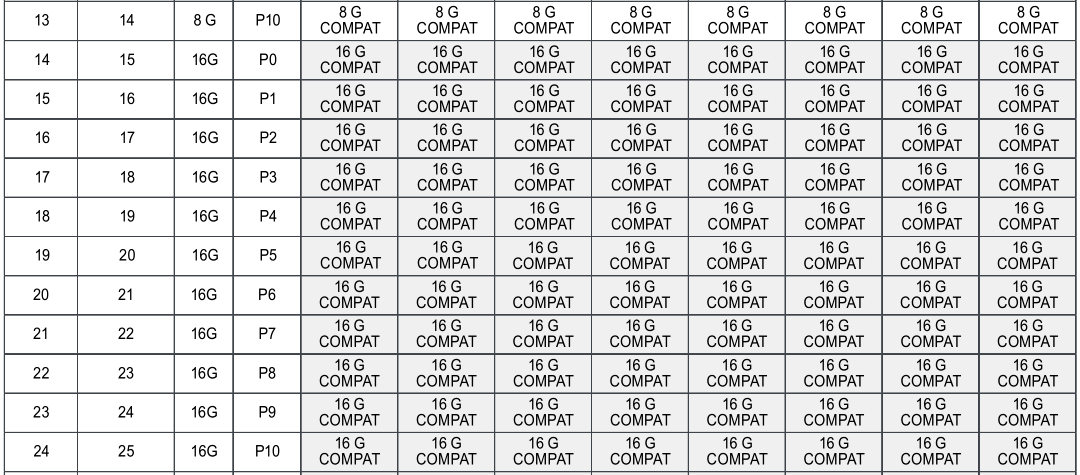

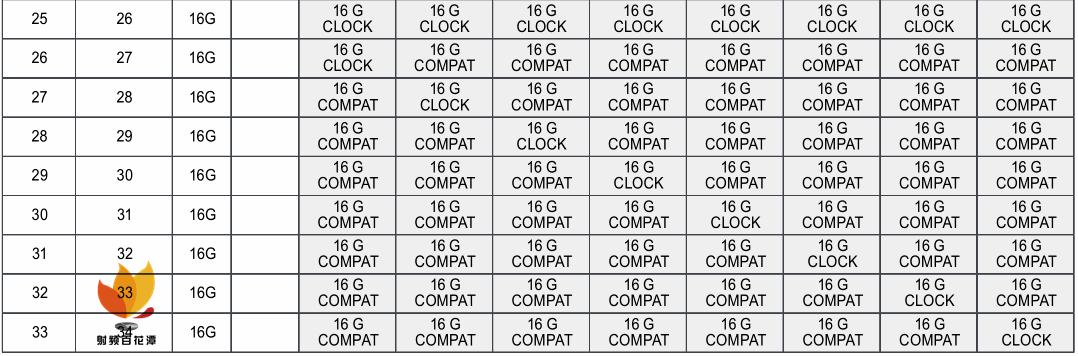

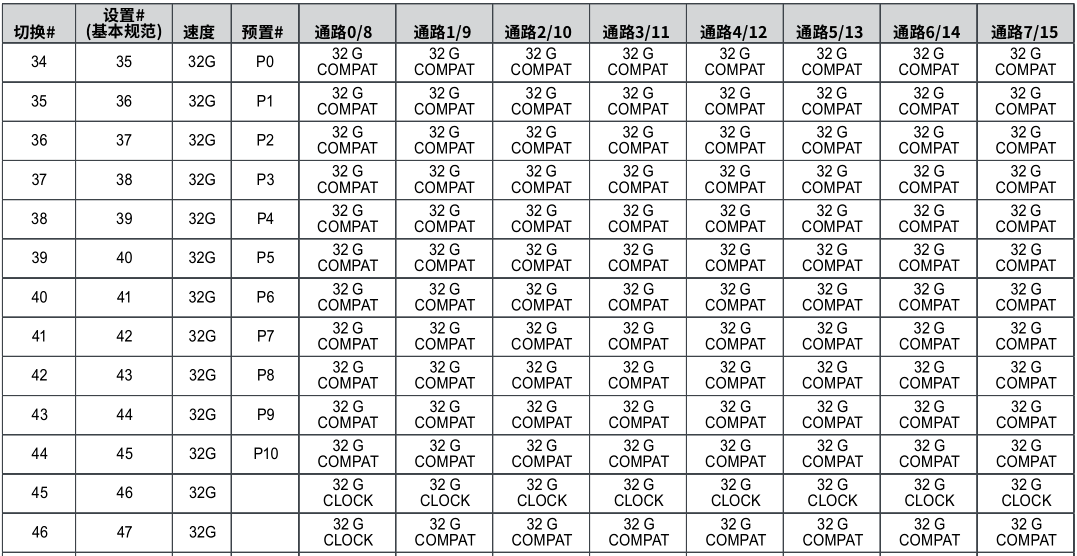

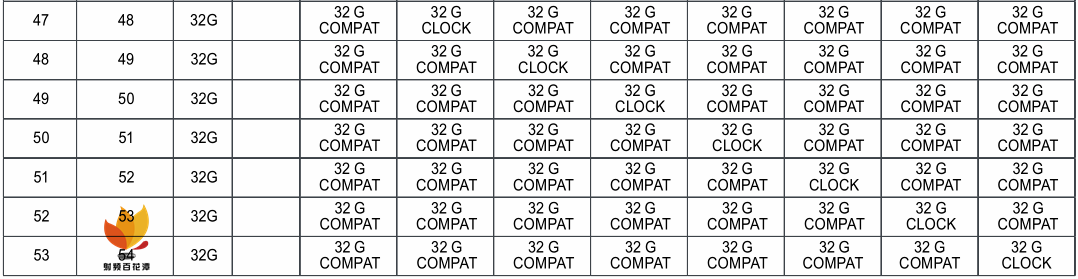

DUT Tx 输出信号在开机时是 PCIe Gen1 (2.5GT/s)。通过发送第一个切换信号,DUT Tx 输出信号会切换到 PCIe Gen2 (5GT/s),预置值为 3.5 dB。然后发送第二个切换信号,DUT 输出信号切换到 PCIeGen2,预置值为 6 dB。发送第三个切换信号,DUT 会发送 PCIe Gen3 (8GT/s),预置值为 0。我们在附录中提供了完整的 DUT Tx 输出信号列表。注意一旦到达最后的码型,DUT 输出信号会回到 Gen1。

5. 为执行通路间测量,我们推荐把 DUT 发射机配置成 Preset 6 for PCIe Gen5,发送切换信号 40 次,可以实现这一操作。

● 注:由于最优 Tx Preset 预置值在不同 DUT 之间可能会变化,所以本节最后提供了一个可选步骤,阐述了怎样使用 SigTest 分析工具确定最优 Tx Preset 预置值。

6. 配置示波器 Horizontal Settings 水平设置。

● Sampling Mode: IT (Interpolate)

● Mode: Manual

● Sample Rate: 200 GS/s

● Record Length: 625K

7. 为 Tx 通路配置示波器 Math Channel 数学通道。

● 设置 Math1 = Ch1 - Ch3

● 设置 Math2 = Ch2 - Ch4

8. 示波器触发设置配置如下。使用脉冲宽度触发,捕获一致性测试码型的 64 个 1/64 个 0 部分。

● Trigger type: Pulse Width

● Source: Ch1

● Width: 2 ns

9. 启动 DPOJET,配置时延测量。

● 进入 Analyze -> DPOJET

● 在 DPOJET:Select -> Time -> Skew Measurement

● 配置 Sources -> Math1, Math2

● 配置 Edges -> From Edge to Rise, To Edge Same as From.

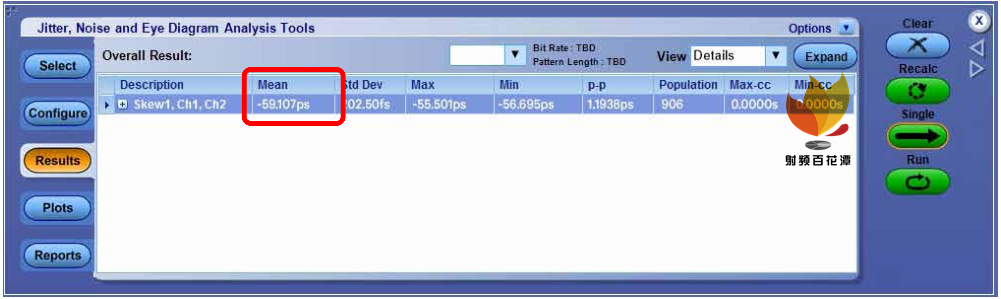

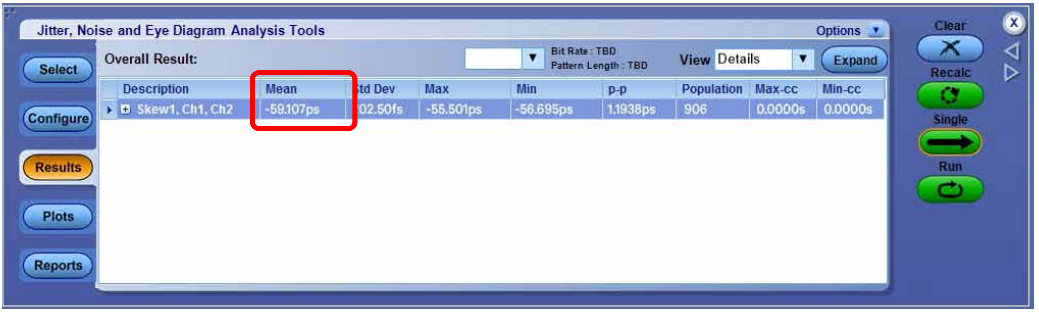

10. 点击右面的 Single 按钮,观查分析运行并结束,记录中间值作为通路间时延测量结果。

( 可选 ) 下面的步骤介绍了在 DUT 和夹具给定通道后怎样搜索最优的 Preset 预置值。

1. 在实时示波器上,下载并安装 SigTest,推荐一直使用最新版 SigTest Phoenix 5.1.02 ( 截止到 2022 年 2 月 )

https://www.intel.com/content/www/us/en/collections/technology/high-speed-io-tools.html?s=Newest

2. 捕获并保存 DUT 提供的每个 Tx Preset 发射机预置值的 Math 数学波形。例如,对 PCIe Gen5,捕获波形 P0,P1, P2, …, P10。

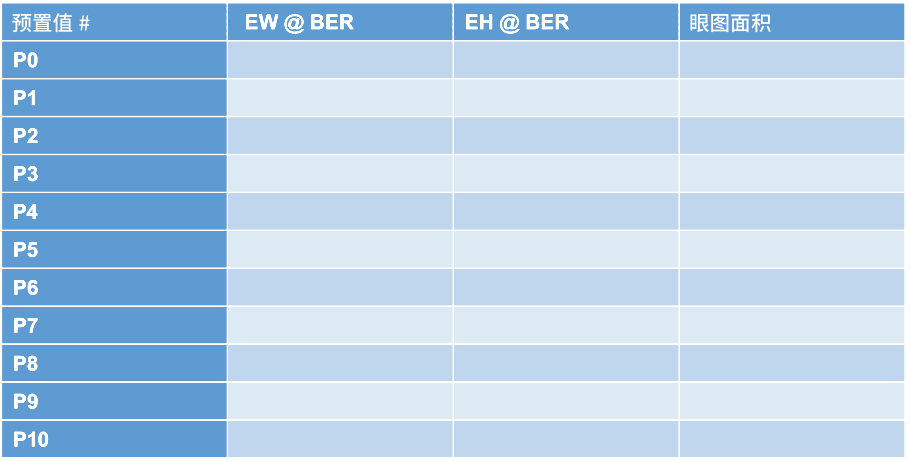

3. 创建下面的表格,记录结果。

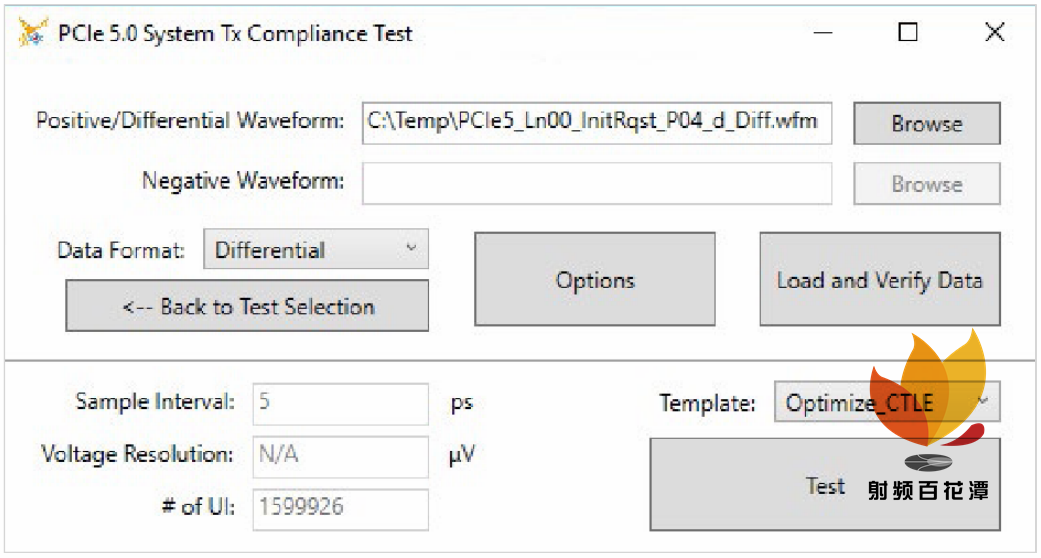

4. 启动 SigTest 5.1.2,使用以下推荐配置,对每个 Tx Preset 发射机预置值波形展开分析。

● Technology: PCIe

● Generation: 5_0

● Test:

- System Board: System

- Add-in Card: Card

● Data Format: Differential

● Template: Optimize_CTLE

5. 在 SigTest Test Results 测试结果的 Overall 整体标签中,针对每个 Tx Preset 发射机预置值,记录 EH @ BER和 EW @ BER 结果。

6. 对每个 Tx Preset 发射机预置值,用 EH * EW 计算出 Eye Area 眼图面积。

7. 找到眼图面积最大的 Tx Preset 发射机预置值,记录预置值编号。

注:根据经验数据,Preset 5、Preset 6、Preset 8、Preset 9 一般是最优的。

附录

一致性切换码型表

推荐一家专业的DC-110G高速及射频PCB设计公司~

声明:

投稿/招聘/推广/宣传 请加微信:15989459034