为应对航空电子系统高速化、高集成度发展方向的要求,印制电路板作为电子系统的基石能够实现良好的信号完整性,以提升电子系统的性能与稳定性,深入分析了导致高速印制电路板出现信号完整性问题的两个主要因素,提出了相应的解决措施,并利用仿真工具Sigrity PowerSI 对高速印制电路板的布线进行仿真优化,最终有效改善了高速PCB 板的信号完整性问题。由此可证明,提出的改善措施可应用至实际工程中,用于解决高速印制电路板的信号完整性问题。

01

概述

02

高速PCB信号完整性问题分析及改善方式

根据定义知:信号完整性问题所研究的是当电子产品工作在高达百兆赫兹甚至G 兆赫兹频率时互连线与数字信号的电压电流波形相互作用时的电气特性怎样影响产品工作性能, 其中信噪比下降或者信号失真属于信号完整性问题中两种常见情况, 噪声问题为文中重点关注的信号完整性问题, 而信号反射、信号串扰是影响信号产生噪声最主要的两个因素。

2.1 信号反射

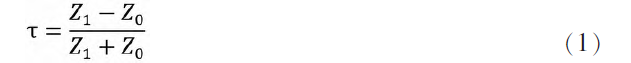

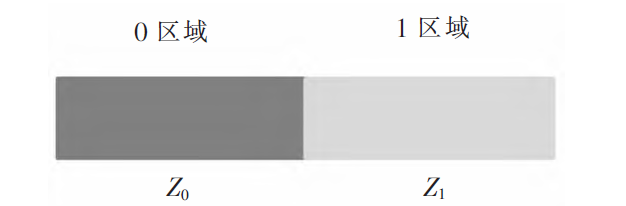

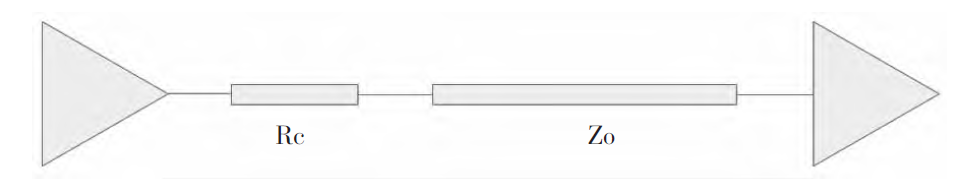

影响电路产生信号反射最直接的因素是信号在互连线上传输过程中出现阻抗不连续的点;在传输信号过程中若发生导线阻抗不连续的情况, 易产生信号反射,如图1 所示。0区域为阻抗分界前, 1区域为阻抗分界后, 假设0区域的阻抗为Z0, 1区域的阻抗为Z1, 则0区域的反射系数τ 为:

图1 阻抗不连续示意框图

图1 阻抗不连续示意框图由上式(1) --反射系数τ 计算公式可知, 当互连线上两相邻区域的阻抗不连续性越差时, 会一定程度上增大反射的信号量。假设一种极端情况:0 区域的阻抗为50Ω, 1 区域的阻抗为0Ω, 其反射系数τ=(0-50)/0+50=-1, 当传输的信号为5V LVTTL 时, 反射电压为-5V, 入射电压与反射电压叠加结果为0V, 末端短路,符合短路点电压为0 的特征。

根据上述分析可知:传输线阻抗不匹配是导致信号反射的根本因素, 为减少因反射带来的信号完整性问题, 提出以下方式减少信号反射问题。

源端串接电阻是通过在源端处附近串接一电阻Rc,用以匹配信号源的阻抗, 其设计示意图如图2 所示。一般这个串接匹配电阻Rc 的阻值都不是很大, 电路中常使用的串接阻值为22Ω 或者33Ω。这种方式是通过限制电流来抑制地弹噪声, 虽然这种电路简单易实现, 但是同时因增大RC 时间常数导致减缓了负载端信号的上升时间, 因此源端串接电阻方式并不十分适用于高速时钟等电路中。

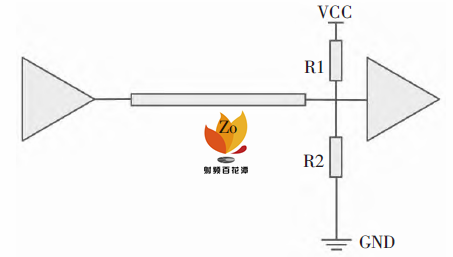

分压器型端接即戴维南端接, 其设计思路如图3 所示。利用上拉电阻R1 和下拉电阻R2 构成端接电阻进行阻抗匹配, 反射的噪声信号借由R1 和R2 吸收。当分压型端接的阻抗Rd(Rd=(R1×R2)/(R1+R2))与传输线阻抗Z0相等时, 将会达到最佳阻抗匹配。

当在系统中使用分压型端接时, 能够完全吸收发送的波从而实现反射信号的消除;假设传输线上无信号,可利用戴维南端接电路设置线路电压, 稳定电路状态,该方法非常适用于总线电路使用。但其始终有直流电流从VCC 端流经至GND 端, 致使匹配电路中一直有直流功耗, 降低了系统内噪声容限。

以上两种方式皆是通过阻抗匹配的方式降低反射的影响, 两种方法各有优缺点, 在进行高速电路设计时可结合具体情况选择适用的端接电路;当然阻抗匹配方式并不仅仅局限于这两种, 可根据实际情况选择其他合适的方式进行设计。

行业内将印制电路板的信号的走线连接方式利用拓扑结构表征出来, 常见的拓扑结构整体上可分为点对点和多对多的拓扑结构。利用点对点的拓扑结构可便于进行阻抗控制, 但是易造成布线复杂;菊花链拓扑结构多数情况下用于负载多的总线系统, 该结构优点在于在占用较小布线空间的基础上实现单一阻抗匹配, 但是其布线长度受限;多负载系统另一种常用布线方式为星形布线网络, 可实现多负载的信号同步, 但是存在传输线驱动能力不足的问题。因此在进行PCB 布局布线时, 尤其是关键信号, 应该先利用软件进行信号完整性分析来判断使用哪种拓扑结构来保证信号与印制电路板的质量。

2.2 信号串扰

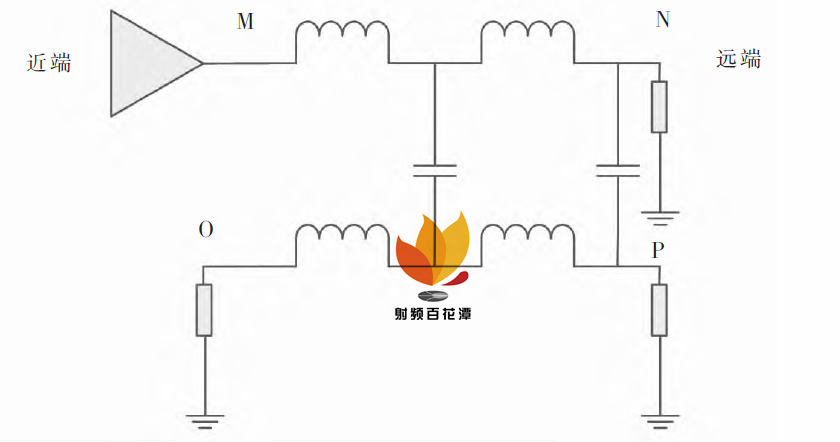

根据电磁感应定律可知:当导线上有电信号流经时, 会在导线周围存在变化的电磁场, 而这磁场会在与此导线相邻处耦合出噪声信号, 产生信号串扰。当这磁场变化愈强时, 产生的噪声信号愈强, 即信号串扰情况加重。图4 为理想状态下导线间串扰示意图, 将下图中MN 段导线为动态线, 即电信号在MN 段传输, 方向为M 点至N 点;OP 段导线为静态线, 当电信号传输时,会在OP 段耦合出噪声信号, 该噪声信号会进一步干扰其他正常电路。当流经MN 段信号趋于平稳直到变成直流信号时, 在OP 段耦合出的噪声信号便会减弱直至消失;由此可知信号的跳变是导致串扰产生的关键因素,电流变化愈大愈快, 在静态线上耦合出的噪声也愈大。

图4 理想状态下导线间串扰示意图

信号串扰对高速印制电路板的影响主要表现形式为信号误触发。信号误触发是指在高速数字电路中, 若串扰噪声通过耦合在被干扰线路与信号接收端产生一个瞬时噪声脉冲信号, 假设该脉冲信号的幅值大于接收端的阈值, 则会产生不受控的触发信号, 有可能导致后级电路的逻辑控制功能混乱。

通过前期查阅资料以及仿真分析得知:减小串扰的有效措施是减小干扰源与被干扰对象之间的耦合, 通过增大传输线间距以及减小平行线走线长度能够有效避免因耦合产生的信号串扰问题。因此, 根据分析结果主要利用以下几种方法来抑制信号串扰:

在满足印制电路板布线布局空间要求前提下,适当增大传输线走线间距, 尽量保证走线间距符合“3W” 原则。

进行多层板叠层结构设计时, 尽可能减小信号层与GND 层间的高度, 前提是满足阻抗要求。

借助前文提及的端接方式, 进行阻抗匹配设计, 有效消除信号反射, 从而削弱信号串扰的影响。

印制电路板布线时, 尽可能避免使用过长的平行线。

在进行电路原理设计时, 尽可能在满足时序要求的情况下选择转换速率较慢的电子元器件, 通过降低电磁场转换速率来抑制信号串扰。

由于物理上的限制印制电路板的表层走线仅有一个参考平面, 会无形中使表层走线的耦合大于内层走线, 因此在设计PCB 时应该尽量保证在内层完成对串扰噪声敏感的信号传输线布线。

03

试验验证

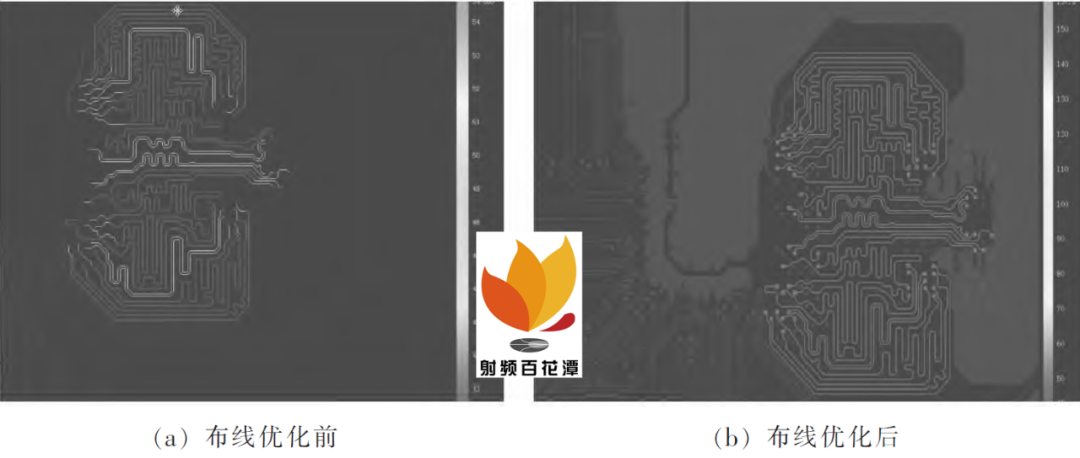

选取一款基于DDR4 的10 层印制电路板的布线进行仿真分析与设计优化, 该DDR4 内存工作频率为2.4GHz,工作电压为1.2V;仿真分析软件选用Cadence 公司的Sigrity PowerSI 组件对DDR4 布线进行阻抗仿真分析。将选取的10 层印制电路板文件导入PowerSI 中进行阻抗分析, 选取DDR 部分数据总线进行演示, 仿真结果如图5 (a) 所示。用颜色深浅来区分阻抗值, 如图5(a)中右侧所示, 例如(40-50)Ω 为蓝色, (120-130)Ω 为黄色;由图5(a)可看出优化前PCB 走线的阻抗不连续,易产生信号反射等问题。利用提及的优化措施对PCB重新进行布线后再次仿真, 结果如图5 (b) 所示。根据仿真结果可看出, 优化后走线的阻抗连续性明显优于优化前的。因此根据试验结果可得出利用提出的改进措施能够有效改善信号完整性问题, 提升印制电路板质量。

04

结语

信号反射与信号串扰是影响高速印制电路板信号完整性的主要原因, 对产生这两个现象的原因进行深入剖析, 依据分析结果提出相应的解决措施并将改善方式应用于某款高速印制电路板设计工作中;利用仿真软件对电路的信号完整性进行仿真验证, 通过实验结果可得出提及的措施能够有效改善信号完整性问题, 保障高速印制电路板信号的质量, 提升电子系统的稳定性, 为高速印制电路板设计行业提供新的设计思路。

作者:苟辉,汪忠林,李坚

来源:数据库与信息管理

精彩推荐

声明:

投稿/招聘/推广/宣传 请加微信:15989459034