电子设计自动化(Electronic Design Automation,EDA)工具是指包括功能设计、逻辑综合、物理设计、仿真验证等一整套自动化芯片设计流程的计算机辅助设计软件。EDA 作为集成电路产业链的战略基础支柱之一,积极促进芯片行业的技术革新,极大提升半导体产业效率。

从市场角度,随着汽车、工业、医疗、教育等应用领域需求的爆发,数字经济的快速发展为集成电路产业提供了非常广阔的市场、非常丰富的应用场景。集成电路设计工具正是这一庞大产业的底层关键技术,政府的高瞻远瞩与庞大的市场空间,为中国EDA的发展带来前所未有的发展机遇。

一、高光时刻

1、全国EDA领域唯一一家国家级工程研究中心落户华大九天

2022年1月,国家发展和改革委员会公布了纳入新序列管理的国家工程研究中心名单,以华大九天作为依托单位的EDA国家工程研究中心(原大规模集成电路CAD工程研究中心)顺利通过了优化整合评价,正式纳入新序列管理,成为全国EDA领域唯一一家国家级工程研究中心。

未来,EDA国家工程研究中心将落实国家创新驱动发展战略,创新体制机制,统筹协调资源,强化产学研深度融合,以集成电路设计、制造、封测等产业链需求为导向,聚焦集成电路EDA关键核心技术研究,推动技术成果产业化,致力于研发面向集成电路设计、制造、封测的全流程EDA工具系统,构建国内EDA完整产业链,解决EDA核心技术受制于人的难题,为我国集成电路产业的持续健康发展提供支撑和保障,提升集成电路产业链、供应链的稳定性和竞争力。

2、南京申报EDA创新中心

在2022世界半导体大会上,江苏省工业和信息化厅副厅长池宇表示,目前,南京EDA创新中心已经向科技部申报,正在审批当中,这是国内第一个报到科技部的EDA创新中心。

3、芯华章成立国内首个EDA企业研究院

2022年7月28日,芯华章宣布成立研究院,这是国内首个EDA企业研究院。中国工程院院士沈昌祥任荣誉院长,中国科学院院士毛军发任首席专家顾问。

在未来3年,芯华章计划投入超亿元人民币全力构筑人才及技术创新战略优势。研究院将以研究下一代EDA2.0方法学与技术为目标,结合技术发展趋势的深入洞察,将密切围绕产业发展需求部署创新研究方向,重点专注于三大前沿领域研究,以更智能易用的下一代EDA2.0,让系统工程师和软件工程师都能参与到芯片设计中来,打造自主可信赖的电子系统创新基石。

4、两位EDA界华人专家入选IEEE FELLOW

2022年11月22日,国际电气和电子工程师协会(IEEE)公布了2023年新晋Fellow名单;有两位华人EDA专家入选。

杨凤如(Fung-Yu Evangeline Young)以表彰对 VLSI 物理设计中电子设计自动化的贡献而入选。杨凤如现在是香港中文大学计算机科学与工程系教授,研究方向包括VLSI电路CAD、算法、组合优化和AI。她的学生在CAD Contest at ICCAD 、ISPD Contest获得多个第一名,博士生陈耿杰获得ACM SRC 2017第一名。

张鸿嘉(Norman Chang)以表彰在 SoC/3DIC 电子设计自动化的物理级签收方面的领先地位而入选。张鸿嘉现在是ANSYS半导体事业部的首席技术专家,研究兴趣包括ADAS可靠性和基于ML的工程应用。

5、北大郭资政获ACM SRC 2022本科生组第一

郭资政是北京大学图灵班大四学生,目前已直博本校集成电路学院,主要研究方向,是EDA中的静态时序分析领域。据郭资政个人主页显示,本科2020年至2022年期间共发表了11论文,其中以一作身份发表8篇,均被EDA领域的国际顶级学术会议和期刊DAC、ICCAD、TCAD等接收。2021年获得SRC@ICCAD本科生组第一。

6、北京大学无锡EDA研究院正式签约

研究院将结合北京大学集成电路学院设计自动化与计算系统系的优势力量,打造自主可控的EDA创新技术,为我国EDA技术的突破和无锡打造世界级集成电路产业集群踔厉奋发、笃行不怠。

北大无锡电子设计自动化研究院将聚焦EDA相关核心技术,推动基础与应用研究、培养和引进科创人才、促进科技成果转化、培育新兴产业,构建集成电路产业转型升级和创新发展的基础科研与产业化推进平台,驱动包括EDA在内的集成电路领域理论研究、技术应用和产业繁荣发展。

7、五家EDA公司入选“中国芯”优秀支撑服务企业

2022年11月17日,第十七届“中国芯”集成电路产业促进大会上,华大九天、概伦电子、芯华章、思尔芯、广立微等五家EDA公司被大会授予“中国芯”优秀支撑服务企业。

“优秀支撑服务企业”主要是用于奖励为中国IC设计公司提供供应保障、在行业自立自强发展过程中发挥了重要作用的企业。

二、IPO+融资

2022年中国内地EDA赛道继续爆发,华大九天和广立微在一周内先后在深圳创业板上市;同时2022年有24家公司完成28次融资,融资金额超过20亿元,融资次数比2021年的43次减少了15次。

2022年7月29日,华大九天在创业板上市,公开发行108,588,354股,发行价为每股32.69元,募集资金总额为35.5亿元。首日开盘价为每股69.05元,首日收盘价为每股75元,首日总市值为407.21亿元

2022年8月5日,广立微在创业板上市,公开发行50,000,000股,发行价为每股58元,募集资金总额为29亿元。首日开盘价为每股122元,首日收盘价为每股148.35元,首日总市值296.70亿元。

2022年11月27日,芯华章宣布完成数亿元B轮融资,由中金资本旗下中电中金基金领投,Mirae Asset (未来资产)、衡庐资产等参投。本轮融资将用于加快实现产品量产、落地和强化专家级技术支持队伍建设,进一步夯实芯华章数字验证全流程服务能力,为数字产业发展提供安全、可靠的高质量工具链。面对新兴技术环境下,系统应用创新在验证规模、效率和完备性等方面提出的巨大挑战,芯华章以终为始,打造了统一底层架构的智V验证平台和全流程数字验证工具链,以自动化、智能化快速迭代为目标,为用户提供从系统级到电路级的敏捷验证方案,助力缩短从芯片到系统的产品上市周期。

2022年10月14日,国微芯宣布完成Pre-A轮融资,由国微集团、立丰投资、亚商资本、布谷天阙投资多家机构共同投资。深圳国微芯科技有限公司,是一家具备国际竞争力的EDA创新企业,公司依托自主可控的“通用服务引擎、统一的层次化数据库、面向对象的规则开发语言”等核心技术优势,搭建了EDA+IP+设计服务一体化平台,向全球芯片设计及制造厂商提供安全、高效、便捷的国产EDA工具系统和服务,主要产品及服务包括:设计后端EDA工具、制造端EDA工具、IP设计、DFT设计服务及后端设计服务等。

2022年7月21日,英诺达完成A轮数千万元融资,此次融资由复星领投,华登国际、红杉宽带等跟投。本轮融资资金将主要用于国产EDA工具的研发,以及进一步扩展EDA产品的云上部署。

2022年6月,合见工软宣布完成超10亿元Pre-A轮融资,由上汽集团旗下尚颀资本、IDG资本、国科投资、中国汽车芯片联盟、斐翔资本、广汽资本等多家机构共同投资,老股东武岳峰科创、木澜投资等持续加注。

2022年2月,行芯科技宣布完成超亿元B轮融资,由中芯聚源领投、华业天成资本等机构参与投资,所募集资金将用于加速打造先进工艺工具链的研发和产品迭代,持续吸引海内外优秀行业人才加盟。行芯作为高起点、具有国际竞争力的EDA企业,专注于芯片物理设计签核与验证领域,提供广泛的、业界领先的产品组合,包括寄生提取、功耗完整性、电迁移、IR压降、可靠性与多物理域等,以解决先进工艺下不断增长的挑战。

2022年1月20日,芯行纪宣布完成数亿元A+轮融资,由今日资本领投,上海科创基金等跟投,本轮融资将用于加大数字实现EDA产品研发投入。芯行纪着力于自主研发新一代数字芯片实现EDA技术和提供高端数字芯片设计解决方案。

2022年1月5日,芯华章宣布完成数亿元Pre-B+轮融资,由国家制造业转型升级基金旗下的国开制造业转型升级基金领投。本轮融资将加大产品研发投入,进一步夯实芯华章在国产验证EDA领域的领军地位,并加快新一代EDA的下一阶段研究及技术创新。

三、走出国门,拥抱世界

继华大九天、鸿芯微纳、概伦电子、芯和半导体、行芯科技成为三星半导体先进制造生态系统SAFE(Samsung Advanced Foundry Ecosystem)之EDA生态系统合作伙伴后,2022年广立微和阿卡思成为SAFE-EDA生态系统合作伙伴,至此中国大陆有7家EDA公司成为三星SAFE-EDA生态系统合作伙伴。

广立微在招股说明书中提到,2015 年成功进入三星电子供应体系,持续向其销售 SmtCell、ATComplier、DataExp、ICSpider等产品;并达成深度合作关系。

四、国际竞赛连续获奖

Contest@ISPD 2022中,西安电子科技大学和鸿芯微纳联队经过两个月时间的算法设计以及优化方法开发,针对12个测试版图例子实现潜在安全威胁的完全清零,同时将初始设计面积、功耗、速度等综合设计性能提升近一倍,在12个测例点中取得9个第一的好成绩,以综合成绩第一问鼎此次ISPD竞赛第一名。这是中国内地高校首次在该赛事中取得第一名。

图片来源:西电官微

CAD Contest@ICCAD 2022赛题B(3D Placement with D2D Vertical Connections)竞赛中,中国内地队伍包揽前三名,鹏城实验室、东南大学、北京大学和香港中文大学联队分获前三。

Die-to-Die (D2D)技术是当前被使用得最广泛的 Chiplet 技术之一,是未来突破3D 芯片设计的关键技术,其可以带来更高的良率、更好的时序、更低的成本等。而布局是物理设计中极其重要的一环,单元位置摆放的好坏在很大程度上直接影响芯片的 PPA(Performance、Power、Area)。赛题要求参赛队伍在考虑上下层不同工艺、层利用率、混合键合端子数量和间距约束等诸多复杂约束的基础上,将网表划分成两部分,并确定每个单元在所属层中的具体位置,使得走线的总长度最短。解决该问题对提升 3D 芯片设计质量有关键的提升。

图片来源:李兴权教授

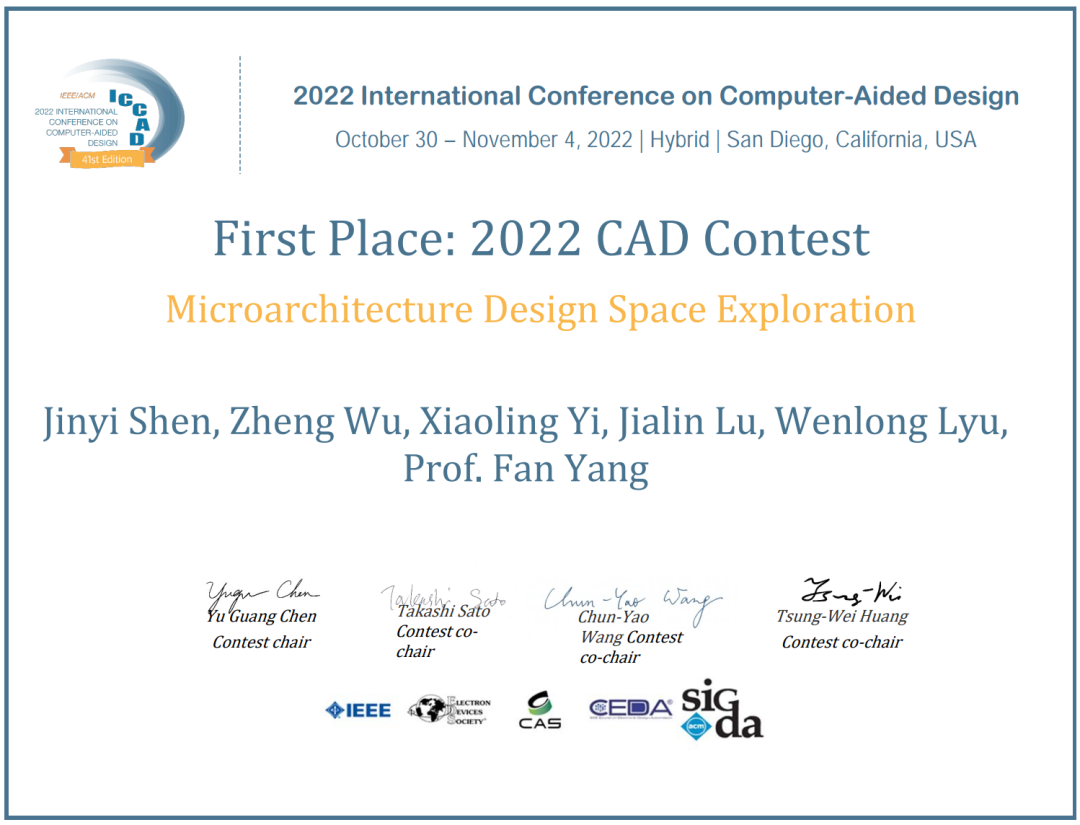

图片来源:李兴权教授CAD Contest@ICCAD 2022赛题C(Microarchitecture Design Space Exploration)竞赛中,复旦大学和诺亚方舟联队获第一名。

图片来源:杨帆教授

图片来源:杨帆教授

向所有获奖成员致敬!

Contest@ISPD 2022第一名:西电-鸿芯微纳联队(汤正光,郭广鑫,李本正;指导老师:游海龙、史江一)

CAD Contest@ICCAD 2022赛题B第一名:鹏城实验室(陈仕健,赵雪岩,李江考,邱奕杭;指导老师:李兴权、黄志鹏)

CAD Contest@ICCAD 2022赛题C第一名:复旦大学和诺亚方舟联队(沈金翼,吴峥,易晓玲,路家林,吕文龙;指导老师:杨帆)

CAD Contest@ICCAD 2022赛题B第二名:东南大学(梅扬杰、申福恒、施跃剑、刘鸿,指导老师:朱自然、杨军)

CAD Contest@ICCAD 2022赛题B第三名:香港中文大学-北京大学联队(Peiyu Liao; Yuxuan Zhao; Dawei Guo; Shuo Yin;指导老师:林亦波,余备)

五、集成电路EDA设计精英挑战赛

2022年集成电路EDA设计精英挑战赛围绕“集成电路设计方法学创新”及“先进设计方法学在集成电路设计中的应用”两个核心关注点设置赛题,继续以产学深度融合为主要运作方式,打造高水平的命题型、开放型专业赛事。鼓励命题企业在重点问题领域持续命题、持续深化、持续创新,从而加深创新深度,实现核心技术领域突破。

今年大赛共有九道赛题,分别是:动态组网迭代划分算法设计(思尔芯)、Verilog中case功能的综合优化(安路科技+鸿芯微纳)、高位宽运算电路的逻辑等价性验证(海思)、多实例化分块布图下的顶层布线(新思)、数字集成电路动态功耗优化策略分析与评估(芯华章)、大规模电源地网络瞬态仿真的分布式并行加速(比昂芯)、感知物理信息的智能化时序估算模型(行芯)、AI-Based的智能版图拼接(华大九天)、面向TCAD仿真的通用器件模型算法和实现(概伦电子)。

今年大赛共有来自清华大学、北京大学、东南大学、香港中文大学、南京邮电大学、美国加州大学洛杉矶分校等国内外高校,以及北京微电子技术研究所等科研院所,共计81个单位的457支队伍,1096位学生参赛。其中,博士、硕士队伍占比达80%。

从集成电路EDA设计精英挑战赛举办以来,就一直鼓励参赛学生在EDA领域开展学术研究及探索,在大赛赛题的基础上持续深入钻研。继2021年的5篇之后,2022年有6篇赛题成果衍生的论文被 SCI/EI/中文核心学术期刊或者国际学术会议录用,

令人高兴的是,28所示范性微电子学院今年首次全部组队参赛,27所获批增列集成电路一级学科的高校有26所组队参赛,这也说明大赛越来越受高校重视,也同时表明高校和学子对EDA的重视。

如果能够升格为国赛,会有更多高校加入。

六、整合并购

回看全球EDA发展史,收购是快速增长的通道。中国EDA产业发展必将经历由点到面的突破,继而是形成全流程工具,收购整合将是必由之路。

1、芯华章收购瞬曜电子

2022年9月,芯华章宣布对瞬曜电子进行核心技术整合,将其超大规模软件仿真技术融入芯华章智V验证平台,丰富其系统级验证产品组合,巩固芯华章敏捷验证方案。同时,瞬曜电子创始人傅勇正式加入芯华章并出任首席技术官,将带领研发团队研发出更多具有竞争优势的数字验证EDA产品。

2、华大九天收购芯達科技

2022年10月18日,EDA公司华大九天发布公告称,拟通过全资子公司深圳华大九天科技有限公司以1000万美元现金收购芯達芯片科技有限公司100%股权,并签署了相关收购协议。据悉,芯達科技从事存储器/IP特征化提取工具的开发,该工具是数字设计和晶圆制造领域的关键环节工具之一。

3、日观芯设收购芯云微

2022年12月,日观芯设宣布收购成都芯云微电子有限公司,并进行核心技术整合,并购金额没有披露。日观芯设表示,芯云微电子的产品技术与公司现有产品具有互补性和协同效应,可以提升物理验证以及EMIR分析研发团队的技术水平,有助于公司不断丰富EDA产品,完善签核工具全链条解决方案,符合公司的发展战略。

七、换标识

2022年7月,鸿芯微纳启用了新标识。

八、新品发布

芯片行业正在经历一个技术进步和创新浪潮的复兴时期。人工智能、5G、自动驾驶等新兴领域技术的不断发展对芯片设计带来全新的挑战,包括工艺要求提升、丰富的应用场景、整体设计规模以及成本等。

EDA工具进入2.0时代,其未来的发展着重在两个大的方向,一是应用目前丰富的算力,提高并行和分布式处理能力,提升设计效率;二是更多的应用AI技术,促进设计的探索自动化,减少可替代的人工努力,解放工程师资源到更具创造性的工作。

近年来EDA公司开始推出用于芯片自主设计的智能化软件,能够在芯片设计的巨大求解空间里搜索优化目标,不仅能够大规模扩展了对芯片设计流程选项的探索,还可以自主执行次要决策,帮助芯片设计团队以专家级水平进行操作,并大幅提高整体生产力,从而在芯片设计领域掀起新一轮革命。

1、芯华章(XEPIC)

芯片验证场景日益复杂,从单纯的功能验证到今天面对整个系统级、场景级的验证;另一方面,面对激烈的市场竞争,芯片集成规模不断扩大,研发周期却不断缩短,验证的重要性日益突出。为有效提高SoC芯片的设计和验证效率,降低芯片设计成本,芯华章在2022年发布两款新产品,加速芯片设计创新:

2022年5月11日,芯华章发布基于创新架构的数字验证调试系统昭晓Fusion Debug® 。该系统基于芯华章自主开发的调试数据库和开放接口,可兼容产业现有解决方案,提供完善的生态支持,并具备易用性、高性能等特点,能够帮助工程师简化困难的调试任务,有效解决难度不断上升的设计和验证挑战。昭晓Fusion Debug® 采用完全自研的高性能数字波形格式XEDB。该波形格式借助创新的数据格式和架构,具备高性能、高容量、高波形压缩比等特点,其提供的高效编码和压缩方案,在实际测试中可以带来比国际主流数字波形格式超8倍的压缩率。与其它商业波形格式相比,XEDB的读写速度快至3倍,并支持分布式架构,可充分利用多台机器的物理资源来提升整体系统的性能,实测中表现出的波形写入速度可以比单机模式提高5倍以上,这对复杂的软硬件协同验证与调试至关重要。

2022年12月2日,芯华章举办以“突破边界的演进共生”的主题的芯华章生态及产品发布会,正式发布了旗下第六款新产品-高性能FPGA双模验证系统桦捷HuaPro® P2E,以独特的双模式满足系统调试和软件开发两方面的需求,解决了原型验证与硬件仿真两种验证工具的融合平衡难题,是硬件验证系统的一次重大突破性创新,将极大助力软硬件协同开发,赋能大规模复杂系统应用创新。桦捷HuaPro® P2E是桦捷HuaPro® P1的延续,同时P2E也赋予了另一层涵义,P代表原型验证(Prototype Verification),E代表硬件仿真(Emulation),P2E!据悉,桦捷HuaPro® P2E系统包含自动综合、智能分割、优化实现,深度调试、无限量、任意深度的信号波形采集、动态触发、内存加载和读取等数十项技术专利。

2、思尔芯(S2C)

2022年6月28日,思尔芯面向全球客户正式发布芯神瞳自动原型编译软件Player Pro-7(PPro-7)。新版本针对大规模芯片设计提供了有效的解决方案,拥有更高的编译效率和更好的分割性能。为高密原型验证系统逻辑矩阵LX的客户提供更佳的操作体验,并大幅提高大型SoC验证的效率。PPro-7三大优势解决大规模芯片设计痛点:对大规模 SoC 设计进行 RTL 级分割,缩短设计的综合时间;提供系统级时序分析,快速预估系统性能,优化时序策略;支持SerDes的TDM模式,提升工作效率。

2022年9月28日,思尔芯(S2C)发布了云化EDA工具:Neuro云管理软件。软件成熟,已得客户验证,可长效保护客户的云端验证环境。它可以协助用户将其分散在全球的原型验证资源进行云端虚拟化,工程师几分钟内即可完成验证环境的部署,快速访问其数据中心、实验室或机房内的原型验证资源和CPU集群算力资源,实现用户、CPU算力、原型验证、虚机/容器等资源的集中管理,并最大化用户的投资回报率(ROI)。

3、华大九天(Empyrean)

2022年7月13日,华大九天在DAC2022会议期间隆重发布了一款高性能晶体管级电源完整性分析工具Empyrean Patron®。该工具聚焦于模拟芯片的电源完整性检查,可高效地提供精准、全面、可靠的EM/IR分析数据及多种EM/IR检查报告。Empyrean Patron®的推出,是华大九天模拟电路仿真系列产品家族的重要补充,更迎合了集成电路设计者的迫切需求,成为业界EM/IR分析解决方案的“破局者”。

Empyrean Patron®作为一款晶体管级电源完整性分析工具,主要拥有动态EM/IR、自热效应和多状态EM/IR分析能力,工具轻量化且快速显示的可视化界面支持版图反标功能,轻松配置,简单易用。Patron由业界认可的华大九天SPICE仿真引擎Empyrean ALPS®驱动,受智能矩阵求解器(SMS)技术加持,速度相比传统工具可实现2倍以上加速;面对高精度EM/IR分析,直接求解模式确保无精度损失;独立研制的迭代求解模式可以提供更佳的仿真能力,实现高性能EM/IR分析。

4、芯行纪(XTIMES-DA)

2022年8月,芯行纪宣布推出首款完全自主研发的数字实现EDA产品AmazeFP智能布局规划工具,将机器学习技术应用于布局规划引擎,在兼顾性能、功耗和面积(PPA)的同时,提供了高度智能的拥塞感知、便捷的数据流分析和宏单元自动整理对齐功能,有效解决当前数字芯片在后端设计的布局规划节点面临的对经验依赖度高、手工耗时长、数据流分析手段单一、设计问题依赖后期定位导致的收敛性差等难题。

AmazeFP采用的机器学习技术可快速获取高质量的宏单元布局思路,提供给用户初步布局规划;内置的数据流导向引擎,可智能规划宏单元摆放,加速宏单元关键路径的时序收敛;拥塞感知功能可准确预测拥塞度并调整宏单元位置,实现高效且有针对性的全局优化;宏单元自动整理对齐功能可以动态地根据所选的宏单元自动生成网格化窗口,极大地节省用户规整对齐宏单元的时间。

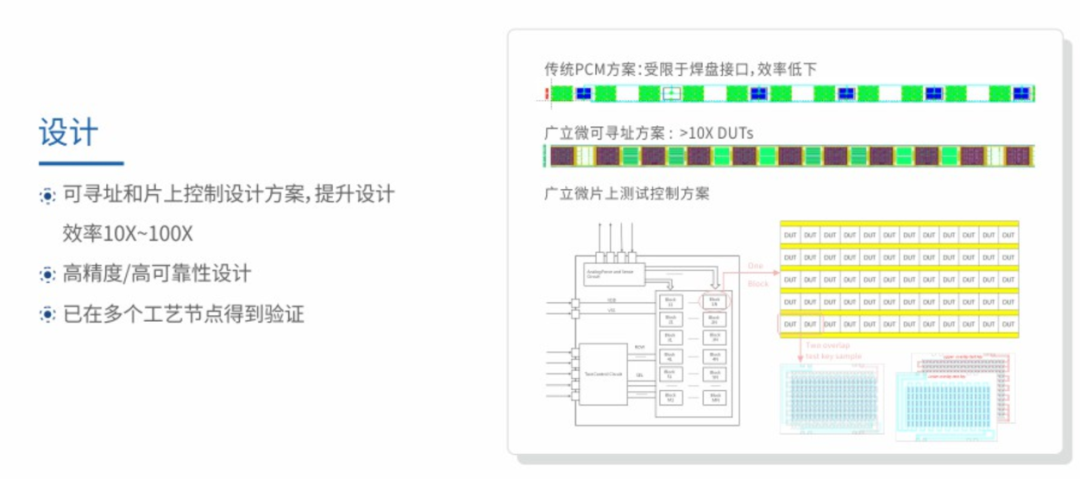

5、广立微(Semitronix)

成品率(Yield)一直是集成电路制造的关键指标,反映了生产工艺的水平和成熟度,同时也是优化工艺的依据。广立微专注于集成电路的智能制造,近期推出了新的制造类EDA产品,丰富了成品率提升的生态,为芯片成品率保驾护航:

超高密度成品率监控划片槽方High Density Yield Scribeline(HDYS)

超高密度成品率监控划片槽方案 (HDYS )进一步完善了广立微独有的可寻址EDA技术,能够在量产晶圆的狭小划片槽里,自动化得设计和摆放大量的电性测试结构。广立微推出的创新监控结构包括:在生产线中所关注的电学套刻对准监控(E-Overlay)、Module监控参数、工艺窗口量化、光罩之间的变异监控等。

高效量产电性监控方案Advanced Process Control Monitor Solution(Adv-PCM)

高效量产电性监控方案(Adv-PCM)在晶圆生产过程中,结合可寻址、高密度阵列的EDA技术,与广立微的WAT测试设备实现了软硬件协同,实现了多维度、多元化的量产监控,确保芯片的成品率、稳定性和可预测性方面优于传统解决方案。

广立微Adv-PCM的EDA设计方案

智能设备监控平台DataExp-FDC

智能设备监控平台(DataExp-FDC),具有数据收集、战略构建、分析和生产监控的主要功能。DataExp-FDC系统与设备和MES建立通讯,收集设备中传感器的原始数据,并从中提取有效表征因子,监控和保证生产工艺的稳定性。同时可与良率分析系统(YMS)结合,通过大数据机器学习和在线量测建模,帮助快速找到成品率问题的根因。

6、概伦电子(PRIMARIUS)

NanoDesigner:提供一个灵活、可扩展的全定制存储和模拟/混合信号IC设计环境,包括原理图编辑、版图编辑和优化及物理验证等功能,同时与概伦电子行业领先的电路仿真器NanoSpice系列引擎集成,为以各类存储器电路、各类模拟电路等为代表的定制类芯片设计提供完整的EDA全流程,从而极大地提升设计效率。

信号完整性分析解决方案NanoSpice SI:提供了快速、精准的信号完整性解决方案,可以解决抖动、串扰、响铃、地面反弹,和由于封装空间缩紧和时钟频率增加而产生的噪声问题。

门级晶体管级混合时序分析解决方案TRASTA:可以自动识别关键路径,使设计师以最高精度分析关键路径。TRASTA 自动识别设计中的特别器件,并利用拓扑结构和沟道连接提取技术产生门级电路,提取的门级单元的时序特性被自动特征化并用于静态时序分析(STA)中。TRASTA 提供了一个内置的STA引擎和支持对寄生进行反标的SPICE网表自动生成功能。

新一代高精度快速波形发生与测量套件FS-Pro PIV:增加短脉冲IV(PIV)技术后,FS-Pro全面而强大的参数测试分析能力极大地加速了半导体器件与工艺的研发和评估进程,并可无缝的与概伦电子低频噪声测试系统9812系列集成,其快速DC测试能力进一步提升了9812系列产品的噪声测试效率。基于在产线测试与科研应用方面的优异表现,FS-Pro全面的测试能力在科研学术界受到了广泛关注和认可,并已被数十所国内外高校及科学研究机构所选用,同时也被众多芯片设计公司、代工厂和IDM公司所釆用。

7、上海立芯(Ledatech)

上海立芯在2022年发布两款商用工具:自动化布图规划工具LePlan和布局及物理优化工具LePlace。两款工具均已通过业内知名客户的验证且获得采购。

数字集成电路自动化布图规划工具LePlan,为国产数字集成电路后端设计全流程EDA工具的破局助力。LePlan较手工布图在整体上有明显的PPA优化优势,效率亦有显著提升。LePlan工具针对性地破解传统手工布图规划难以解决的耗时和收敛性差等多方面难题,提供基于数据流分析和智能探索达到最快收敛的布图规划方案,旨在助力数字电路设计实现更具挑战性的PPA要求。特别地,LePlan还高度融合后端布局布线技术,同时降低集成风险。该工具后续将大规模推向市场,满足更多设计客户的需求。

数字集成电路布局及物理优化工具LePlace,为国内数字芯片物理设计环节最需要突破的布局布线流程工具提供了新的选择。LePlace是一款支持成熟及先进工艺的布局及物理优化工具,基于创新的布局布线技术和物理优化算法,主要用于超大规模集成电路布局,内嵌创新性的拥塞及时序驱动的布局技术,可以满足超大规模复杂设计所需的大容量和高性能要求。

据公司网站介绍,后续将陆续推出时钟树综合工具LeCTS、布线工具LeRoute和逻辑综合工具LeSynth。

8、合见工软(UNIVISTA)

新一代时序驱动(Timing-Driven)的高性能原型验证系统UniVista Advanced Prototyping System(UV APS)升级版集成了先进的时序驱动全流程编译软件APS Compiler,自研的强大前端编译处理引擎,可以快速实现多种类型设计的移植和启动,降低用户初期部署成本;APS Compiler内嵌功能更强大的时序驱动引擎,并通过大范围TDM ratio自动优化求解,面对10亿门以上设计亦能自动化快速实现更卓越的性能,提供了寄存器回读和深度调试等多样化调试手段。

先进封装协同设计检查工具 UniVista Integrator(UVI)的Sign-off级完整功能版,完善了先进封装设计在IC、Package、PCB设计协同的Sign-off功能,支持全面的系统互连一致性检查(System-Level LVS)。

高效易用的数字功能仿真调试工具 UniVista Debugger(UVD)实现了高性能、高容量的架构和关键技术设计,支持智能源代码追踪,可以兼容业界不同的验证工具和方案,同时具有简洁易用的用户界面。

强大灵活的大规模功能验证回归测试管理平台 UniVista Verification Productivity System(VPS)实现了以覆盖率为驱动的自动化数字前端验证流程管理和海量数据管理,它为用户提供了从初始验证计划创建、回归执行、回归数据收集挖掘、智能错误调试、项目追踪到最终覆盖率收敛的完整流程管理与支持。

即插即用的混合原型系统级IP验证方案UniVista Hybrid IPK(HIPK)充分利用了虚拟原型和FPGA原型验证系统的优势,在项目早期就可为用户提供一个软件开发调试以及IP子系统软硬件协同验证的环境,从而加速软硬件验证的收敛。

9、本源量子

2022年4月本源量子发布量子芯片EDA软件本源坤元Origin Unit,实现量子芯片的自动化设计,为推进量子芯片的生产打下基础,力图避免在量子计算机时代重蹈EDA技术受制于人的覆辙。9月推出本源坤元2.0。

本源坤元作为兼容超导和半导体两大体系的我国首个自主开发的量子芯片设计工业软件,实现数据到仿真的EDA全流程、版图自动化设计,进一步实现我国量子芯片的自主研发及产业化生产!

10、鸿芯微纳

鸿芯微纳致力打造完整的全流程集成电路设计国产数字EDA 平台,继2019年推出布局布线工具Aguda®后,2022年推出三大新产品:版图驱动的逻辑综合工具RocSyn®、静态时序签核工具ChimeTime®、功耗签核工具HesVesPower®,进一步完善公司在数字芯片后端设计全流程工具链的布局。

11、国微芯(GWX)

2022年12月,国微芯重磅推出“芯天成”五大系列十四款EDA工具及系统,实现多个行业首创。国微芯成为国内数字EDA设计后端及制造端领域覆盖范围最广,工具布局最全的公司。

“芯天成”系列包括物理验证(版图数据集成、金属填充工具、金属密度检查工具、版图比对工具)、光学邻近矫正工具(基于规则的OPC、基于规则的辅助图形工具)、形式验证(C2RTL等价性验证工具、RTL2Netlist等价性验证工具、FPV 模型检查工具)、SPICE(SPICE仿真器、模拟电路图输入工具、波形显示与电路调试工具)、特征化(特征化提取工具、单元库正确性检查工具)在内的14款工具正式面市。