点击“蓝字”关注我们

欢迎回到最新 RF Data Converter 博客系列。

这次我们将演示 RF Data Converter IP 设计仿真测试激励文件示例。

本篇博文旨在演示其构建方式及其用于实践 IP 的机制。我觉得这部分内容值得讲一讲,因为只要您能够充分理解测试激励文件,就可以将其作为有效的模板来用于将 RF Data Converter IP 构建到自己的仿真设置中。

我并不会细讲这里的所有内容,只是为了演示一下仿真的机制。当然,您也可以自行深入分析测试激励文件 RTL。

您可能已经知道,IP 设计示例随附有完整的测试激励文件。此测试激励文件可在仿真中提供激励生成和采集,用于 ADC 和 DAC 实践。仿真具有内置自检功能,因此它可用于检验您的 IP 设置。

让我们来简单了解下设计测试激励文件示例。

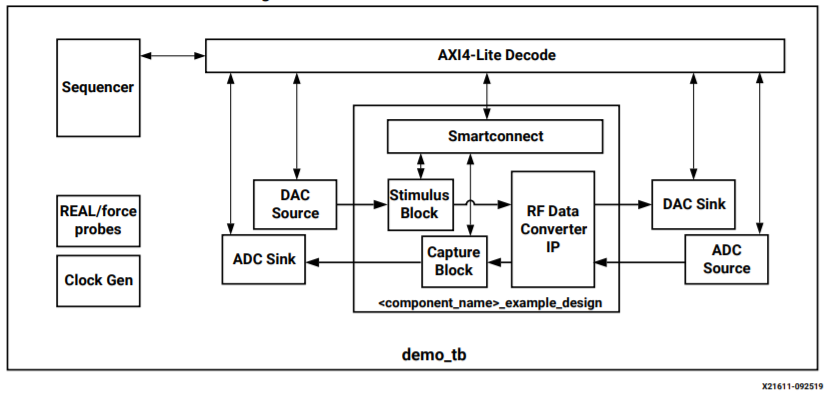

从 IP 设计示例层面上来看,不仅有 IP,还有激励块和采集块(均为大型块 RAM 数组)。

此外还有 1 个 SmartConnect 块用于连接到 IP 的 AXI4-Lite 端口。

因此,测试激励文件需提供的是:

时钟生成,用于设计中的所有时钟。ADC 和 DAC Tile 的输入、AXI 流传输接口和 1 个 AXI4-Lite 接口。

加载激励块或源代码块的方法。

将“实数”信号应用于模拟输入的方法,以及将实数信号从 DAC 转换为数字总线以便检查的方法。

最重要的是,需要 1 个定序器 (sequencer) 用于管理仿真。

检验采集块或接收端 (sink) 块的方法。

让我们来看看测试激励文件。测试激励文件的所有源文件都包含在设计工程示例中的导入 (imports) 目录中。

顶层测试激励文件包含在 demo_tb.sv SystemVerilog 文件中。我们不会逐行详细分析其中所有内容。在此级别只需连接各主要块即可。让我们来看下仿真功能的最重要的部分。

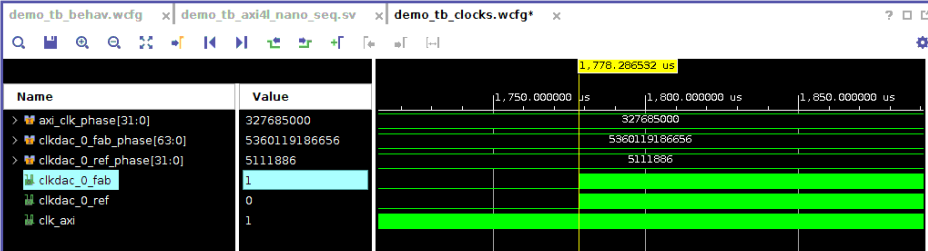

时钟生成

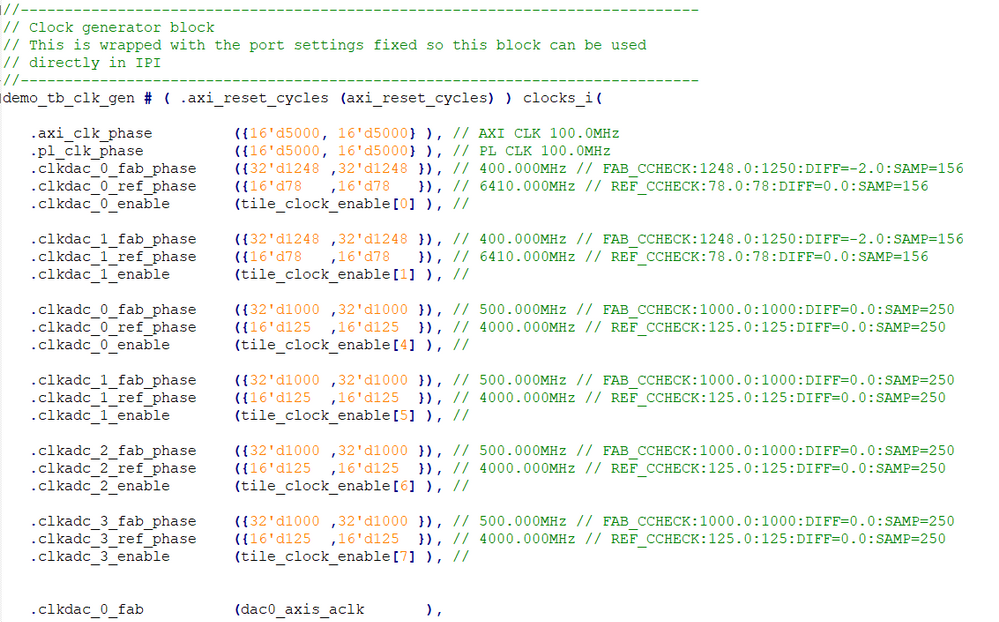

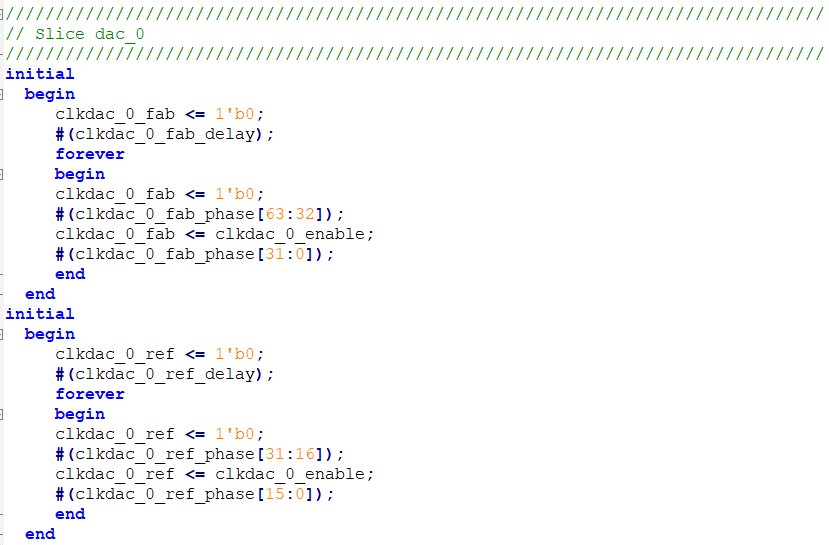

有一个非常简单的模块可用于在仿真中创建所有必要的时钟信号。其中的输入带有_phase后缀,支持用户为时钟设置高低时间。它用于为每个 Tile 和 AXI Stream 时钟创建所期望的频率。

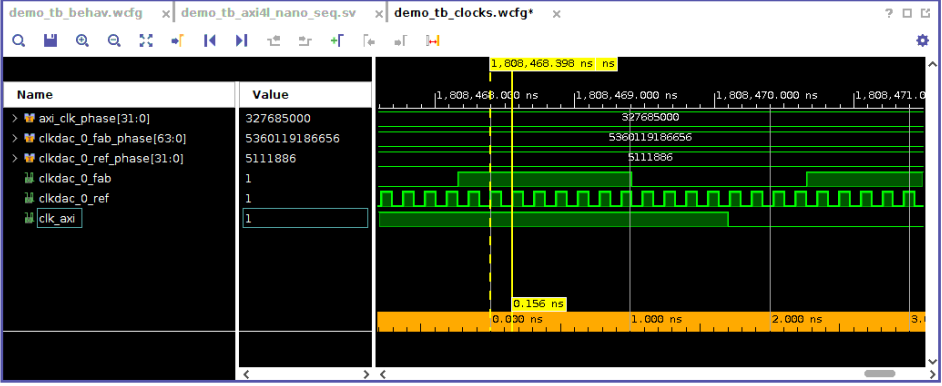

我们可在仿真中对此进行检查,确保它按我们期望的方式运行。

在此情况下可以看到,DAC 采样时钟以 6.4GSPS 运行,而 AXI stream 传输时钟的运行速率为该速率除以 16。

激励生成

在仿真中,ADC 和 DAC 将分别单独处理。在此情况下并不执行环回。

DAC 与 ADC 来源相同。

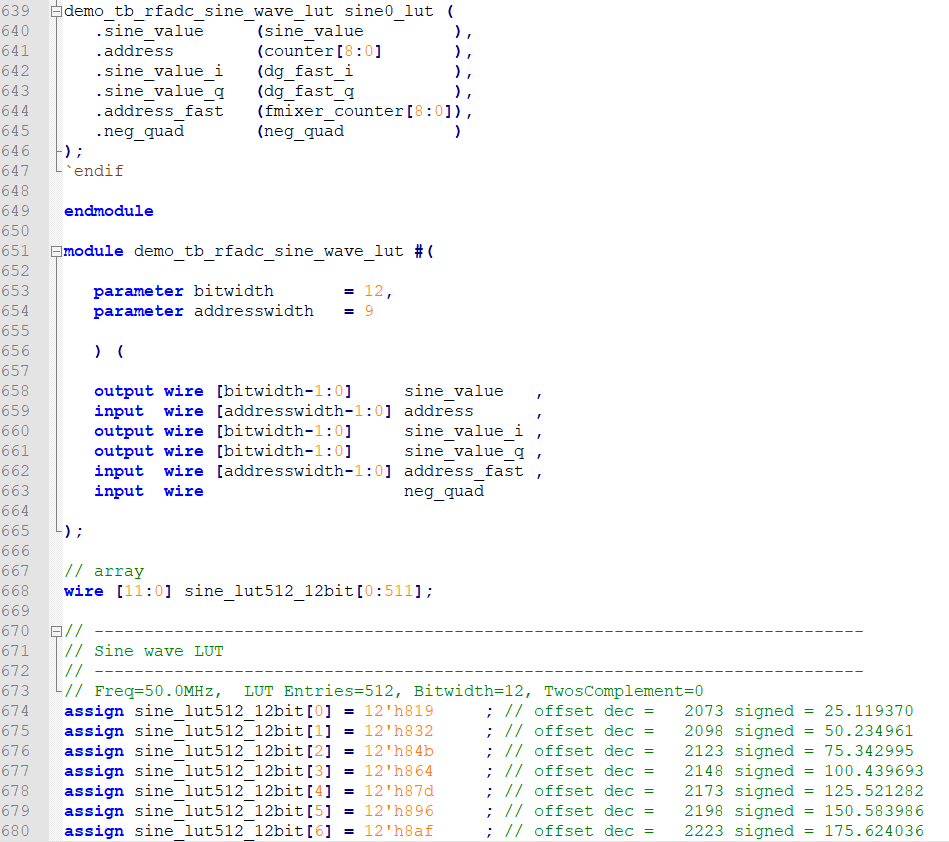

ADC 包含demo_tb_rfadc_data_source.sv,其中包含demo_tb_rfadc_tile_source.sv。在代码中,我们提供的是正弦查找表 (LUT)。在此情况下,将循环此 LUT 并生成正弦波输出。

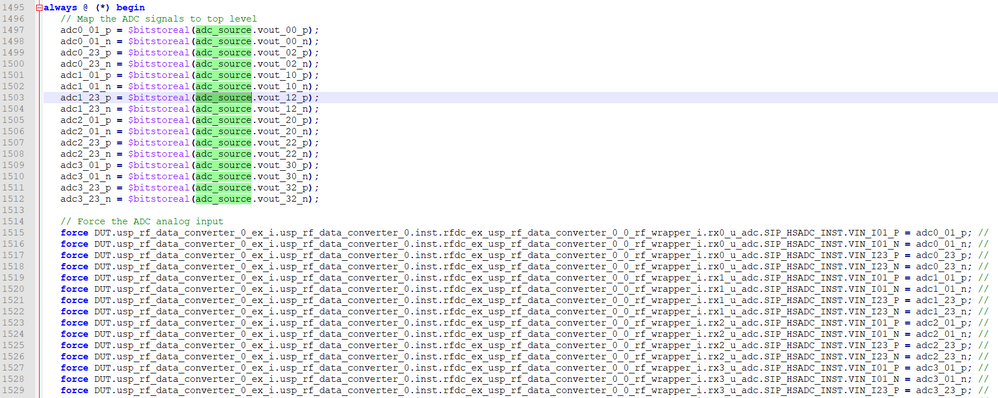

此正弦波将输出到测试激励文件的顶层。我们可将其转换为实数,以便将其强制添加到demo_tb中的 Tile 的 UNISIM 模型层的模拟信号输入中。

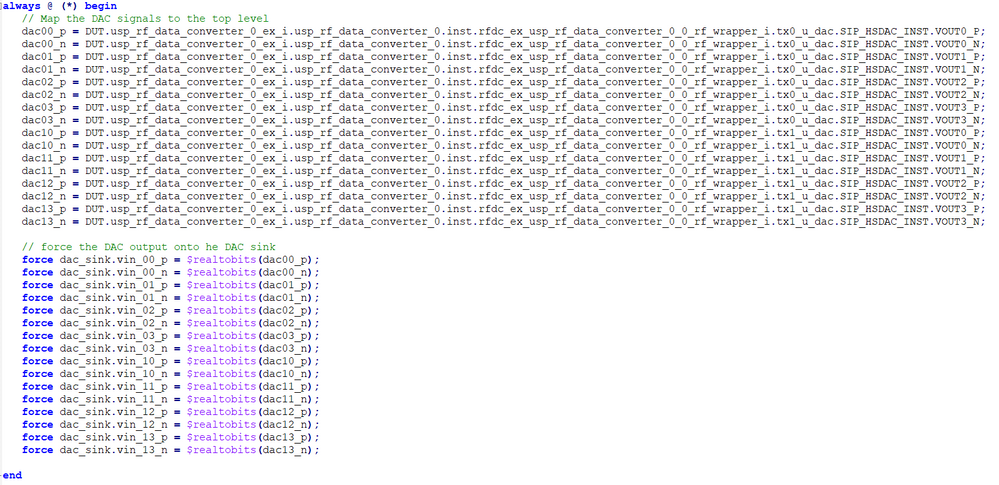

对于 DAC,只需将此数据写入设计示例中的 DAC 源块上的 AXI 接口即可。在demo_tb层级上,我们可将 DAC 模拟信号从实数转换为位数,并将其应用于 DAC 接收端输入。

测试激励文件定序器

鉴于时钟正在运行仿真,并且先前已经讲解过数据源相关内容,因此我们可以继续讲解测试激励文件的主要部分。

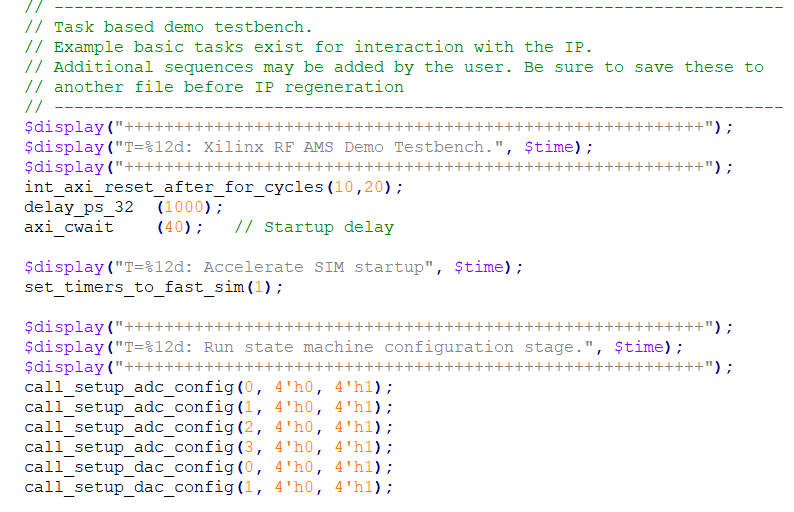

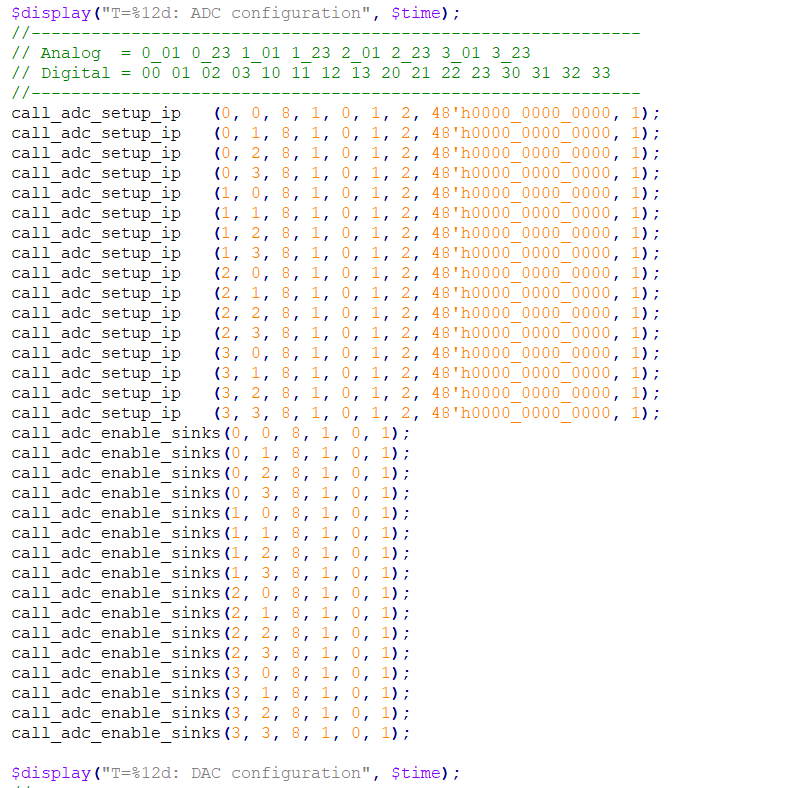

在demo_tb_axi4l_nano_seq.sv文件中可以了解到仿真的设置和控制方式。此文件使用部分 SystemVerilog 任务以便于我们访问 RF 的 Tile,并对其执行部分设置。此外还有其它任务可用来控制仿真。我们将演示仿真的整个过程,并根据需要来探讨这些任务。

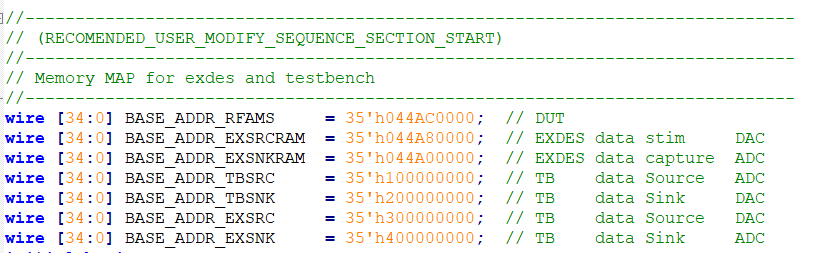

通过观察此文件可以发现,它使用参数化寻址来允许我们处理测试激励文件中 AXI4-Lite 上的各个子块。各项任务将通过这些子块来控制仿真。

定序器 (Sequencer) 首先会对测试激励文件中的所有一切都应用复位。然后它会对 Tile 执行写入以启用仿真加速。这样即可缩短 Tile 的启动时间,因为它可缩短电源微调时间以及 ADC 校准时间。仿真仅允许 Tile 达到 IP 的启动状态机的状态 1。

在此步骤后,它会对 Tile 执行某些设置,然后开始在测试激励文件中开启源端和接收端。它还会开始加载 DAC 源内存。

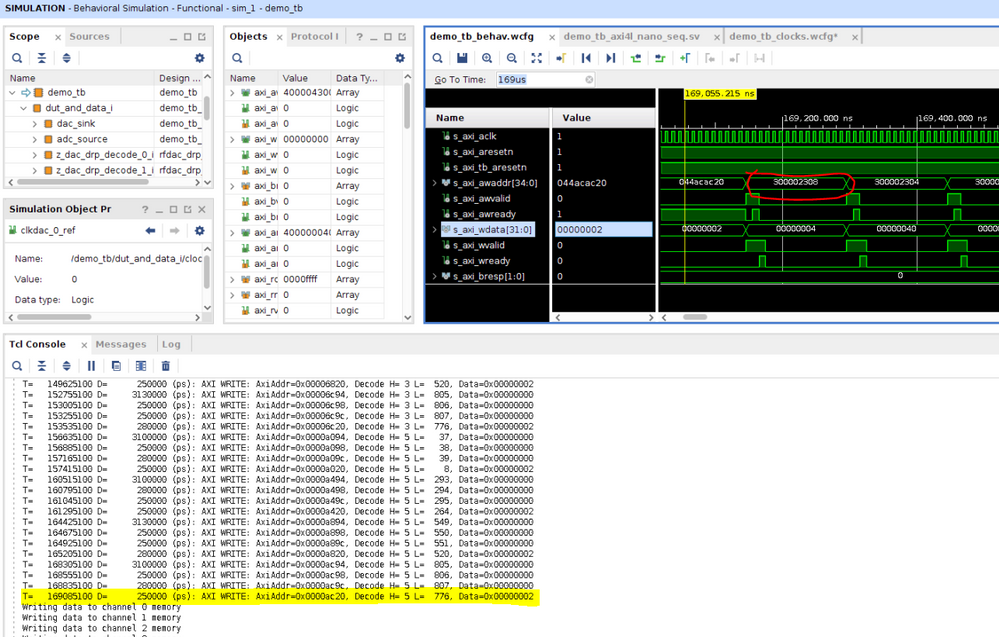

最好在执行每个步骤时都打印仿真时间。这样即可根据需要检查波形。

可以看到,IP 设置完成后,就会于 169us 附近开始写入 DAC 激励数据。DAC 源内存位于基址 0x300000000 处。

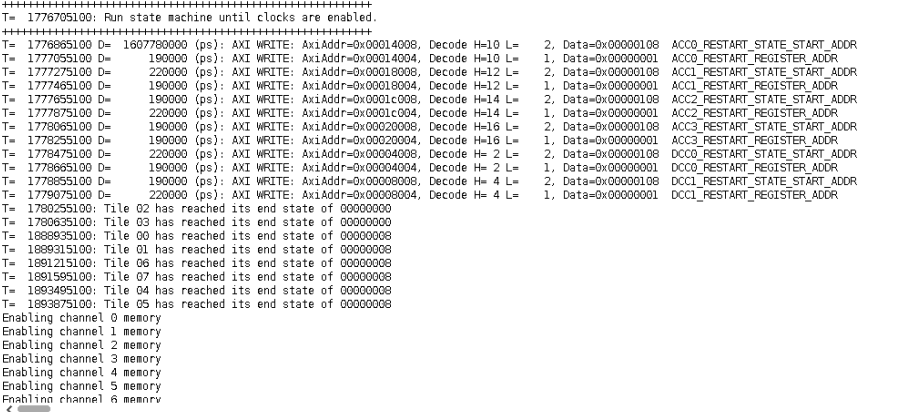

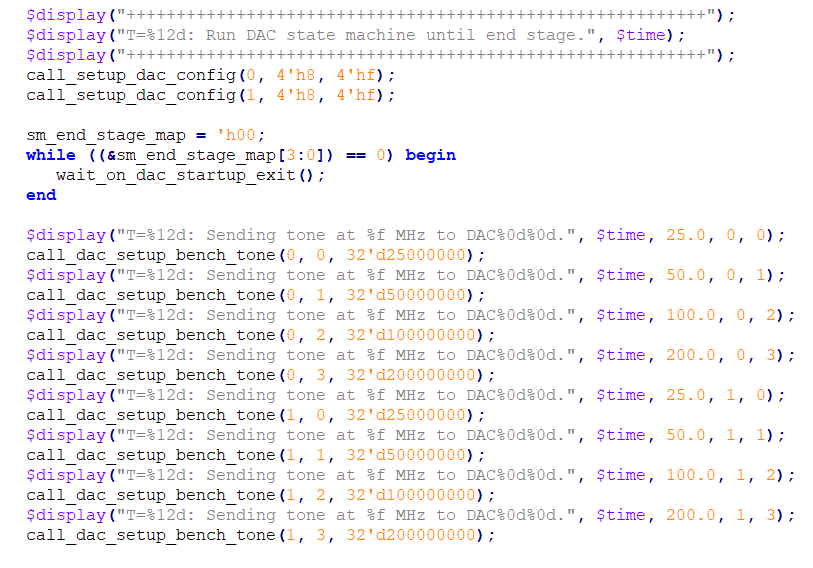

下一步,启动 Tile 时钟,并运行 ADC 和 DAC 直至时钟检测步骤为止。

完成此步骤后,即可启动 DAC 源并运行 DAC,直至启动 FSM 结束为止:

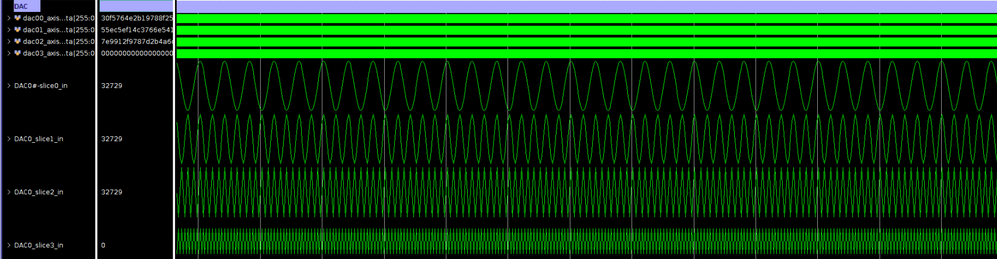

通过观察波形可知,音调已传入,而 DAC 输出总线正在运行。

此处可看到 25Mhz/50Mhz/100Mhz/200Mhz。

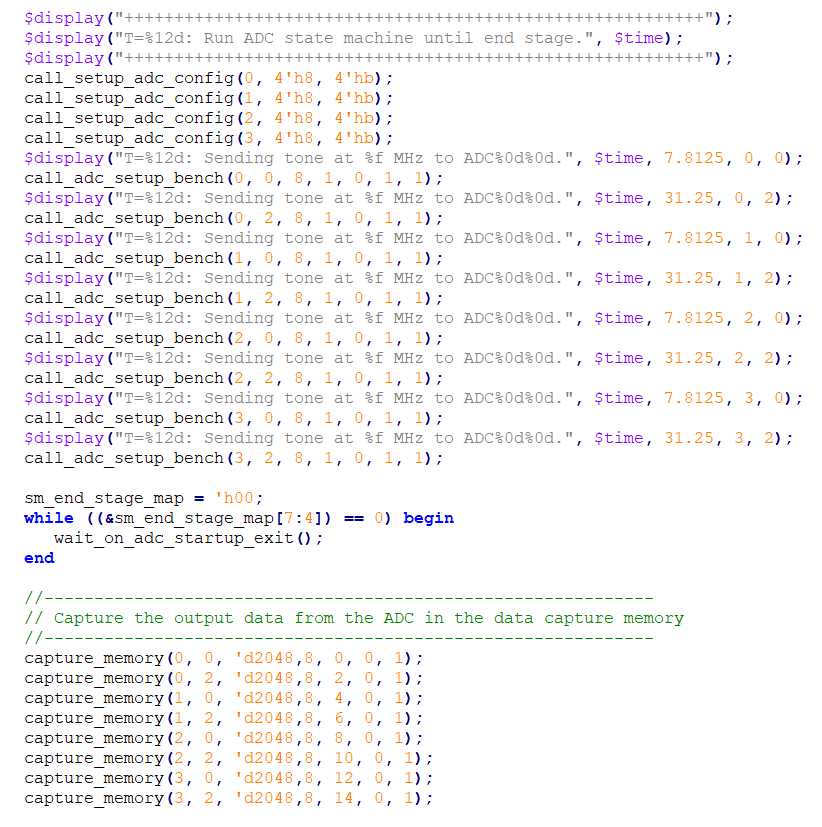

然后,针对 ADC 重复此过程:

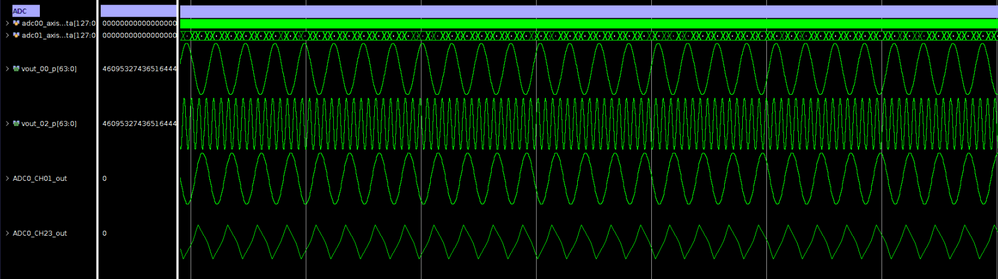

运行后,可在波形中查看结果。在此情况下,vout_00和vout02总线即为仿真中 ADC 源的输出。

我在此处还附上了 AXI Stream 传输的 8 个采样之一的截屏,以显示 ADC 能正常转换单音信号。

数据接收端和检查器

ADC 和 DAC 在demo_tb中具有一组接收端块。

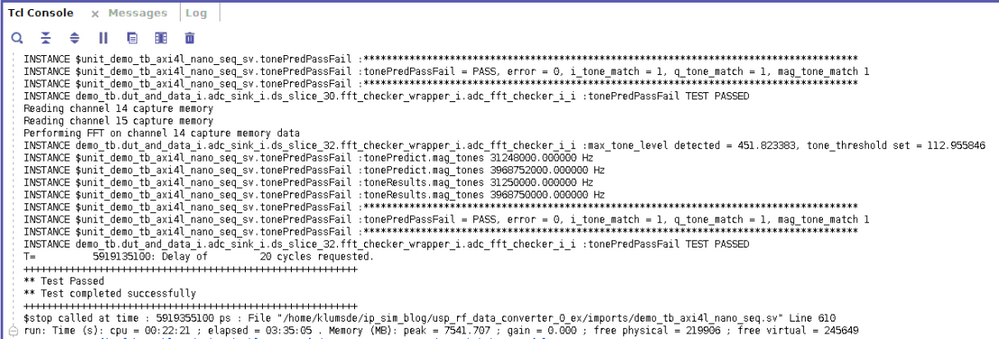

在这些块中,将对数据进行缩放,并且将执行 FFT。这样即可确认信号能以正确方式进行转换。

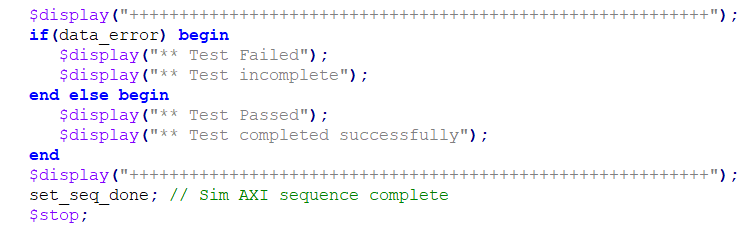

这些块用于管理错误计数器。如果全部正确,那么定序器 (Sequencer) 就会停止仿真。

我希望本篇博文能够帮助您更进一步了解 IP 仿真示例。此外还有很多内容值得分享,但本文应该能够为大家提供一个良好的起点,以便大家了解仿真的工作原理,并且您可能还可以将其中部分技巧用于您自己的仿真测试激励文件。

完。