2022年12月5日(太平洋标准时间),IEDM2022正式开幕。英特尔共奉献了8篇一作,还有和佐治亚理工、加州大学圣塔芭芭拉分校(UCSB)有2篇合作论文。这些论文展示了英特尔在三个关键领域的创新进展,以实现摩尔定律的延续:新的3D混合键合(hybrid bonding)封装技术,无缝集成芯粒;超薄2D材料,可在单个芯片上集成更多晶体管;能效和存储的新可能,以实现更高性能的计算。

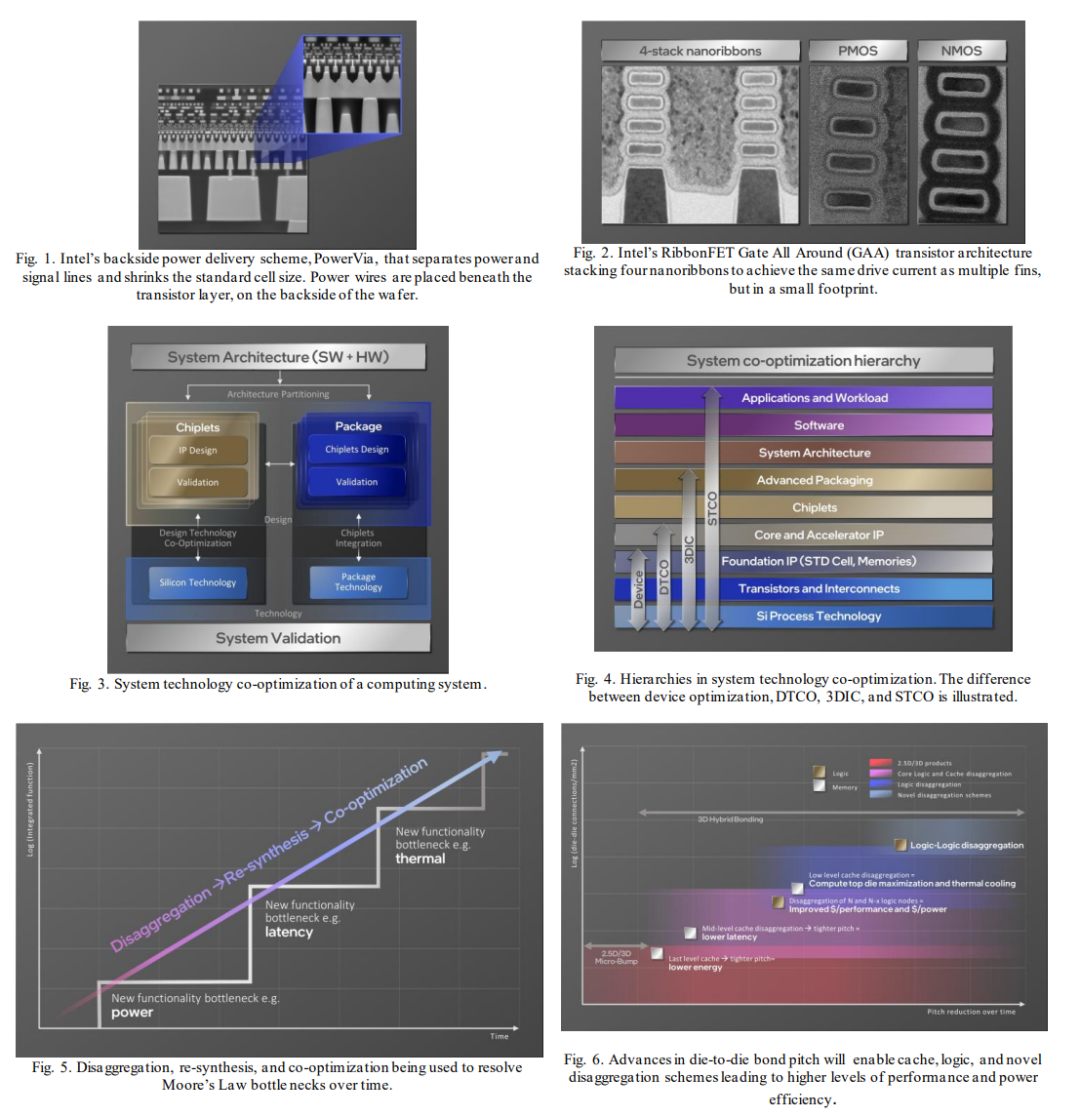

英特尔执行副总裁兼技术开发总经理Ann Kelleher博士作为特邀嘉宾发表开场演讲《庆祝晶体管创新75年,展望摩尔定律创新的演变Celebrating 75 Years of the Transistor A Look at the Evolution of Moore's Law Innovation》。Ann Kelleher博士,75年来,晶体管和集成电路(IC)创新一直是电子设备规模化的基本引擎。他从摩尔定律对满足计算需求至关重要,随着功能集成需求的增加,各种协同优化机会变得普遍。设计技术协同优化(DTCO)已得到利用。系统技术协同优化(STCO)是摩尔定律的下一个主要发展,以进一步推进功能集成。

从Ann Kelleher博士的报告中可以看到,摩尔定律的演变分为两个时代:

首先是晶体管缩放时代:这是经典的“Denard scaling”时代,晶体管的几何收缩提高了功率、性能和面积。1974年,Robert Dennard等人撰写了一篇开创性的论文,描述了晶体管缩放规则,该规则能够同时提高性能、降低功率和持续的密度。Denard scaling被半导体行业采纳,成为未来30年推动摩尔定律的有效路线图,为我们提供了一条可预测的持续晶体管技术改进之路。该时代的重大突破包括沉浸式光刻(immersion lithography)、超薄栅极氧化物、硅晶圆尺寸的变大。

第二个时代是后晶体管缩放时代,该时代有三个创新路径:

一是随着晶体管某些元件的缩放开始达到极限,引入了新的材料和器件结构来继续缩放,包括应变硅(Strain-Si)和HKMG等创新,以及向FinFET的过渡。

二是设计技术协同优化(Design Technology Co-Optimizatio,DTCO)。Ann Kelleher博士在演讲中表示,过去的几年,DTCO带来了一些创新,并解决了互连路由的瓶颈问题,随着密度的增加,更细的互连堆叠设计、EDA布局布线的共同优化继续在每个技术节点上显著提高性能。DTCO是当今维持技术发展的重要部分。

三是系统技术协同优化(System Technology Co-Optimization,STCO),仅优化设备已远远不够,我们需要优化整个系统!

Ann Kelleher博士举了一个STCO的例子,其中小芯片、IP设计和验证是带有工艺技术的DTCO,并与封装、小芯片设计和验证以及软件和硬件架构和验证相结合,以产生一个优化的系统。

设备包括工艺技术、晶体管和互连以及基础IP。DTCO增加了核心和加速器IP和小芯片。STCO进一步增加了高级封装、系统架构、软件和应用程序以及工作量。

同时,Ann Kelleher博士认为创新机会很多:

人:被强调为最重要的,人是创新的驱动力。

缩放Scaling:带状FET,然后是CFET。

互连Scaling:RC延迟、电迁移、光子学。

材料Materials:金属、偶极子、光刻胶、电介质。

图案化EUV,然后是高NA,然后是EUV的多重图案化,最后是高NA。

内存Memory:存内计算、光学、铁电存储,过程中的功耗。

power loss during transfer:芯粒(chiplets/tiles),可靠性

封测:2.5D、3D,EMiB+Foveros=Ponte Vecchio(来自5个工艺节点的47块芯粒),光学。

可靠性:必须评估可靠性、3D封装(电力和热力)的任何变化。

软件–对于交付产品非常重要,在进行STCO时需要考虑软件。

制造:在考虑材料时,考虑到可持续性。

据悉,在封装方面,英特尔将于2023年下半年推出Foveros Direct,与目前的Foveros工艺相比,其密度提高了10倍,同时具有更高的带宽、更低的延迟、更低的功耗和更小的管芯面积。英特尔也在研究可插拔的光互连。

英特尔的长期研究正在致力于:

实现了芯粒的无缝集成,密度和放置灵活性提高了10倍。

超薄材料通过实现2D材料进一步扩展到RibbonFET之外。

使用更节能的存储器(如FeRAM、magento电子器件和硅上GaN)实现能效的新可能性。

总之,Ann Kelleher博士提出了将摩尔定律再延续十年或更长时间的机会和挑战的迷人观点。英特尔显然重新成为领先的技术创新者。