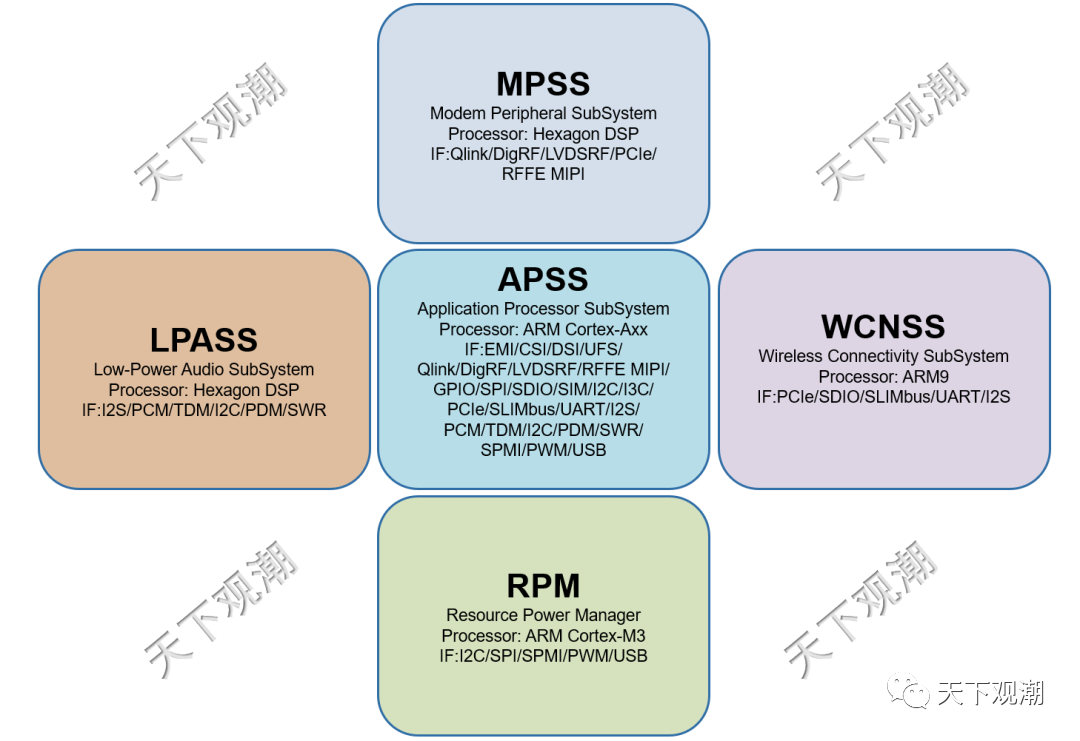

手机SOC可谓集成度最高、功能最全的集成电路。按照高通的分类方法,可以将SOC分为APSS、RPM、MPSS、WCNSS、LPASS五大子系统。

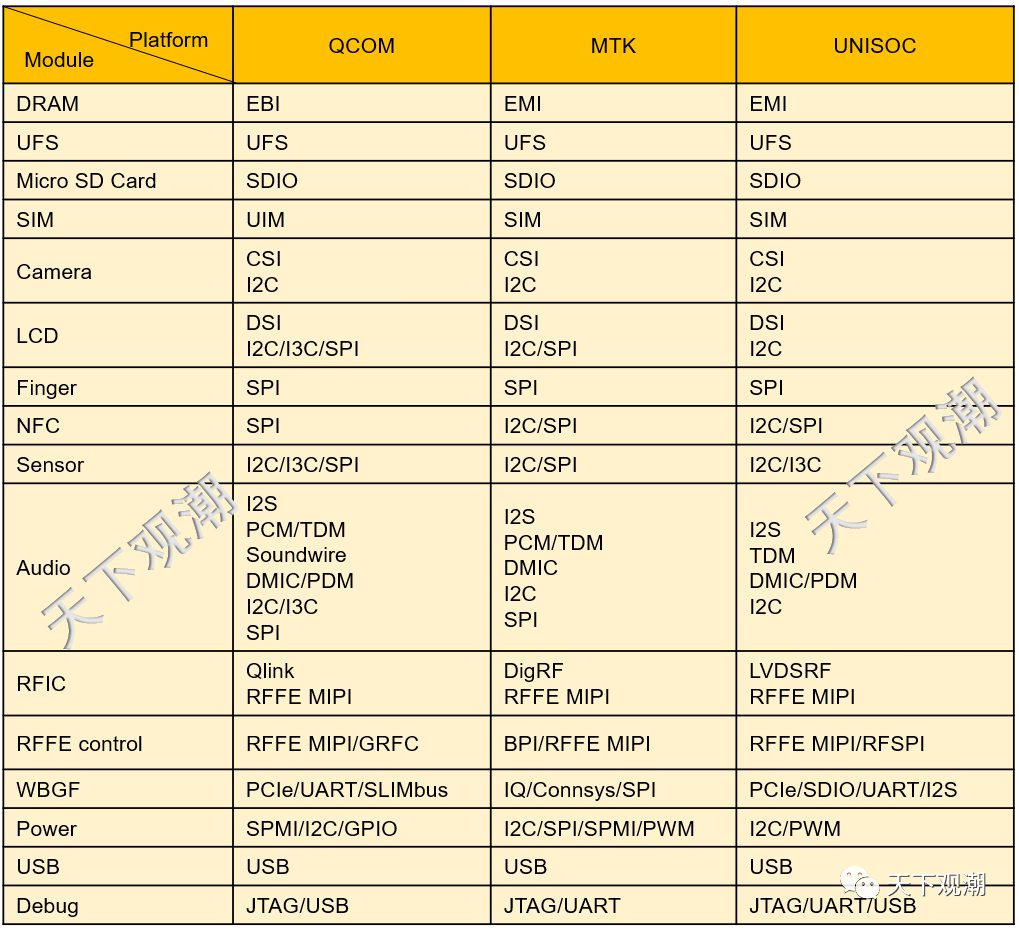

各子系统之间,子系统与外设之间需要频繁处理大量复杂的数据和信号,因此催生出各式各样,不同标准的接口。不同平台所用接口也有所不同。

如AP和Memory之间的EMI、UFS、SDIO接口;

AP与摄像头、触摸屏之间的MIPI CSI、DSI接口;

AP与外设传感器之间的I2C、SPI接口;

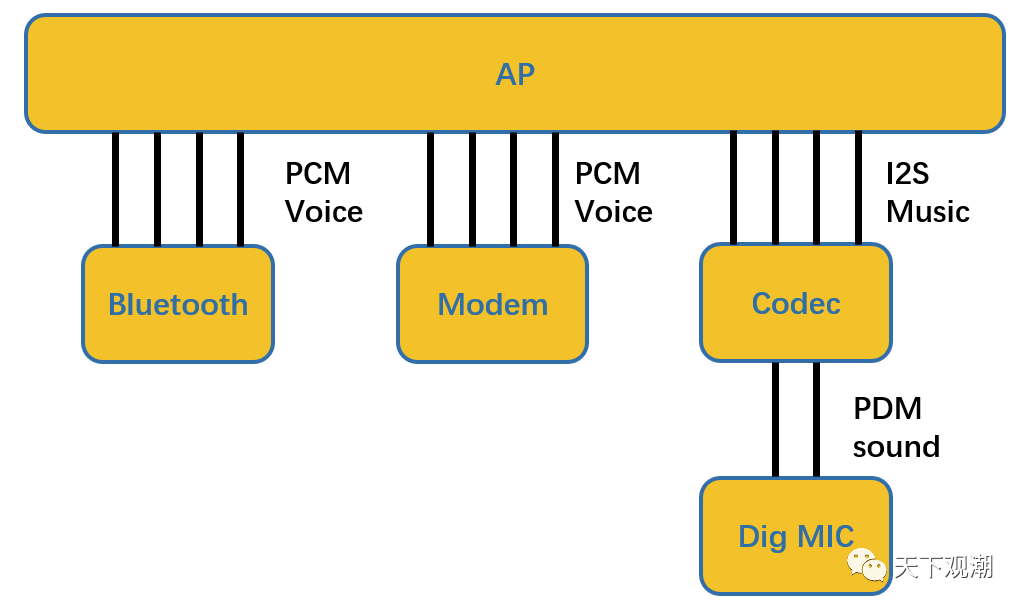

AP与Codec、Audio PA之间的I2S、PCM/TDM、I2C、SPI、Soundwire、DMIC/PDM接口;

Modem与RFIC之间的Qlink、DigRF、LVDSRF、RFFE MIPI接口;

AP与WBG之间的PCIe、SDIO、UART、SLIMbus、I2S接口;

PMU与外围电源器件之间的I2C、SPMI、SPI、PWM接口;

以及Debug用的JTAG、USB、UART接口等。

IIC-Inter-Integrated Circuit

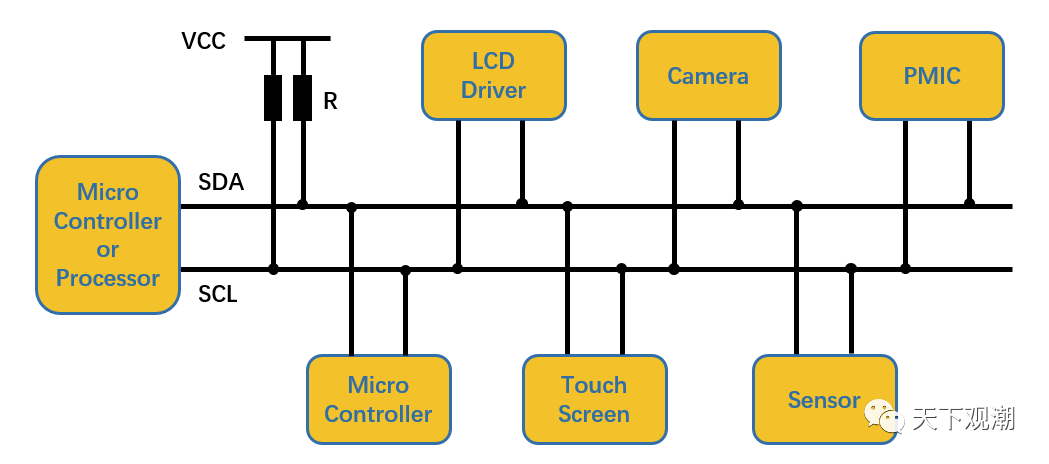

I2C作为最早最常用的电路接口,上世纪八十年代由飞利浦推出后,于1992年定版,属于半双工串行总线,主要用于短距离低速芯片之间通信,如触摸屏、摄像头、传感器,以及电源芯片等。

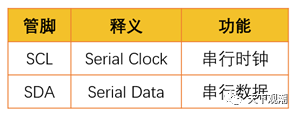

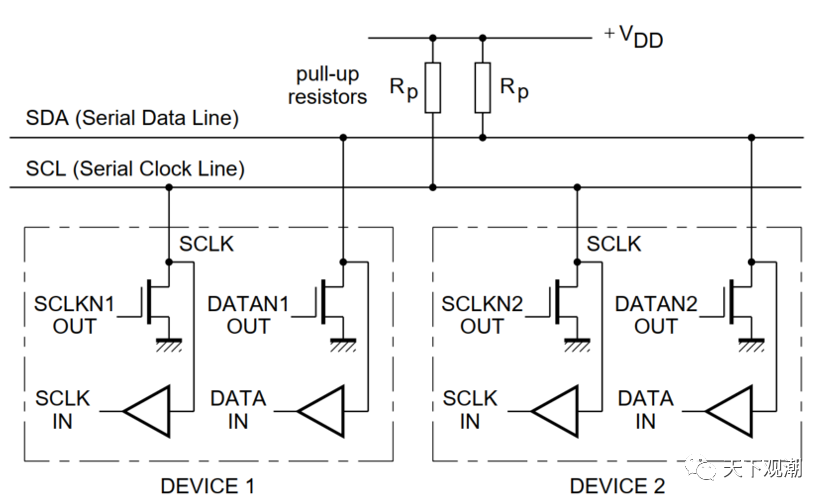

I2C只有两根双向信号线,SCL用于时钟同步,SDA用于传输数据,支持多主机操作,最大从机理论可达127(2的7次方个设备,其中一个是主机),但受最大电容400pF限制。

SCL和SDA内部使用开漏驱动,可以被拉低,但不能被驱动为高电平,需要接上拉电阻,空闲时都是高电平。

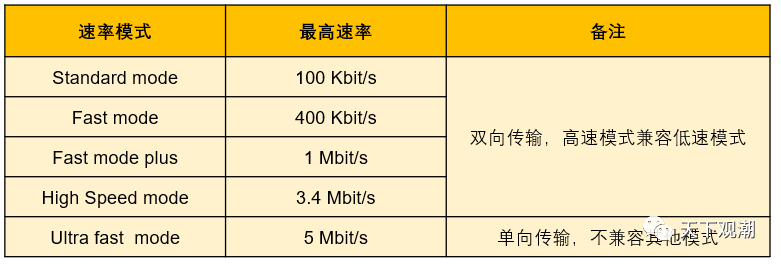

Standard mode: 100k bps;

Fast mode: 400k bps;

Fast mode plus: 1M bps;

High speed mode: 3.4M bps;

Ultra fast mode: 5M bps;

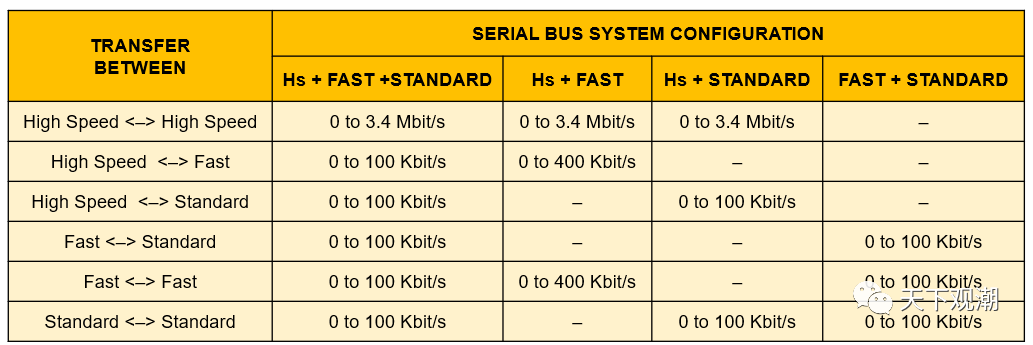

最常见的还是标准模式,快速模式和高速模式三种,如MTK平台的的I2C几乎都是400K bps的快速模式。三种模式之间的通信速率如下:

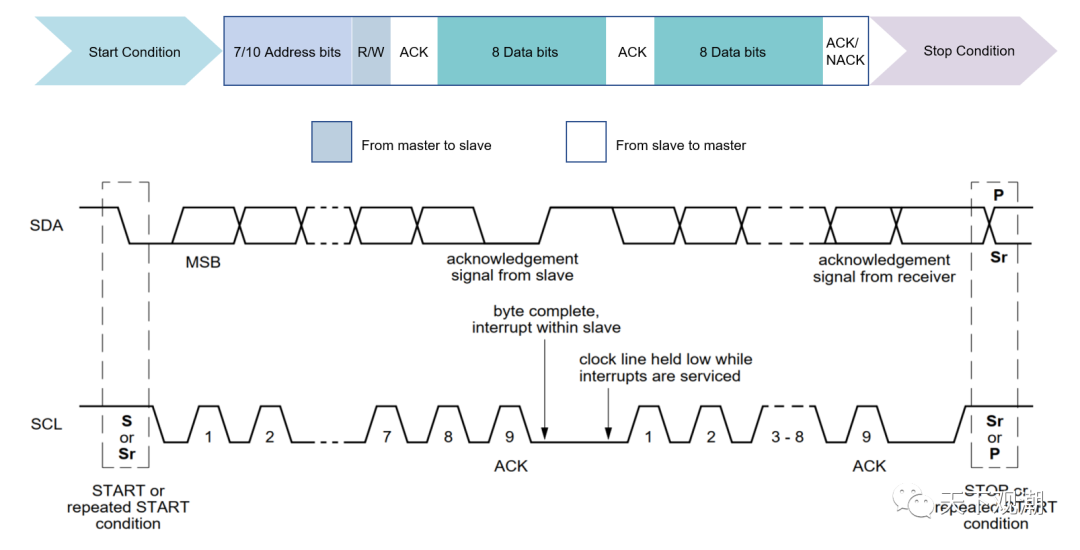

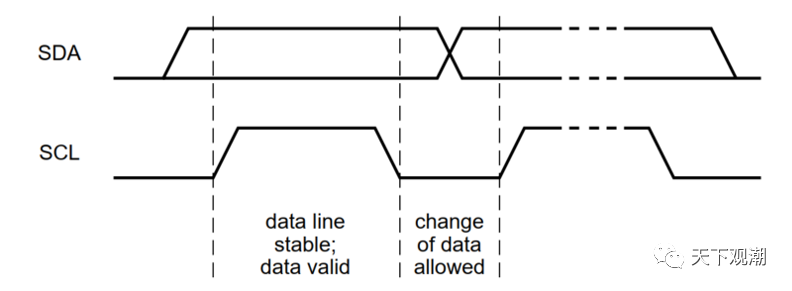

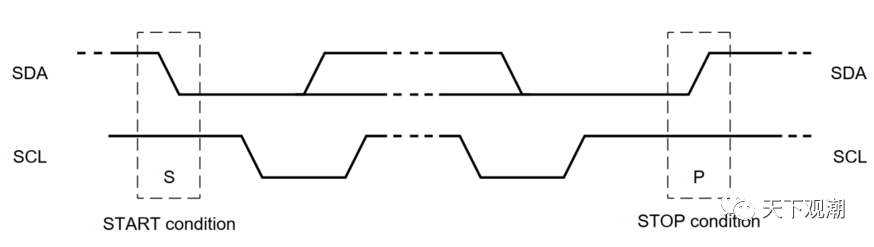

主机开始通信时,SCL为高电平,SDA由高变低启动, SCL由高变低同步时钟。在SCL为高时,SDA不允许变化,必须保持稳定;SCL为低时,SDA才允许变化。

主机发送一个字节8bit的数据,其中包括从机地址(address)和后续字节的传输方向(R/W),0表示主机--从机,1表示从机--主机;对应的从机检测地址是否匹配,被寻址的从机发送应答信号(ACK)回应主机;发送器(不一定是主机)发送一个字节数据,遵从MSB高位优先原则,先发高位,再发低位,接收器(不一定是从机)发送应答信号回应;如果接收器发送的Not Acknowledge,即SDA高电平,则通信结束;主机在SCL为高电平时,SDA由低变高停止通信。

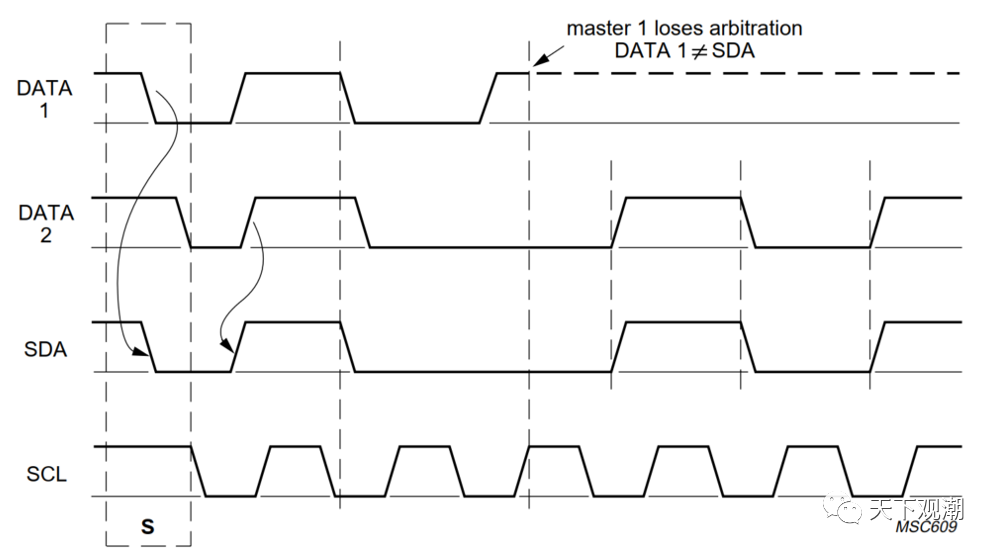

因为SCL和SDA都是开漏,只有所有的主机都发高电平时,SCL/SDA才是高电平;只要有一个发低电平就表现为低电平,即“与运算”。当一个主机发送数据后,在SCL为高电平时,检查SDA电平是否和自己发的一致,如果不一致则输掉仲裁,停止向SDA写数据;检测如果SDA一致,则继续传输数据。因为“与运算”特性,谁低谁就能强制SCL/SDA为低,抢占优先级,因此谁先低,谁优先;谁先高,谁退出。

SPI-Serial Peripheral Interface

SPI是最常用的串行外设接口,全双工同步通信,比I2C速率更快,上世纪80年代由摩托罗拉推出后,迅速广泛应用于LCD、Memory、Sensor、NFC、Audio、指纹识别等领域。

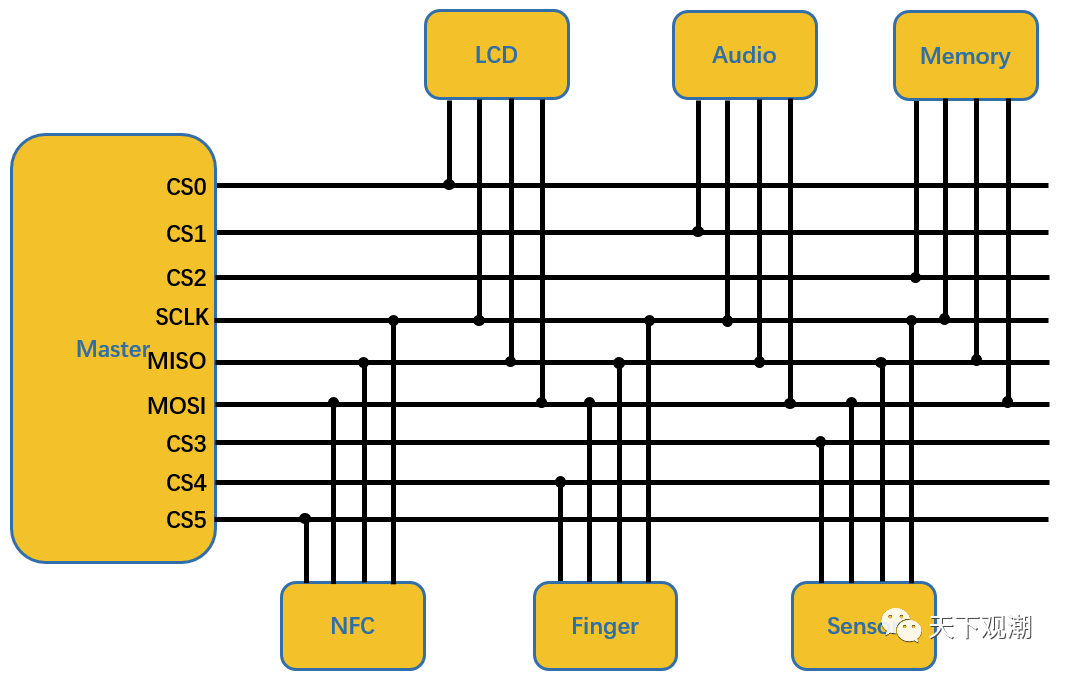

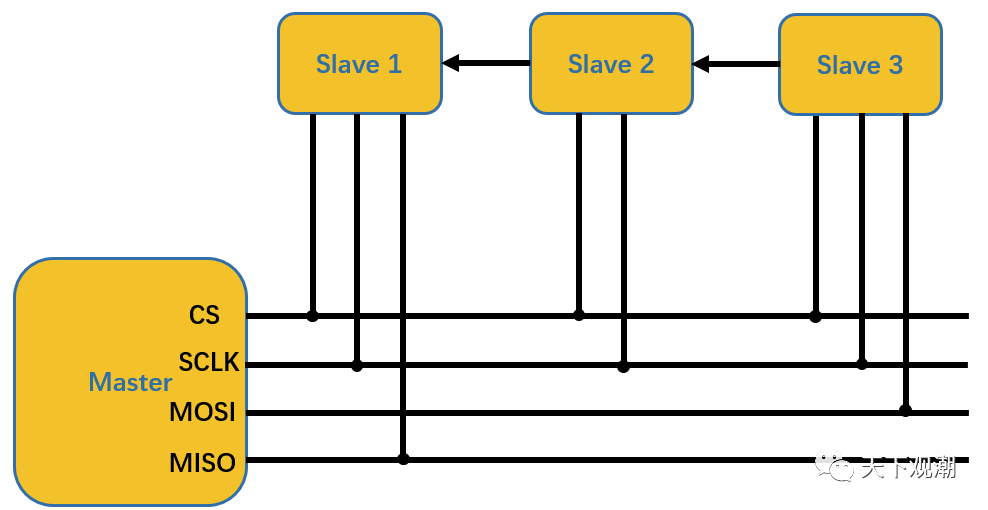

SPI需要4根线传输:CS为片选信号,由主机发出,低位有效,每个从机都需要一个CS;SCLK为串行时钟信号,最大频率只有系统时钟频率的一半;MOSI为主出从入信号,由主机发出,从机输入,主机和从机均为MOSI引脚互联;MISO为主入从出信号,由从机发出,主机输入,主机和从机均为MISO引脚互联。

若主机CS信号引脚数量有限,可以采用菊花链结构,各从机MISO和MOSI互联,主机发出的信号遍历所有从机。

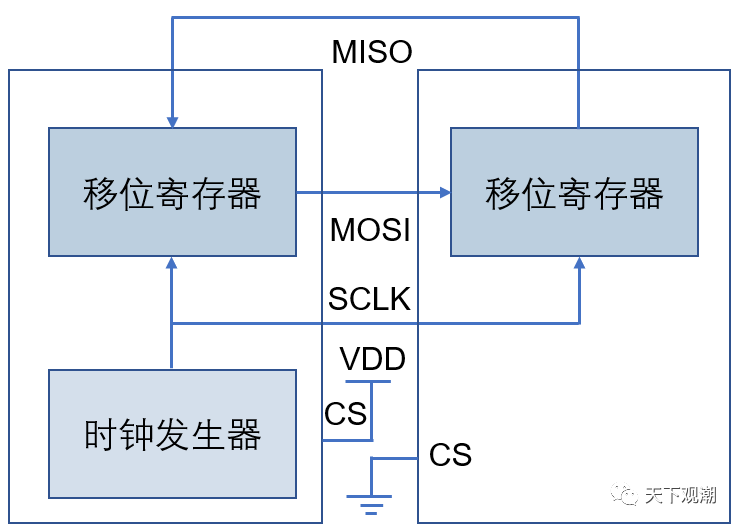

通信时,主机会先将CS片选拉低,然后发送SCLK时钟信号通知从机马上进行读写操作。SPI通信的时钟频率受低速器件限制。在每个时钟周期内,都会进行一次全双工数据传输,主机通过MOSI发出数据,从机通过MOSI接收数据后通过MISO再发出去。主机、从机中的8bit移位寄存器以虚拟环形拓扑连接,在时钟沿,主机从机都移最高有效位的1bit数据给对方。下一个时钟沿双方再对传输线上的该bit数据采样,并将其设置为移位寄存器的新最低有效位。如此重复则可以传输任意时钟周期的数据。因此SPI数据传输实质上为数据交换。

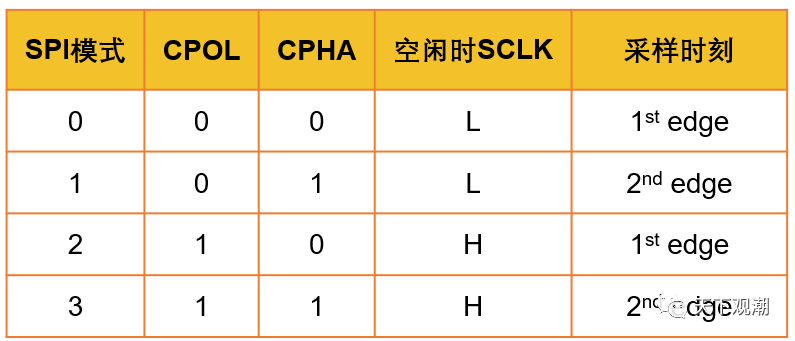

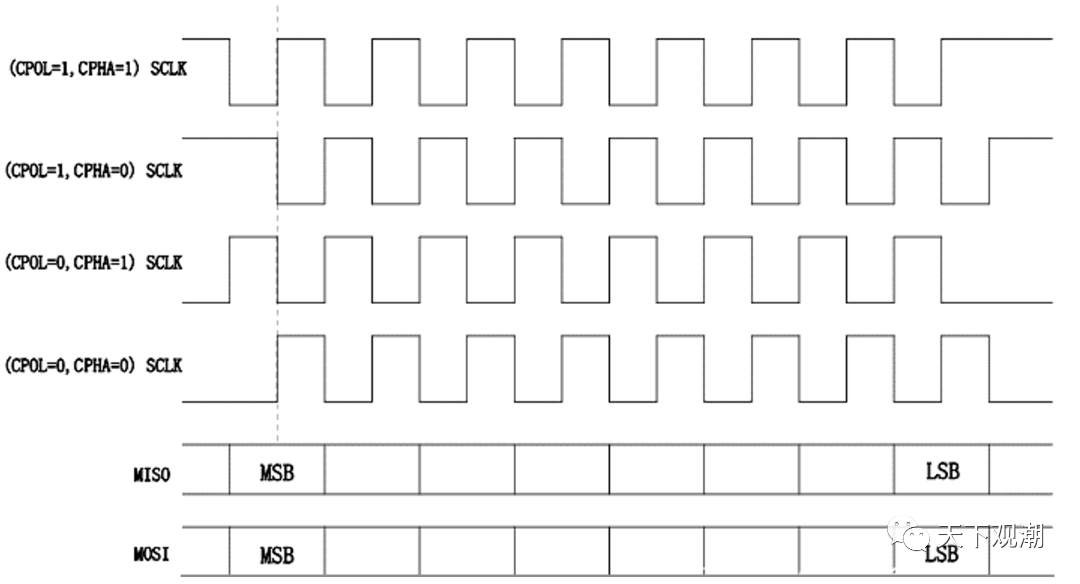

根据时钟极性(CPOL, Clock Polarity)和时钟相位(CPHA, Clock Phase)的不同,SPI通信有四种通信模式。

CPOL定义了SCLK空闲时的电平:CPOL=0,则SCLK空闲状态时电平为低,有效状态为高;CPOL=1,则SCLK空闲状态时电平为高,有效状态为低。

CPHA定义了数据位相对于时钟线的时序:CPHA=0,则一个周期包括半个空闲和半个置位,在时钟前沿采样,后沿改变;CPHA=1,则一个周期包括半个置位和半个空闲,在时钟前沿改变,后沿采样。

SPI只有时钟和数据,没有地址,当使用多个不同模式的从机设备时,主机设备切换模式时重新初始化,会使访问从机设备速度变慢。

SPMI-System Power Management Interface

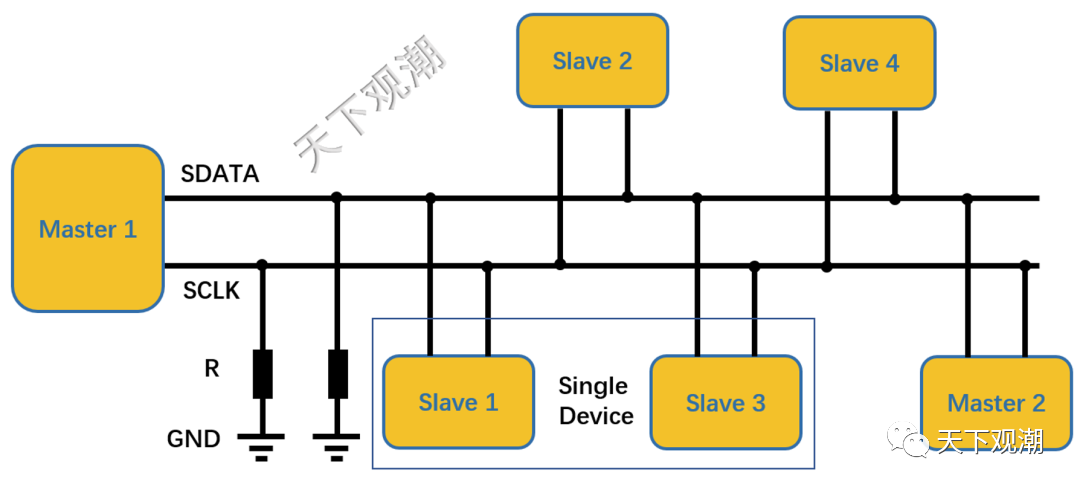

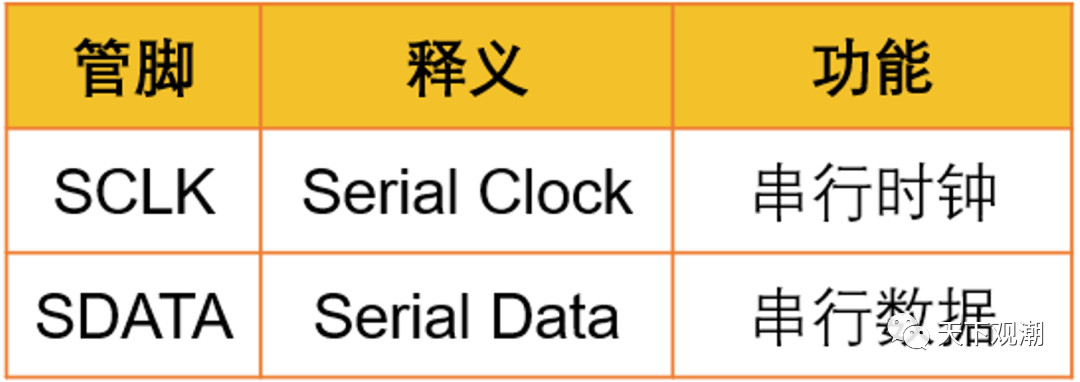

I2C和SPI都于上世纪八十年代推出,广泛应用于各类芯片。在电源管理芯片领域为了统一接口,MIPI联盟推出SPMI接口,用SDATA和SCLK两根线,即可控制所有电源芯片,准确监控处理器性能水平,实时动态控制各种电源电压。

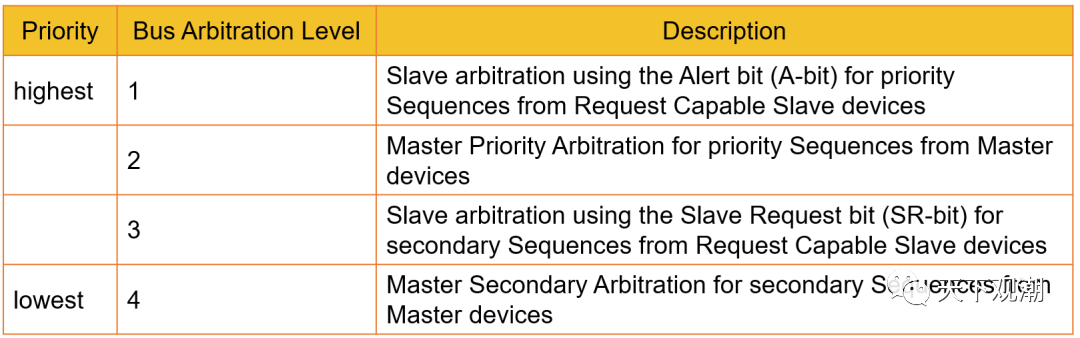

SPMI与I2C类似,只有两根线:SCLK为串行时钟,SDATA为串行数据。

时钟频率有两种模式:高速模式为32KHz-26MHz,低速模式为32KHz-15MHz,比I2C速度要快一些。支持多主机和多从机工作,主机有2bit MID(Master Identifier),因此SPMI总线可以最多支持4个主机;从机有4bit SID(Slave Identifier),因此SPMI总线可以最多支持16个从机。主从设备都是CMOS结构,需要下拉电阻,因此空闲时为低电平,高位有效。

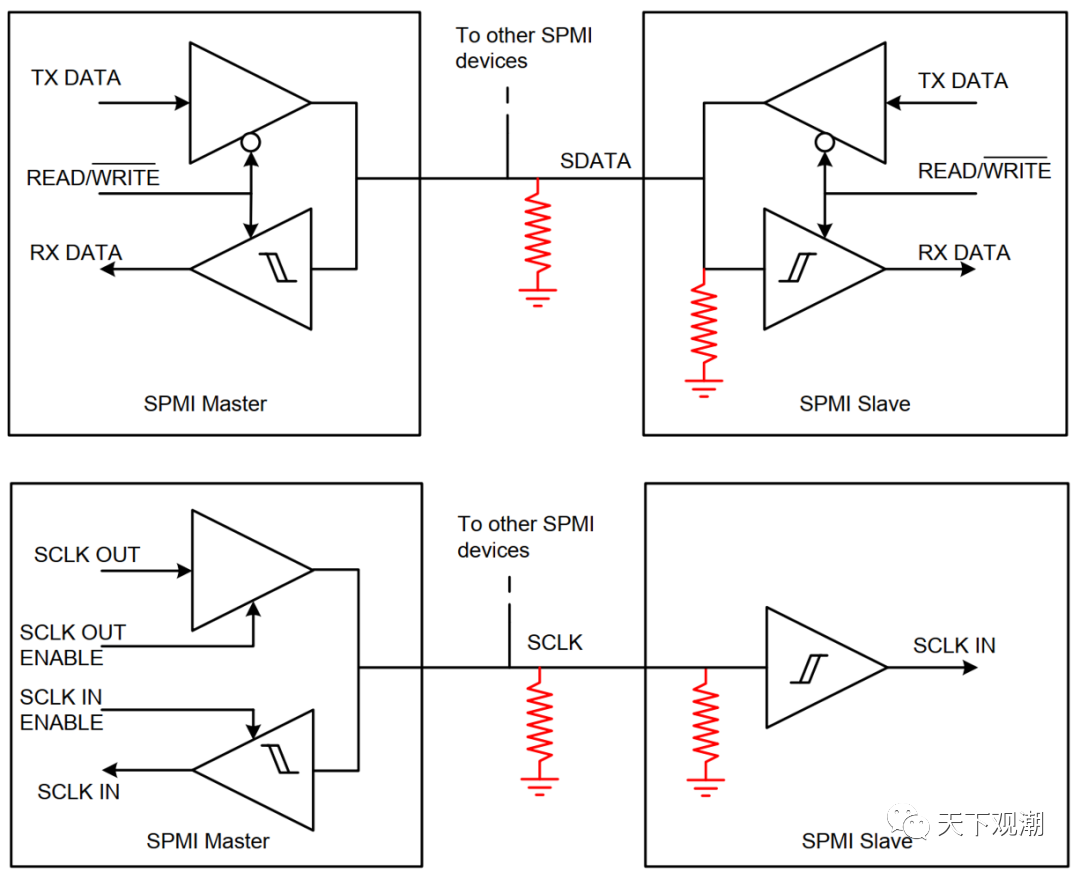

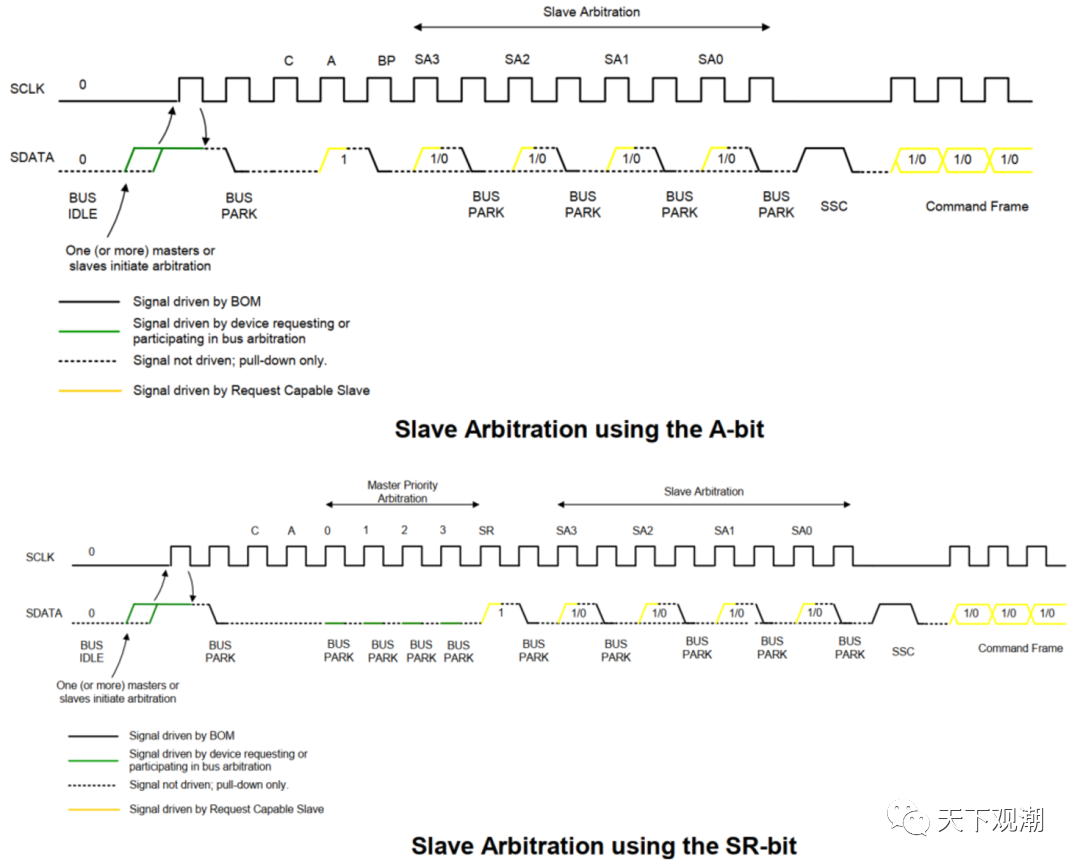

占据总线的主机称为BOM(Bus Owner Master),每次通信前需要总线仲裁,由BOM决定仲裁结果。空闲状态下SCL和SDATA都是低电平,哪个主机想发数据,就把SDATA线拉高,BOM检测到后发SCLK,开始仲裁;如果没有BOM发CLK,就自己发CLK当BOM。根据主设备的MID可以计算相对应的MPL(Master Priority Level),每次仲裁结束后MPL都会重新计算。MPL0的主机优先级最高,抢到BOM后接入总线,可以发SSC(Sequence Start Condition)序列后将SDATA拉高,再发Connect Sequence接入总线。

可请求从机(RCS,Request Capable Slave)发出Alert bit表示注意到主机即可进入总线仲裁,或者发Slave Request(SR) bit进入总线仲裁,但优先级要比发Alert bit的低。从机匹配地址和命令后,发出ACK/NACK应答完成通信。

可请求从机(RCS,Request Capable Slave)发出Alert bit表示注意到主机即可进入总线仲裁,或者发Slave Request(SR) bit进入总线仲裁,但优先级要比发Alert bit的低。从机匹配地址和命令后,发出ACK/NACK应答完成通信。

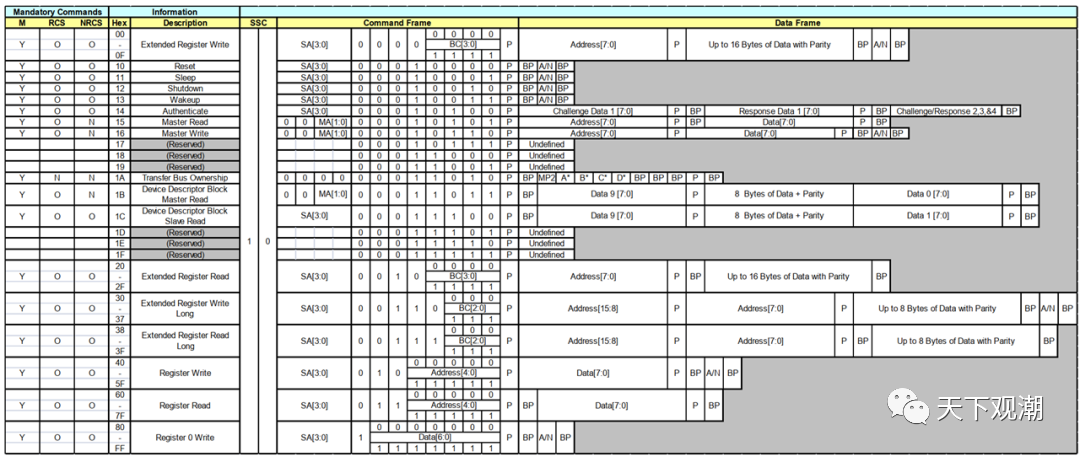

SPMI 的Command Sequence格式如下:

I2S - Inter-IC Sound

I2S和I2C一样都是由飞利浦于上世纪八十年代推出的经典接口,于1996年定版,专门传输芯片之间的数字音频数据,主要用于Codec、Audio PA、DSP等。

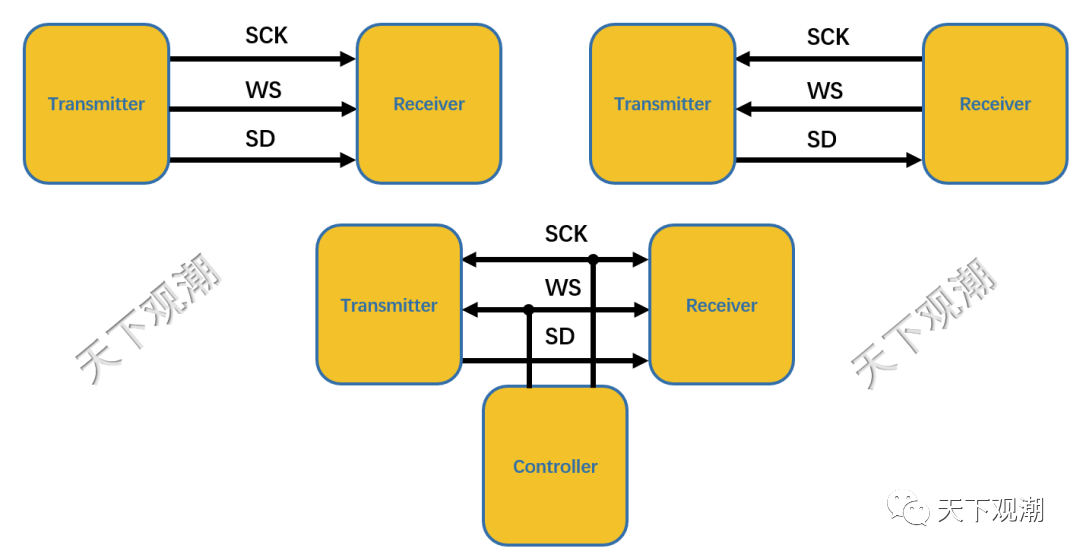

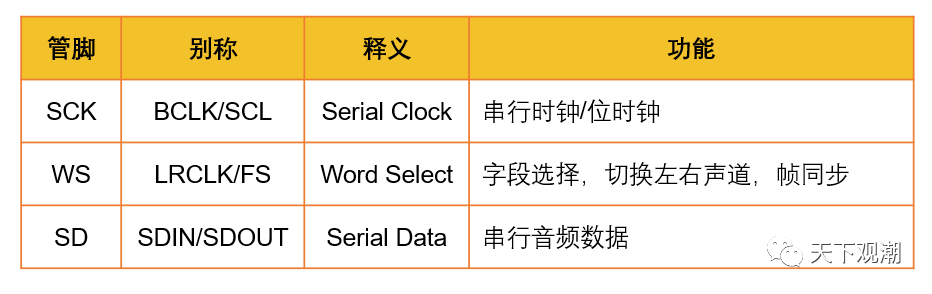

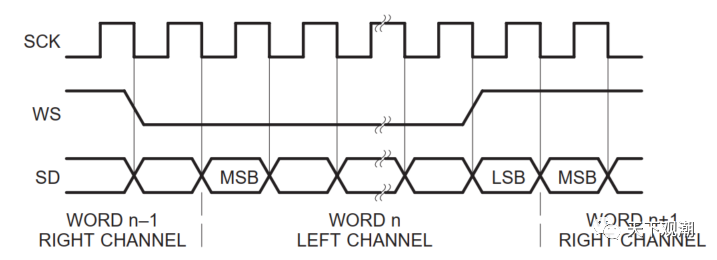

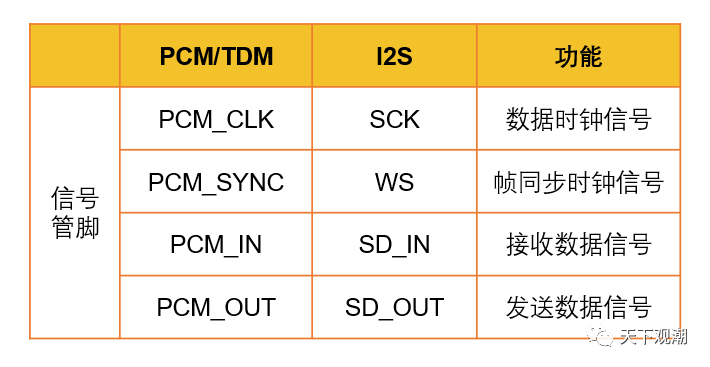

I2S只有三根以上的单向信号线。SCK(也经常写做BCLK和SCL)为串行时钟,用于时钟同步,SCK的频率 = 声道数 * 采样频率 * 采样位数;WS(也经常写做LRCLK和FS)为字段选择,切换左右声道,0-left; 1-right, WS的频率 = 采样频率;SD为串行数据传输,由高位到地位依次传输,SD可以分为SDIN和SDOUT。有时候为了使系统更好地同步还需要再加一个MCLK主时钟,一般是采样频率的256或384倍。

I2S系统中只能同时存在一个主设备和发送设备,提供时钟的为主设备。I2S数据高位优先,最高位总是出现在WS变化的第二个SCK,即比WS晚一个时钟周期,左对齐和右对齐模式不常见,不做赘述。发射机和接收机的字长经常不一致,因此比系统字长短的部分需要置0补齐。

PCM/TDM

Pulse Code Modulation/ Time Division Multiplexing

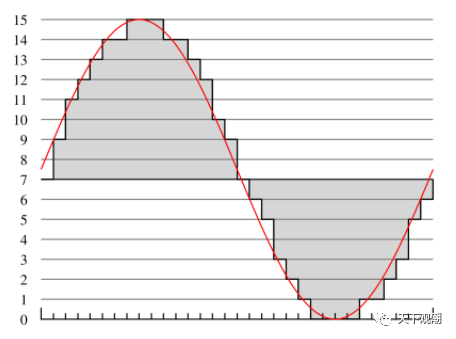

声音是最典型的模拟信号,即信号幅度连续,频率不固定。人耳听到的频率一般在20-20KHz,低频机械波保存和长距传输难度太大,因此通过脉冲编码调制,按照一定的频率采样,用一定长度的量化值表示声音数据,即可将模拟的声音信号转化为对应的数字信号保存。

需要还原为声音时,利用低通滤波即可恢复成模拟的音频信号。采样频率越高,与原始声音信号就越吻合,但是数据量也越大,常用的采样频率有11.025KHz、22.05KHz、44.1KHz、48KHz、96KHz等;量化位数越多,还原得到的声音信号音质就越好越保真,常用的量化位数有8bit、16bit、24bit、32bi等。一般采用44.1Hz的采样频率,16bit就可以得到高保真的声音。另外,声道数越多,声音的表现力越强,双声道立体声就比单声道表现力丰富很多。

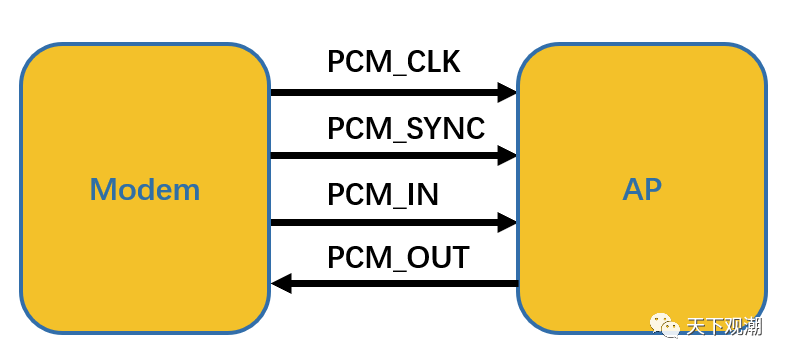

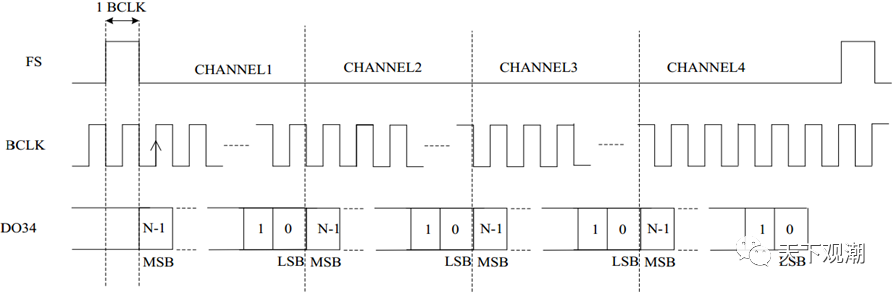

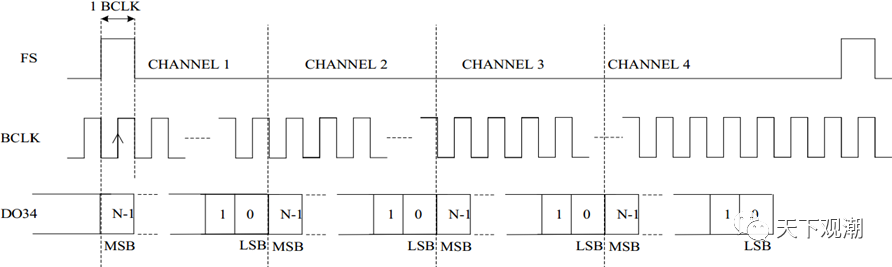

PCM/TDM与I2S很类似,有四根单向信号线。PCM_CLK为串行时钟;PCM_SYNC为帧同步信号;PCM_IN为接收数据信号;PCM_OUT为发送数据信号。PCM通过TDM模式可以传输最多16个声道的数据,因此一般传单声道数据(如麦克风)时,接口名称为PCM,双声道时为I2S,多个声道数据时为TDM。

根据Data相对于SYNC的位置,TDM分为Mode A和Mode B两种基本模式。

Mode A和标准I2S一样,在SYNC后的第二个CLK上升沿有效。

Mode B和I2S左对齐一样 ,在SYNC后的第一个CLK上升沿有效。

如前文I2S时钟频率计算方法一样,TDM的系统时钟频率=声道数 * 采样位数 * 采样频率,器件厂家会将声道数和采样位数直接标注在手册中,如TDM128/TDM256等。

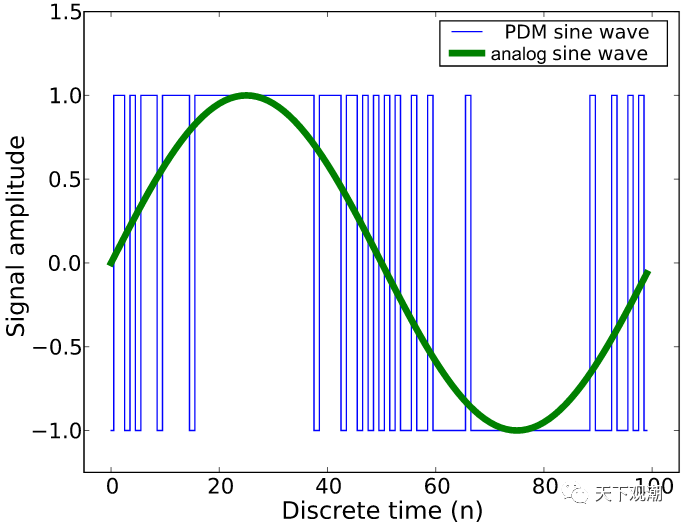

PDM

Pulse Density Modulation

PCM采样等间隔,采样位数多,因此传输的数据量大,数据线也多。对于数字麦克风,则使用PDM接口。

用每一个时刻的采样值与上一时刻的采样值做比较,其差值大于Δ,则输出1,否则输出0。这样量化位数为1,输出要么为0要么为1。但是为了控制量化噪声,采样频率却要比PCM高很多。

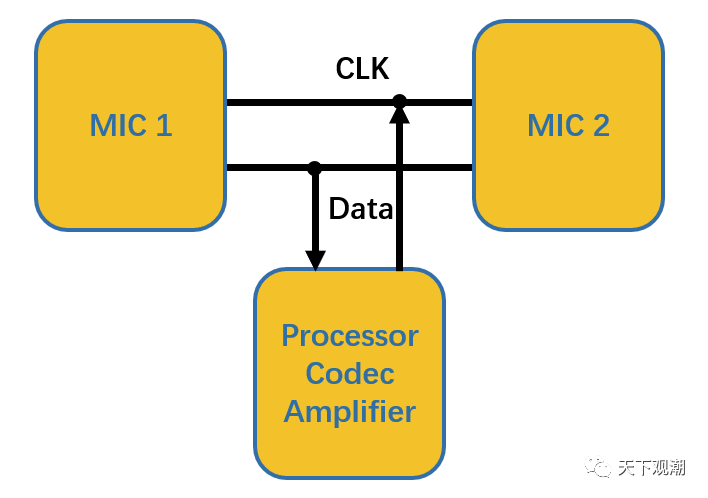

PDM只有时钟CLK和数据输出Data两根线,使用非常方便,主设备(DSP、Codec、Amplifier等)提供时钟,可以设置在时钟的上升沿或下降沿触发音源选择作为数据输入。

PDM通信较为简单,没有“抢总线”过程,也没有接收应答等复杂操作,麦克风将采样到的模拟声音信号编码为数字信号后根据时钟的上升沿和下降沿,分别传输给接收机作为左右声道的数据。

SLIMbus

Serial Low-Power Inter-chip Media Bus

和SoundWire

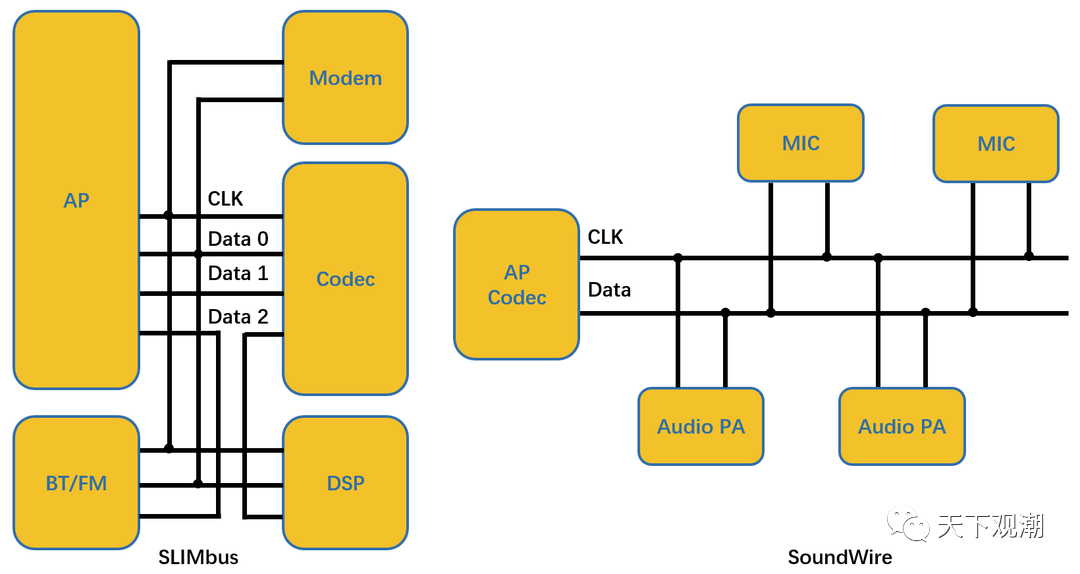

音频器件除了传输数据用的I2S等数据接口外,器件控制还需要I2C,接口数量和总线较多。MIPI联盟为了连接AP/Modem和音频器件,推出了SLIMbus和SoundWire,统一了控制接口和数据接口。目前手机SOC里只有高通支持SLIMbus和SoundWire接口。

贯彻MIPI联盟一贯的极简风格,只需要CLK同步串行时钟,Data发数据。根据数据情况可能会有3根Data线。SLIMbus采用单数据速率(SDR)运行,时钟28MHz,具有固定的帧大小,支持主控和时钟切换以实现低功耗操作。SoundWire是SLIMbus的补充,最多可支持11个设备,采用双数据速率模式(DDR),时钟可以降至12.288MHz,支持可配置的帧大小和增强的低延迟协议。

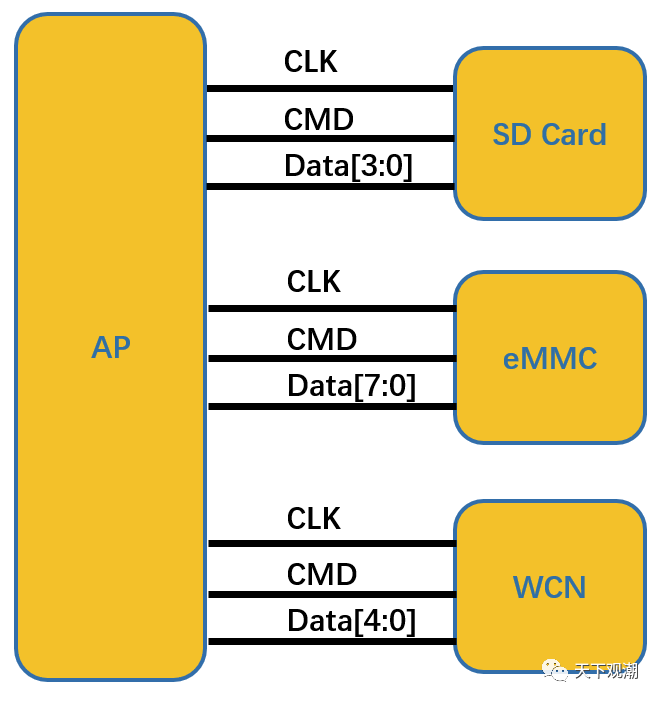

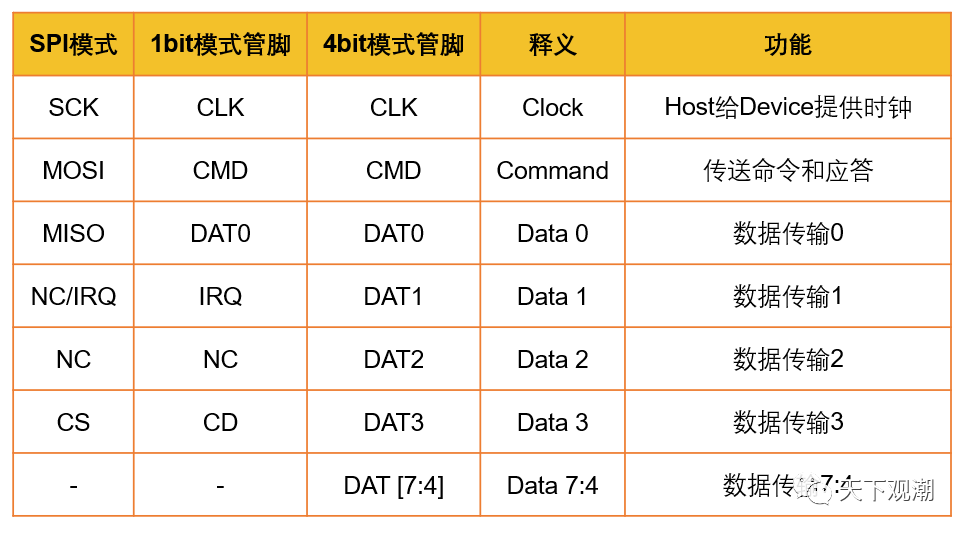

SDIO-Secure Digital Input and Output

SDIO主要有SPI模式、1bit模式、4bit模式和8bit模式四种模式。SPI模式前文介绍过,1bit模式使用不多,现在主要是4bit模式,也称QSPI。eMMC这种速率更快的需要8bit数据线传输。

SDIO总线的设置和控制都是HOST端发起的,Device端回应请求,命令和回应都是通过CMD信号线传送的。双向数据传输通过Data线实现。

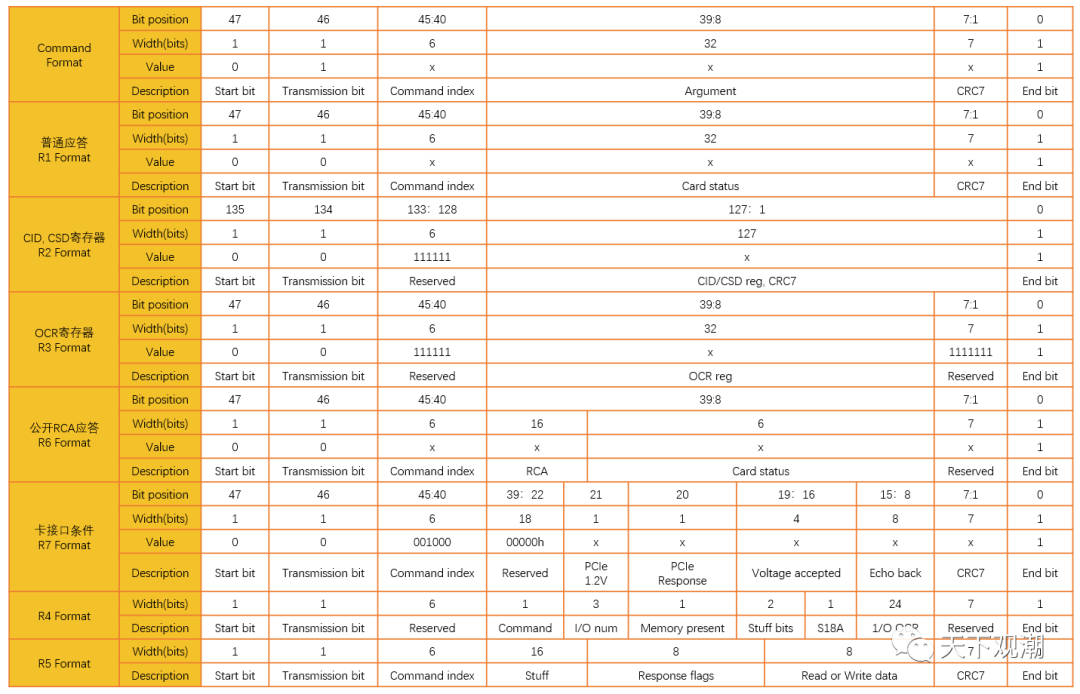

应答模式有R1、R2、R3、R4、R5、R6 、R7七种,不同器件具体设置也会不一样,需要查阅相应的数据手册,检查哪条命令对应哪个应答。

PCIe

Peripheral Component Interconnect express

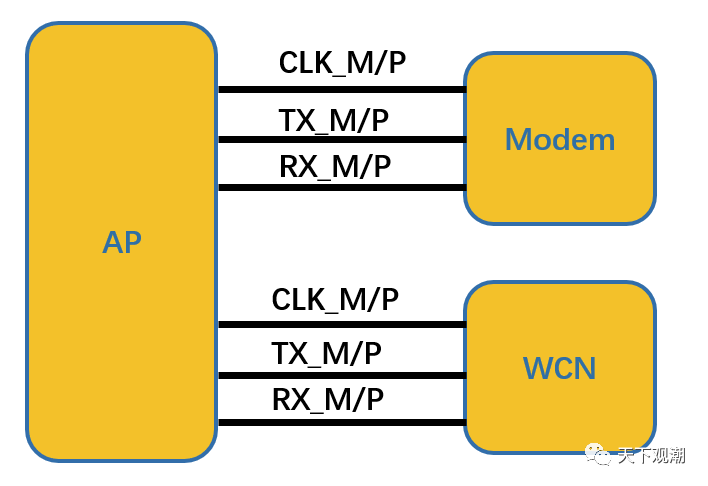

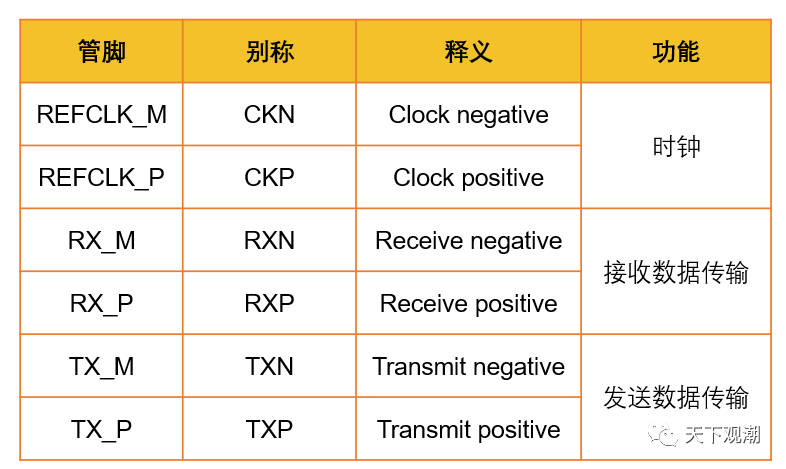

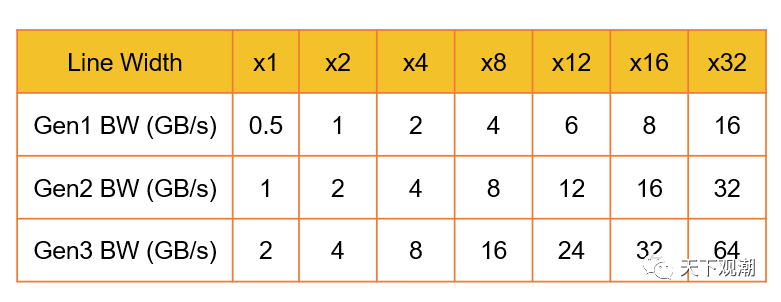

PCIe是全双工传输,常用的1lane模式主要有差分时钟CLK_M、CLK_P;差分数据发送TX_M、TX_P;差分数据接收RX_M、RX_P;合计6根线。

根据Lane的数量可以增加TX和RX的差分数据线对数,增加速率。

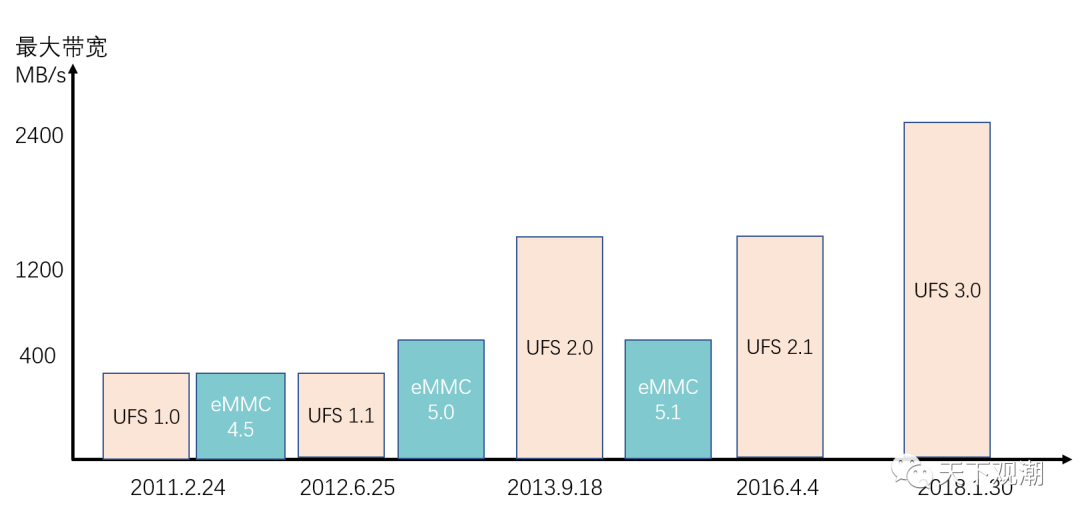

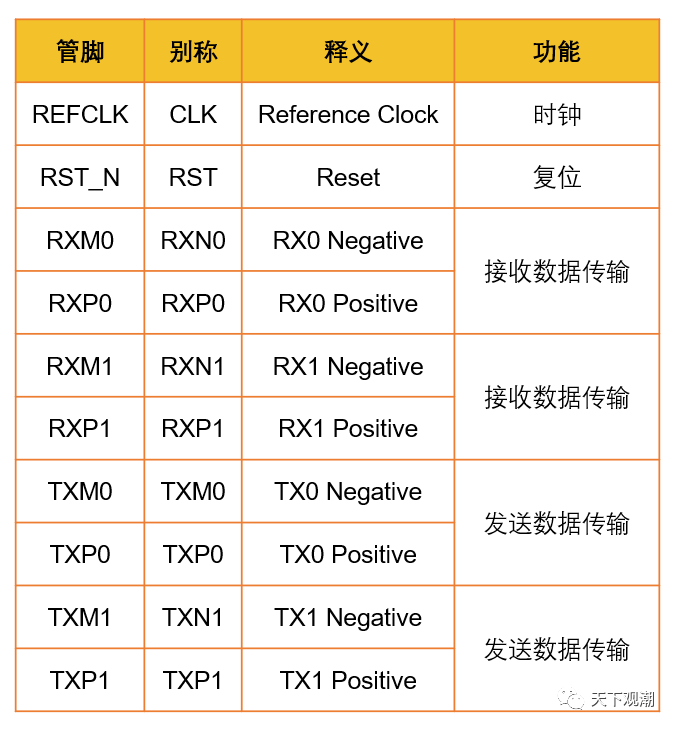

UFS-Univeral Flash Storage

UFS和PCIe比较类似,也是差分数据传输(目前最多支持两通道),但是多了Reset复位脚,时钟也是单端的。

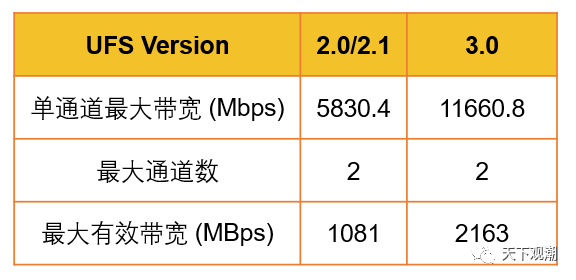

差分信号可以更强的抵抗干扰,因而可以以更快的速度传输数据,从而提供更宽的带宽。现在最新的UFS 3.0可以支持最大2163MB/s的有效带宽,比前面同等配置的PCIe 3.0还快。

UFS支持命令队列,属于异步全双工模式,主机同时发出多个命令,UFS设备并行乱序执行,因而智能手机可以同时听歌打游戏聊微信,多线程操作不冲突。

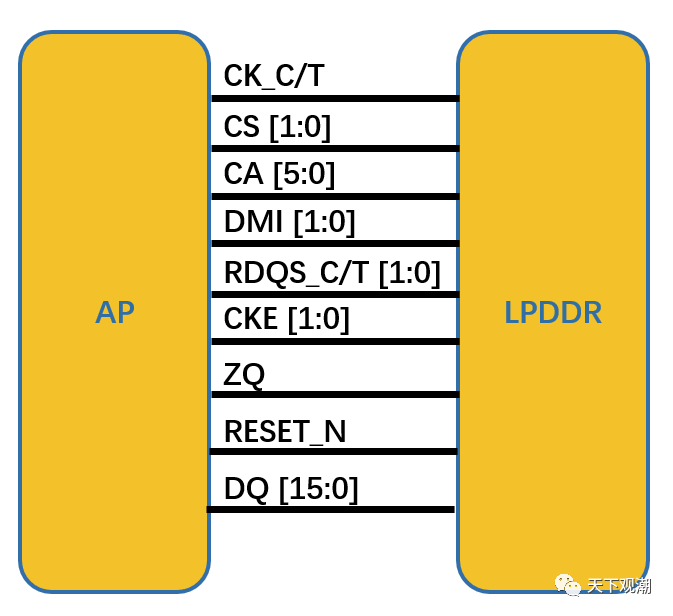

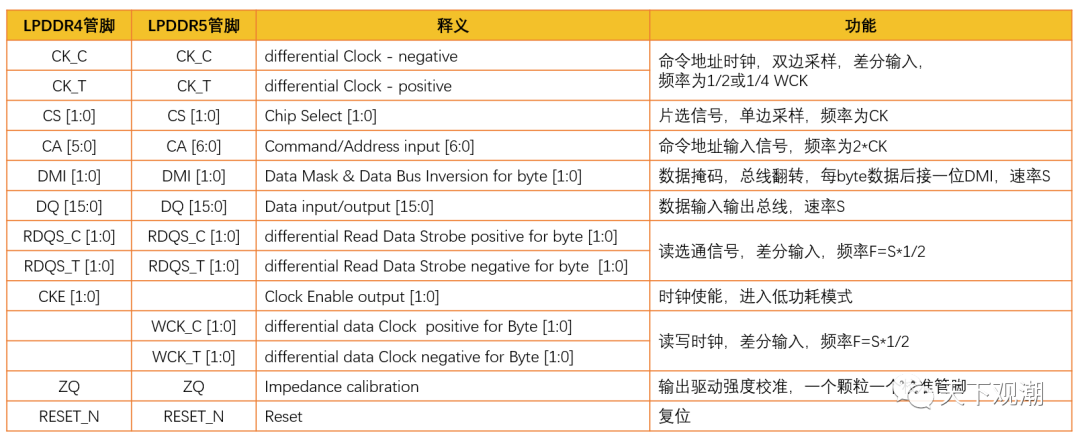

EBI-External Bus Interface

LPDDR因为是双边采样,因此数据速率是读写时钟的两倍,WCK=RDQS=1/2*DQ。命令地址也是双边采样,速率也是时钟两倍,CA=2*CK。片选信号单边采样,速率与时钟一致,CS=CK。根据WCK和CK的比例,即可计算时钟与速率的关系。

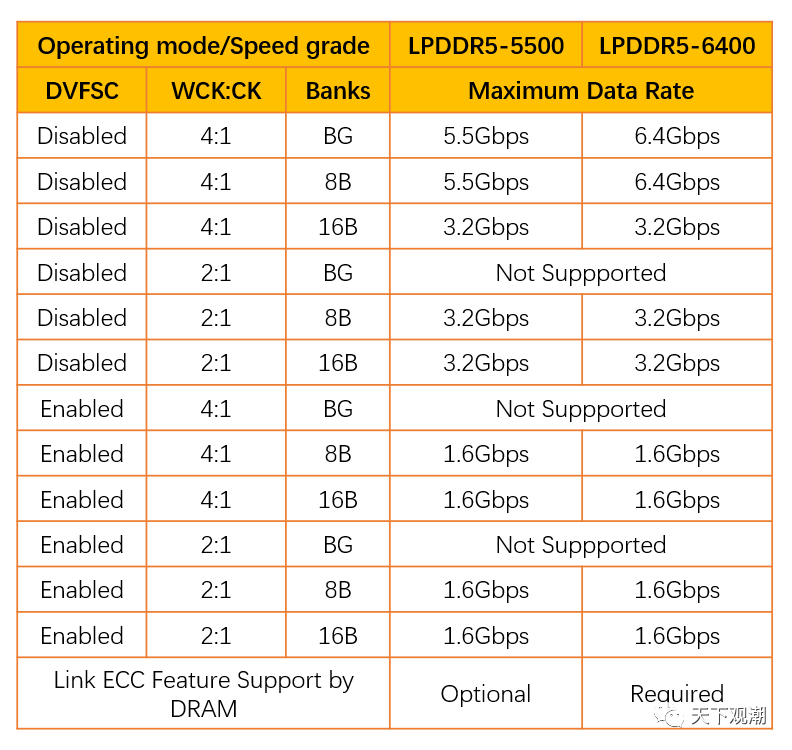

DDR产品的演进整体较快,LPDDR的消费类属性使得其两三年更新一代,今年镁光新发布的LPDDR5x已经做到8533Mbps的速度,也是快的离谱。

end

一口Linux

关注,回复【1024】海量Linux资料赠送

精彩文章合集

文章推荐