文︱王树一

图︱Rambus

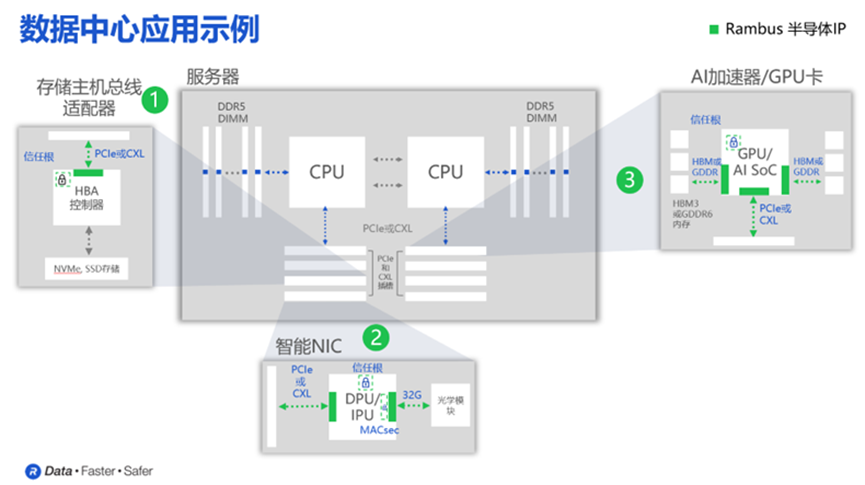

近日,硅IP和芯片提供商Rambus宣布推出PCIe 6.0子系统。该子系统由PCIe 6.0控制器和PCIe 6.0物理层(PHY)组成,PCIe6.0 PHY 传输速率相比PCIeG 5.0增加一倍,达到了64GT/s,并且支持CXL 3.0规范的全部特性和功能,具备更好的缓存一致性。规格升级带来的性能增益,将使得PCIe6.0在数据中心中的存储主机总线适配器、智能网卡和人工智能加速等应用中得到广泛应用。

速度翻倍、编码改变,PCIe 6.0新特性

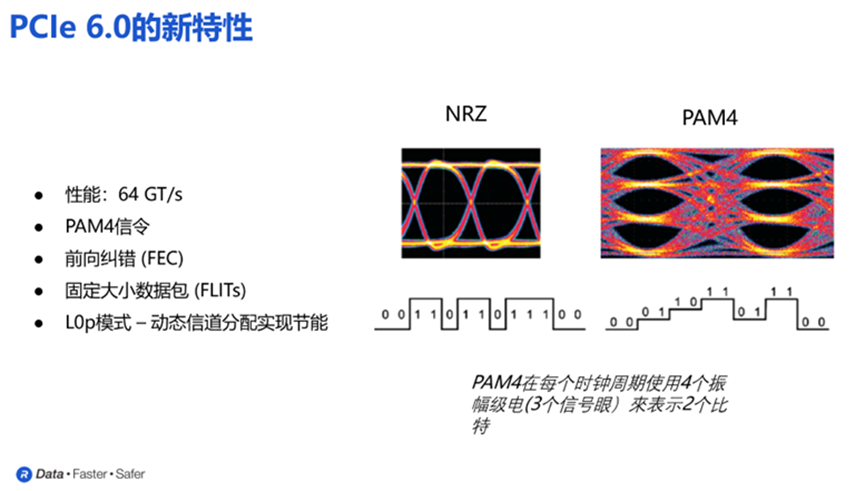

PCIe 5.0速度已经达到32GT/s,接近板级信号物理极限,PCIe 6.0要实现64GT/s的数据传输速率,必须在架构上重新选择,并调整电路传输机制,所以与PCIe5.0的NRZ编码不同,PCIe 6.0选择了PAM4编码。NRZ(Not Return Zero)是指不归零码,而PAM4(Pulse Amplitude Modulation 4-level)是指四电平脉冲幅度调制技术,NRZ不归零码是"0"、“1”双电平模式,而PAM4则升级到了四电平模式,每个时钟周期可以表示两比特信息,因而在不提升时钟频率的情况下,可以提升数据传输速率。

当然,PAM4增加了电压变化,因而对信号完整性和编码提出了新的要求,NRZ是单眼图,而PAM4是3眼图,为保证传输正确率,PCIe 6.0的PHY要支持前向纠错(FEC),因而必须采用固定大小数据包(FLITs),在PCIe6.0之前的版本,数据包的大小可以不同,但是PAM4的引入,让PCIe6.0的数据包改为固定大小。

另一个值得注意的变化是在PCIe 6.0中引入了动态信道分配机制(L0p),早期版本PCIe支持将不用的信道关闭,如果重新启用则需重新配置,而该机制则支持动态开关信道,从而可以让用户更灵活地实现系统的功耗管理,可以根据应用场景实时调整性能与功耗的平衡。

控制器加PHY的完整解决方案,最大程度简化集成PCIe 6.0的SoC芯片开发难度

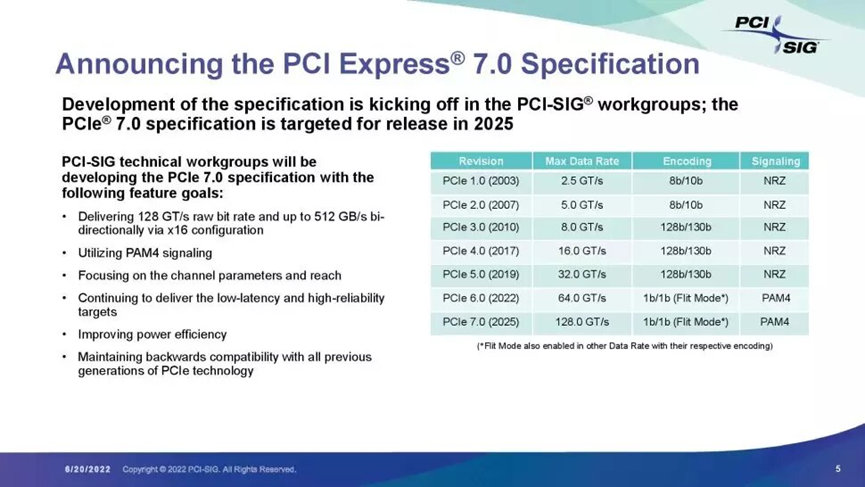

数据的爆炸式增长,引发数据中心带宽升级需求,而PCIe作为数据中心、云服务与高性能计算等场景下应用最广泛的互连技术,其技术升级的频率非常高,PCIe 5刚刚在数据中心应用中开始推广,Rambus PCIe 6.0子系统已经面世,而PCIe 7.0的标准也被制定中。Rambus 战略营销副总裁Matt Jones表示,PCIe版本迭代进程越来越短,SoC厂商更适合采用IP模式来开发,从而满足产品快速迭代的需求,只有开发进度可控,也才有机会收回在该技术上的投资。

Rambus在PCIe市场上的认可度颇高,迄今已经有超过400个项目流片,而其最新推出的PCIe 6.0子系统,将PHY与控制器全集成,可以更进一步降低延迟,优化功耗,以及减小芯片面积。Rambus 大中华区总经理苏雷表示,Rambus产品一向在PPA(性能、功耗和面积)上具有优势,而PCIe 6.0子系统则继承了这一光荣传统。

Matt Jones则指出,公司的PCIe 6.0子系统已经通过了硅验证,技术成熟度可靠,大幅降低用户开发PCIe 6.0技术的难度。相比PHY和控制器单独授权,两者结合的子系统方式,让SoC厂商的开发人员无需再重复做大量冗杂的验证工作,从可以将更多时间专注在产品差异化和算法开发上。

目标2025年大规模应用

按照SoC产品两年左右的开发周期,Rambus PCIe 6.0子系统今年推出后,到2024年市场上会有支持PCIe 6.0的产品出现,而2025年将是产品能否普及的关键期。

Matt Jones表示,虽然在这个时间节点,还不能预测PCIe 6.0的市场规模,但数据指数型增长的趋势是明确的,因而数据中心和云服务中对带宽要求的提升将加速市场对PCIe 6.0技术的接受度,而云服务厂商和高性能计算终端产品,将是最先采用新一代PCIe标准的厂商。

推荐阅读:

关于2022年全球及中国半导体发展情况的判断与思考