▼关注公众号:硬件微讲堂▼

大家好,我是硬件微讲堂。这是我的第56篇原创文章。为避免错过干货知识,欢迎关注公众号并加入免费技术交流群,抱团取暖,共同进步!

关于三极管前面已经发了7篇:

在上一篇着重聊了三极管CE组态的高频等效电路(混合π高频小信号模型)、高频截频fH,并用TINA-TI进行仿真做数据支撑,解释了放大电路不放大的原因。按道理,聊到这里就差不多了。但是我觉得做事需要做全套,聊了高频,不讲低频,这是不道德的。

今天写第8篇,重点聊聊三级管CE组态的低频等效电路、低频截频及对应的伯特图。

两个问题

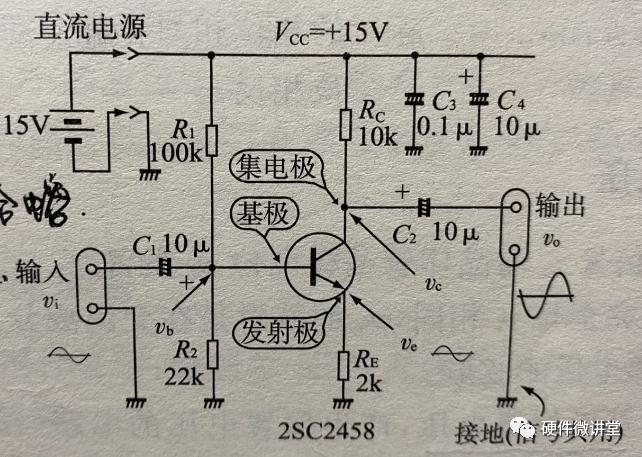

最近在研究三极管时翻到了《晶体管电路设计(上)》这本书,相信很多业内的小伙伴都有这本书。书中在第2章中的实验电路,正好和我们前面分析的例子相匹配。当然这不是巧合,毕竟这个电路太典型,很多模电书上都有分析。

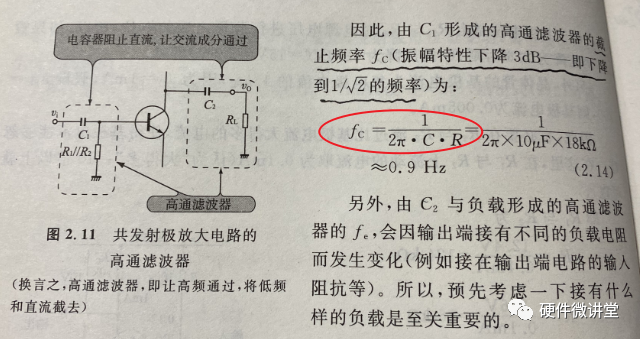

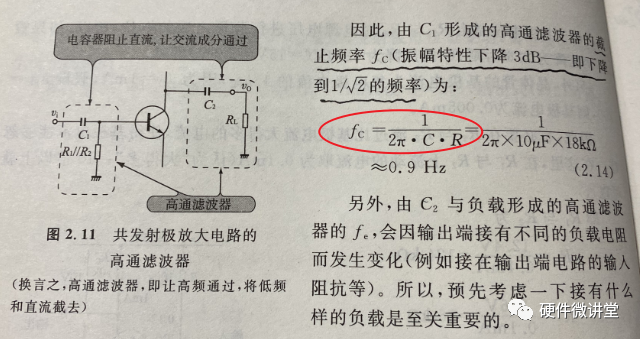

在Page24中,如下图红圈,有提到高通滤波器的截止频率fc=1/2πRC。不知道屏幕前的你在研究这本书时有没有疑惑?

理论分析

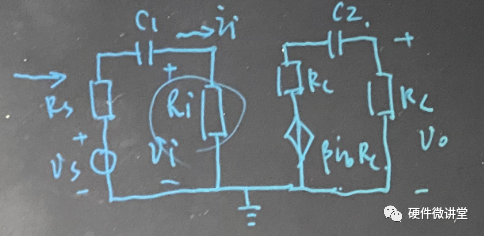

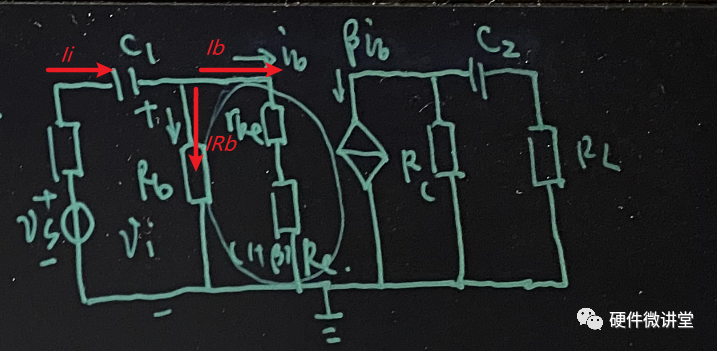

带着这两个疑问,对这个共射极放大电路进行分析。此时我们的目标很明确,就是低频带。在低频带时,交流耦合电容C1,C2不能再像中频带一样短路,需要考虑耦合电容的影响;而三极管的结电容依旧可以当做短路。

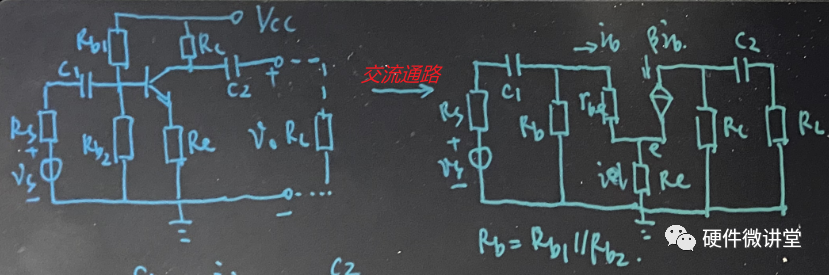

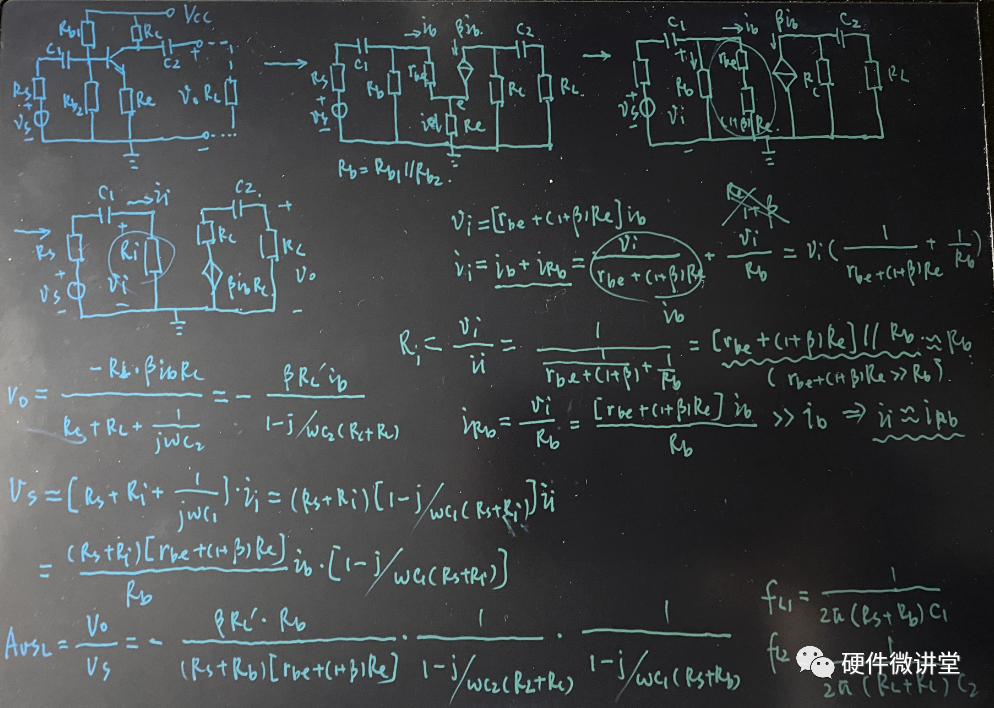

于是,就有如下交流通流:

此时的Rb是Rb1//Rb2并联后的简化。由于发射极电阻Re的存在,使得这个交流通路不是很直观,需要做进一步简化。把Re分别折算到输入回路和输出回路。

如上图所示,Re折算到输入回路,变成了等效电阻(1+β)Re。而在输出回路,由于连接的是受控电流源,电流源的内阻本身已经是无穷大,可以暂且忽略Re在输出回路的影响(这是基于个人理解给出的解释)。

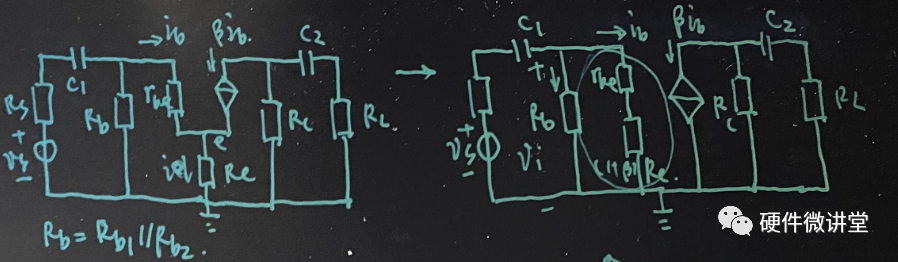

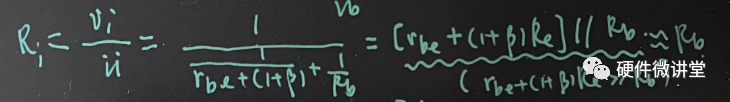

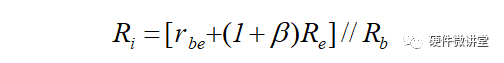

为了让电路更加直观,我们做进一步简化。在输入回路,C1右侧的电阻简化为Ri。在输出回路,根据诺顿定理讲受控电流源β*ib转换受控电压源β*ib*Rc,输出回路的等效电压源的内阻也变成了Rc,如上图所示。

注意:在电路中Re=2k,Rb=Rb1//Rb2=18k,β如果取值200,rbe暂且不算,已经有(1+β)Re>>Rb。那[rbe+(1+β)Re]//Rb的值应趋近于Rb,所以有:Ri近似约等于Rb。

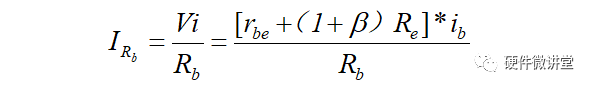

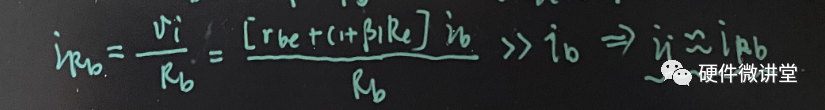

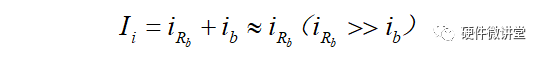

讨论完Ri,我们再看下输入回路的电流Ii。rbe+(1+β)Re上的电压Vi=Ib[rbe+(1+β)Re]。由于Rb和rbe+(1+β)Re是并联关系,则Rb两端电压也是Vi。

于是,可以求得:

由于rbe+(1+β)Re和Rb的两端电压都是Vi,rbe+(1+β)Re>>Rb,则有:

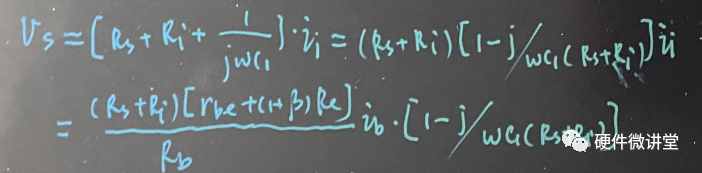

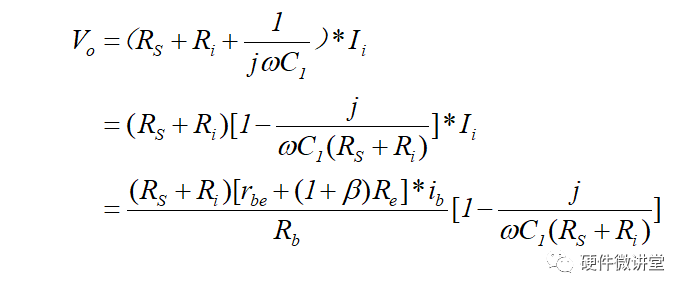

计算完Ri和Ii,我们可以开始求解Vs。

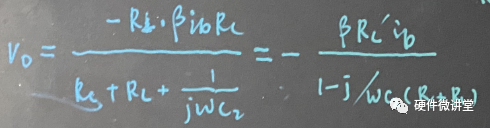

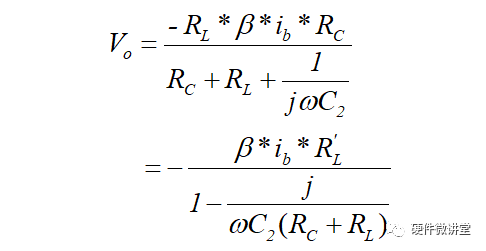

求解Vo:

备注:RL'=Rc//RL。

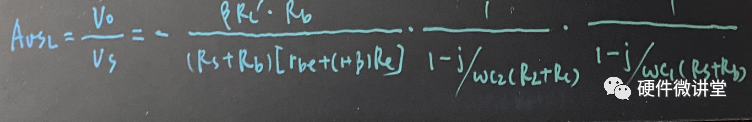

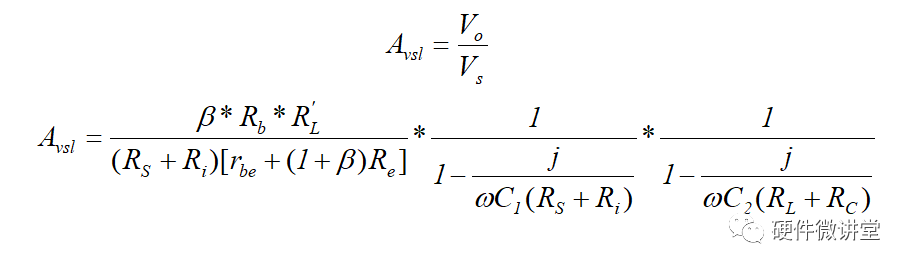

再求解Avsl:

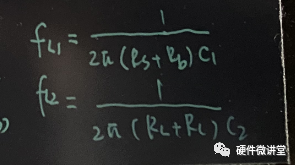

这样的话,可以得到两个低频截止频率fL1和fL2。

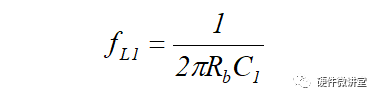

针对Vs,由于没有设置Rs,那么fL1=1/2π*Rb*C1。这个不就是文章开头《晶体管电路设计(上)》书中的计算公式么!而且Rb正是Rb1//Rb2。

把整个推导过程的手写版本,全部放出来:

特别说明:上面的推导仅限于上图中的电路。如果在Re上并联一颗大电容,推导出来的Avsl计算公式又不一样了,请具体问题具体分析。

TINA-TI仿真

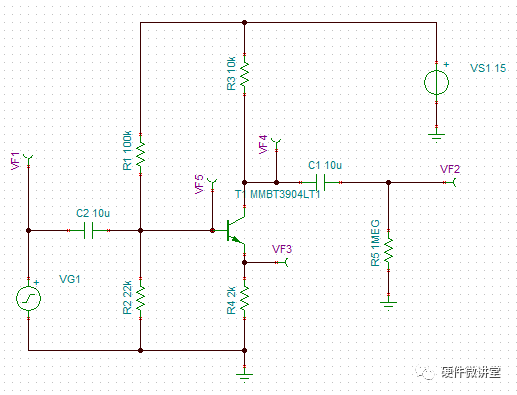

还是用这个共射极放大电路,老粉儿应该不陌生,已经用了多次。

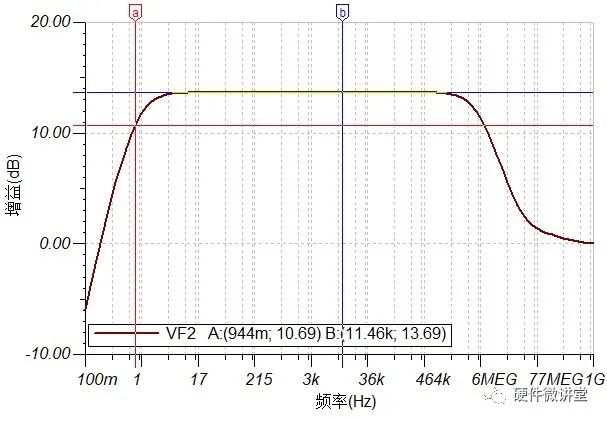

在前一篇文章中,仿真频率响应得到的幅频曲线是这样的:

为什么这里面没有体现出高通滤波的特性呢?

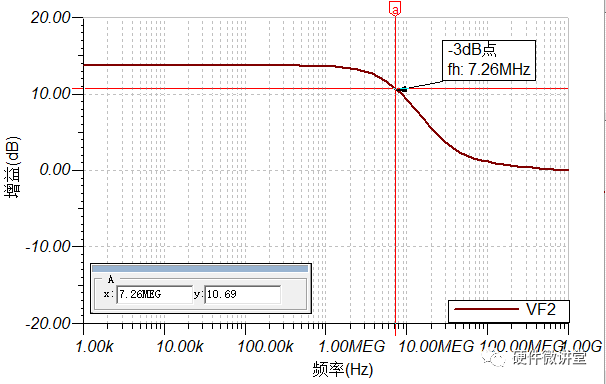

这是因为起始频率设置的太高。如果我们把起始频率设置为0.1Hz,再仿真看看。如下图所示,中频带的增益是13.69,在下降3dB后,在低频区对应的频点是944mHz,即0.9Hz。这也正好和计算的fL1=1/2π*Rb*C1=0.9Hz能对应上。

总 结

写到这里,终于把前面共射极放大电路低频截频计算方法说清楚了。

现在梳理下今天讨论的内容:

①CE放大电路的低频等效电路及其低频截频fh推导过程;

②用TINA-TI仿真CE放大电路的低频带的幅频响应;

怎么样?一个简短的问题,给出的回答可浅可深。我的助攻只能到这里,能否晋升到陆地神仙境,一剑开天门,就看你的造化了!

截止今天,三极管相关的文章已经8篇,也差不多。后面打算盘一下Mos管。有好的问题,可以在文末留言。

关注“硬件微讲堂”,硬件路上不慌张!