超异构芯片最近是比较火的一个名词,其集中特性是将各类不同的芯片内核进行融合,这种集成式芯片设计可以充分整合芯片资源,进一步提升数据计算效率。并且由于芯片在设计之初就打通了相互之间互通兼容性,其内部功能划分和交互统一构建的逻辑优化,相比单芯片功能方案而言,可以显著降低彼此功能和交互的各种掣肘;并且很多设计原理图上可以在芯片之间通过共享某些资源,融合型单芯片可以进一步降低成本。另外,对于自动驾驶系统设计而言,(80%-90%)的轻量级场景+10%左右的挑战场景+10%左右的极端场景需要提供高性能以行业领先的功率/性能比计算传统和深度学习算法,这些完全可以通过超异构的不同芯片核进行覆盖,充分降低复杂度和系统规模。

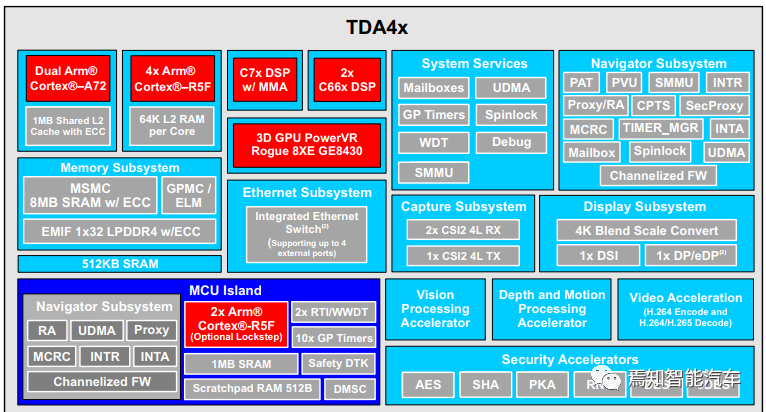

超异构芯片是具有高水平的系统集成,以实现先进汽车的可扩展性和更低成本的支持集中式 ECU。关键核心包括具有标量和矢量内核的下一代 DSP,专用深度学习的NN计算核和传统算法加速器,用于通用计算的最新 ARM 和 GPU 处理器,集成的下一代生成成像子系统 (ISP),视频编解码器,以太网集线器和隔离的 MCU 功能安全岛,所有受保护汽车级安全和安保硬件加速器等。一般情况下,除了芯片选型外,设计超异构芯片时需还要满足如下设计规则:- 内置自检 (BIST) 、故障注入CPU 和片上RAM

- 运行时安全诊断、电压、温度和时钟监控,窗口化看门狗定时器,用于存储器的 CRC 引擎完整性检查

- 可用于应用的功能安全需要满足 ISO26262 要求的ASIL D

- 启用需要大量数据的系统带宽、PCIe 集线器和千兆以太网交换机以及 CSI-2 端口以支持许多传感器输入的吞吐量。

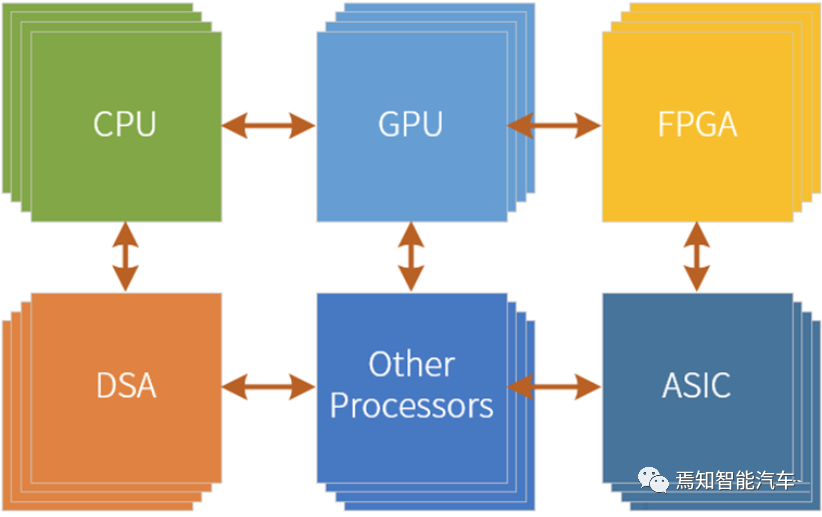

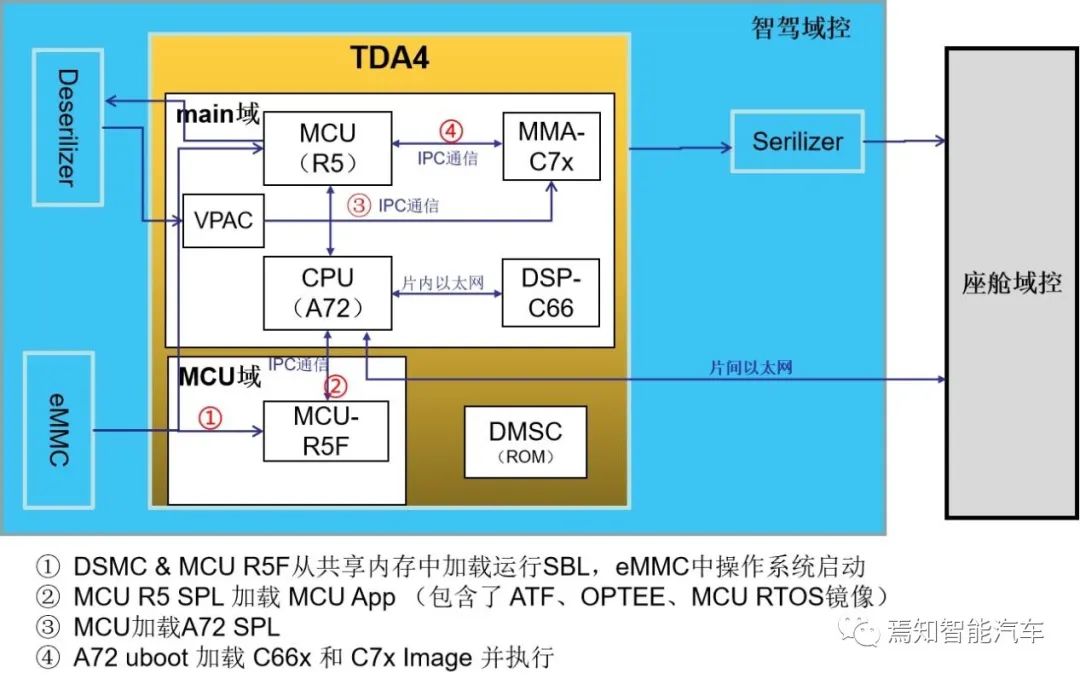

对于超异构芯片而言,一般是基于异构、可扩展的架构开发,多核异构的优点是各核充分发挥其处理效能的优点,再加上专用硬件加速器也可处理特定任务,从而在性能、功耗和成本上达到最佳平衡。当前被各厂家广泛使用比较成熟的超异构芯片当属TI的Jacinto™ 7 家族的处理器了,当然这也只是初级超异构芯片。不同厂家对其使用方式不完全一致,有将其完全作为SOC芯片使用的,充分使用了其上的AI算力,有些厂家在不太考虑其安全等级要求的情况下也可能将其当做MCU来使用。本文将以TI的这块TDA4的芯片为例进行详细介绍,说明相应的内部架构。相当于异构芯片域控的MCU芯片单元所起的作用,用于启动底层硬件驱动、同步时间,启动操作系统及顶层应用软件中控制执行类部分逻辑运算。这里MCU域主要是指MCU Island中用于锁步功能的Arm Cortex-R5F充当;TI这类超异构芯片而言,CPU模块(Cortex R5F)用于对SOC域核周边对应的模块需要单独进行电压和时钟设计,同时,采用专用内存和接口确保其能够与更大的 SoC 隔离。此类模块通常使用高度定制化的NN加速器来实现。在环境感知模块中都会涉及大量的典型神经网络(NN)的运算,过程中深度学习算力主要被消耗掉。包括常见的各类图像、激光点云检测算法,比如物体检测、车道线检测、红绿灯识别等。以TI为例设计的异构芯片中,微处理器系统端包括:Arm® Cortex®-A72和Arm® Cortex®-R5F、C71、C66几大模块。其中,在各家域控Tier1开发过程中一般会考虑在A72上运行HLOS(如Linux或QNX),其余核则运行RTOS,整个运行核均可支持AutoSar。使用A72独立双核集群配置有助于多操作系统应用对软件管理程序的最低需求。R5F子系统支持低级时序关键处理任务,用于实时性要求比较高的硬件驱动。使用C71(MMA)进行深度学习神经网络NN和模型运算,所以说MMA主要计算单位主要是以Tops为计算单位。DSP处理器(C66)功能包含前端和后端视觉处理两方面。前端视觉主要是NV12转BGR、环视拼图,后端进行浮点运算用以充当AI加速器的CNN后处理。如上这种结构是一种典型的AI运算模块(又称为AI-DSA),适用于对AI运算性能要求高,算法相对稳定的情况。由于AI-DSA模块在整个智能驾驶场景运算上使用更为普遍,性能更加敏感,对于云端、边缘计算及自动驾驶几段场景的工程化落地更加具有可使用性。用于图像处理加速单元,包含大量浮点运算和实现动态 3D 渲染以增强观看效果应用程序。同时GPU域也可以认为是高效率的AI运算平台,对于异形场景CornerCase的适配计算效率是最高的。如上如果兼顾执行效率和执行性能上,可以做自适应的AI算力分配,普通场景的AI运算可以采用常规CPU+DSA方式进行,而特殊边缘场景可以采用GPU加速核方式进行高效能计算。VENC/ VDEC用于视频编解码单元,通常高性能的超异构芯片需要适配H.265/HEVC这类高清视频编码器。对于下一代自动驾驶系统来说可以提供更高清的视频编码能力,实现高清视频压缩传输。VPAC(Vision

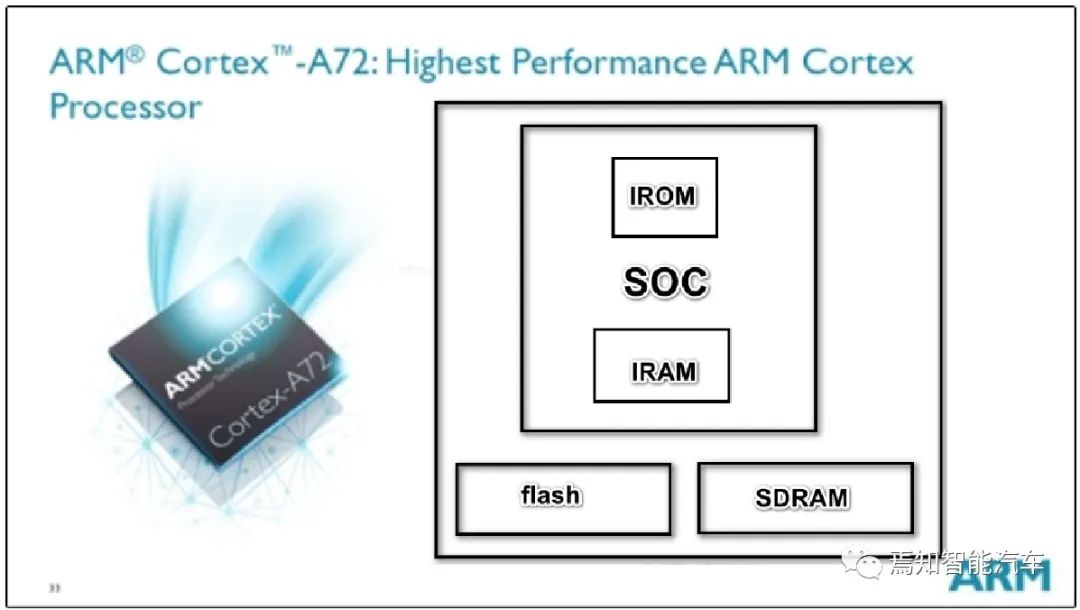

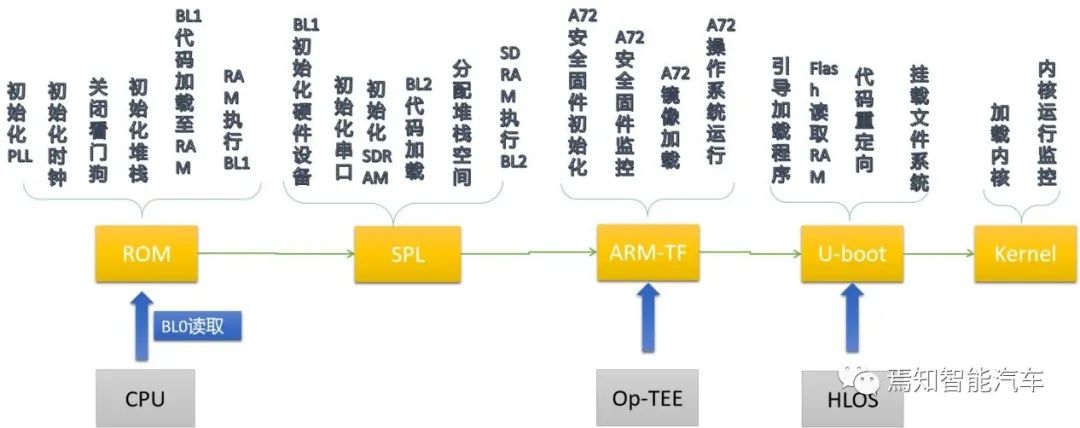

Processing Accelerator)用于对图像进行去畸变、下裁剪(Crop)、重整型(Resides)。其目的是确保输入给神经网络单元进行处理的图像已经被初步处理过了,这样可以提升图像网络处理速度和性能。如下图是以简单的图像传输和处理可以讲清楚在这一类超异构芯片上如何进行数据链路的传输和处理。下图是大多数开发板所有的一个存储单元框架,接下来以此图为基础描述ARM芯片的上电启动流程。ROM:芯片内部固化存储代码的存储器,其中固化在芯片iROM中的启动代码为BL0。RAM:在ROM启动运行的时候,只有RAM是可用的,因此必须要自动从外扩存储器(nand/sd/usb)中拷贝的uboot.bin二进制文件的头最大16K(一般是4K或8K)代码(BL1)。SDROM:芯片外部的运行内存,由运行在RAM上的BL1进行初始化,用于运行BL2与应用程序。Nand Flash :芯片外部非易失闪存技术的存储器,没有地址总线,不能直接运行代码,需要将代码加载到RAM上面才能运行。就举例的TDA4芯片而言,BL1 和 BL2 没有被集成(Jacinto7集成 了 DMSC&MCU R5 取代了 BL1 和BL2 的功能), BL31 执行 ATF,BL32 执行 OP-TEE,BL33 是SPL/U-boot。相应的存储单元涉及Main域和MCU域的管理,且两域分别单独用于片上共享存储单元,他们分别通过多核共享存储控制器MSMC实现相应的存储管理。TDA4内部还存在LPDDR4 w/ECC模块,即使未使用 DDR 接口,其VDDS_DDR均需要使用 LPDDR4 电压范围进行供电。对于超异构芯片而言,由于采用了多核异构的架构,因系统需求的差异,其相应的启动流程也有一定的差异性,并且由于集成多核制会导致其启动流程比单核和多核同构的处理器会复杂些。Bootloader 是在操作系统运行之前执行的一段小程序。通过这段小程序,我们可以初始化硬件设备、建立内存空间的映射表,从而建立适当的系统软硬件环境,为最终调用操作系统内核做好准备。两种bootloader 可以选择 SPL (Secondary Program Loader)或 SBL(Secondary bootloader)两种驱动加载。SPL表示程序加载,分为两级加载程序过程。第一级Bootloader是指从ROM 里面的程序中根据启动方式的选择引导并加载 SPL。第二级Bootloader是指对硬件的初始化过程,引导下一级的 bootloader 核或加载并运行应用程序。SBL表示驱动加载。可以实现对外围设备进行配置,比如 DDR,可以加载并启动其它核。为了满足快速启动 MCU 执行相关的应用,MCU可以先启动,然后使用BOOT APP 进而引导其它应用程序。在 SBL 启动流程中,SBL 可以直接加载 Linux内核和 DTB。如下图显示了完整的异构芯片TDA4的程序加载过程。对于如上超异构芯片而言,用的最广的要数ARM Cortex-A72核了,因为其在整数、浮点、内存等性能皆有不同程度的提升,虽然还缺少一些细节,不过IPC性能上相对于之前的产品提升了16-30%左右。如下图表示了芯片A72的具体启动原理。整个代码启动运行过程包括首先把BL1加载到RAM中运行,然后由BL1对SDRAM进行初始化。最后,代码重定向完成后在内存中执行的uboot的完整代码BL2。从应用层面的系统需求来讲,不同的应用可以部署在不同的核,不同核的启动时序影响着系统需求是否能实现。总体来讲,针对系统的应用需求,可能有如下的额外要求:提前Can信息响应、提前启动画面、提前启动摄像头、

提前分配Linux使用空间、提前显示视频动画等。我们应设计合理的 Soc 启动流程来满足系统的需求。

超异构芯片Super SOC作为ADAS系统普遍应用的处理器,在面向 ADAS 和自动驾驶车辆 (AV) 应用过程中起着举足轻重的作用。智驾领域中,SOC需要深度学习算法中会比传统芯片提供提供高性能计算能力,同时可以有效优化其功耗和系统集成度。最终实现支持集中式ECU 或多种传感器的高级汽车平台实现可扩展性和更低的成本。Simulink模型架构指导

揭秘理想的整车电子电气架构

如何一步一步成为一个技术领域专家

谈谈Bootloader自更新

谈谈对两家AUTOSAR工具看法

奥迪首款800V车型技术总览

CAN设计与应用指南

汽车软件需求是如何变成用户功能?

电子电气架构设计需要考虑哪些方面?

汽车E/E架构的网络安全分析

电子电气架构设计需要考虑哪些方面?

一文搞懂AUTOSAR的DEM模块深度解读汽车域控制器分享不易,恳请点个【👍】和【在看】