作者:Hong Han,AMD 赛灵思开发者

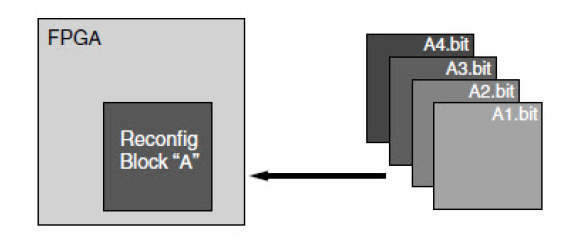

DFX流程的全称是Dynamic Fucntion eXchange, 过去曾被称为PR流程 (Partial Reconfiguration). 可以在保持一部分逻辑在正常工作、不断电的情况下,通过部分重配置替换掉其他的部分逻辑的功能。

如图所示,Reconfig Block A 所包含的逻辑在黑色框所在的区域,A1.bit~A4.bit对应的是Reconfig Block A的四种不同功能,通过加载四个bit文件其中一个文件来在线修改Reconfig Block A中的硬件功能。

在Vivado中,大多数的器件都可以支持DFX功能(Spartan-7 全系列, Artix-7 A12T 7A25T不支持)。

从Ultrascale/Ultrascale+器件开始,大多数类型的逻辑资源都可以放到动态区域内,使得DFX功能的应用场景大大增加。

DFX流程中的常用术语:

Bottom-Up Synthesis

按模块综合设计,无论是在一个工程(Project)中还是在多个工程中综合均可. 底层的模块采取out-of-context (OOC)模式综合,OOC综合会为每一个模块都生成一个独立的dcp文件,供上层模块调用。

在DFX的整个流程中动态逻辑和静态逻辑之间的边界必须严格锁定,绝对不允许跨边界优化. OOC综合可以在综合阶段确保不发生任何跨边界优化。

Programmable Unit (PU)

可供重配置的最小逻辑资源. Pu的大小随逻辑资源的类型而变化。

Reconfigurable Module(RM)

RM是RP中的网表或者HDL描述, 一个RP可以对应多个RM。

Reconfigurable Partition(RP)

RP可以理解为可重新配置分区. 被设置为RP的实例的HD.RECONFIGURABLE属性为true,在实现的各个步骤都会识别到RP的这个属性,从而在opt_design,place_design,phys_opt_design,route_design中继续严格锁定边界。

RP内的逻辑称为可重配逻辑或者动态逻辑。

Partition Pin

静态逻辑和动态逻辑之间的逻辑上( 物理上)的连接. 一般情况下,工具会自动创建,摆放和管理Partition Pin。

Configuration

Configuration是一个完整的设计,每个可重新配置分区 (RP) 都有一个 RM。

DFX 项目中可能有许多配置。每个配置为每个 RM 生成一个完整的 BIT 文件和一个部分 BIT 文件。

Static Logic(静态逻辑)

静态逻辑是指设计中所有不归属于RP,剩余的逻辑。

这部分逻辑不能参与动态重配置,即使设计在进行动态逻辑切换时,这部分逻辑也一直保持有效工作状态

通常静态逻辑又称为顶层逻辑

DFX在Vivado中的软件流程

DFX的设计流程和普通Vivado设计流程很相似,但是有其显著不同的地方.

下面我们一起来看一下DFX的设计流程:

分别综合Static Logic和RM

RM采用OOC模式综合 (synth_design -mode out_of_context …)

Static Logic采用普通模式综合

连接Initial configuration 所需要的网表 (Static+每个RP的一个RM)

划定动态区域的范围(创建相应的Pblock)

对于每个RP都把HD.RECONFIGURABLE属性设置为True.

例如:set_pproperty HD.RECONFIGURABLE true [get_cells XX_RP_inst]

对于完整的设计执行实现(Implementation)的所有必要流程

完成implementation之后,保存完成布线后完整设计的网表(routed.dcp)

把RM从完成布线后完整设计中去掉,保存只包含静态逻辑的网表(routed_bb.dcp)

锁定静态区的所有布局布线信息

把一个新的RM的综合后网表加入到静态区锁定的网表中,完成二次Configuration的Implementation.

重复上一步直到所有的RM都完成了Implementation

对于所有的Configuration执行PR 验证(pr_verification),确保在所有的Configuration中,静态区的逻辑以及动静边界都是一致的

为每一个Configuration创建各自的bitstream文件.

不论是工程模式,还是非工程模式,都会遵循以上流程,只不过在工程模式中部分流程工具会自动执行,没有显示地体现在命令行中. 在使用以上两种模式运行DFX设计,脑海中始终要清楚各个阶段的命令和输出文件在以上流程中的位置。