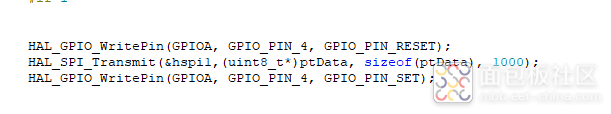

实验代码如下,在启动发送数据前,对GPIO口置位,方便查看从使能SPI到数据时钟起来的时候的时间间隔实验1:CPOL = 0,CPHA = 0

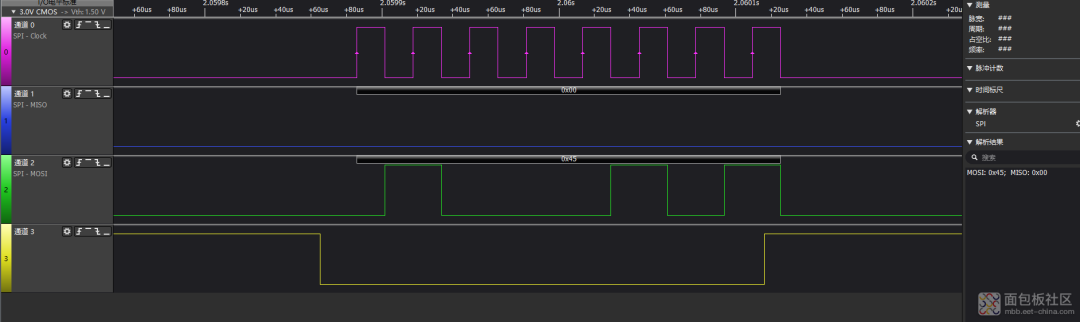

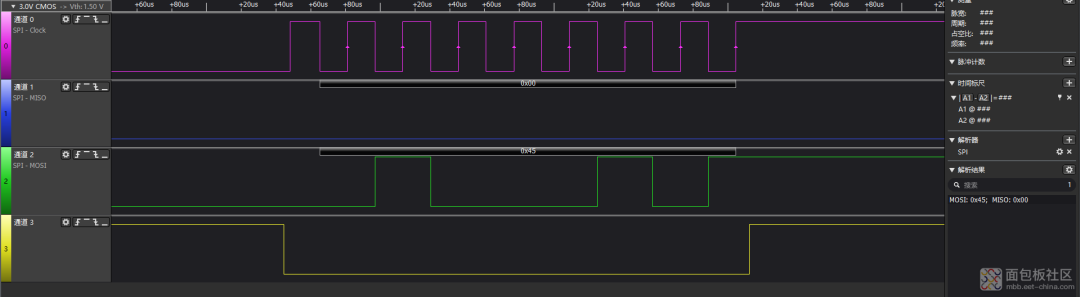

,逻辑分析仪抓数据可以看到,在使能SPI模块以后,隔了半个周期的时间,SPI的时钟开始动作,由于CPHA=0,在第一个时钟跳变沿开始采样数据。实验2:CPOL = 0,CPHA =

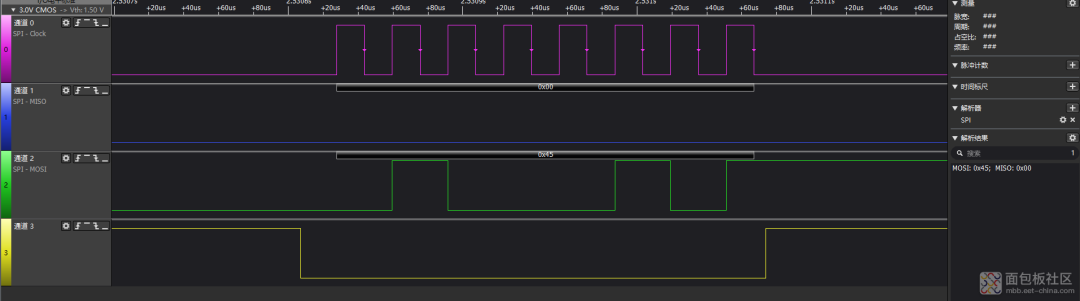

1,逻辑分析仪抓数据可以看到,在使能SPI模块以后,隔了半个周期的时间,SPI的时钟开始动作,由于CPHA=1,在第二个时钟跳变沿开始采样数据。实验3:CPOL = 1,CPHA =

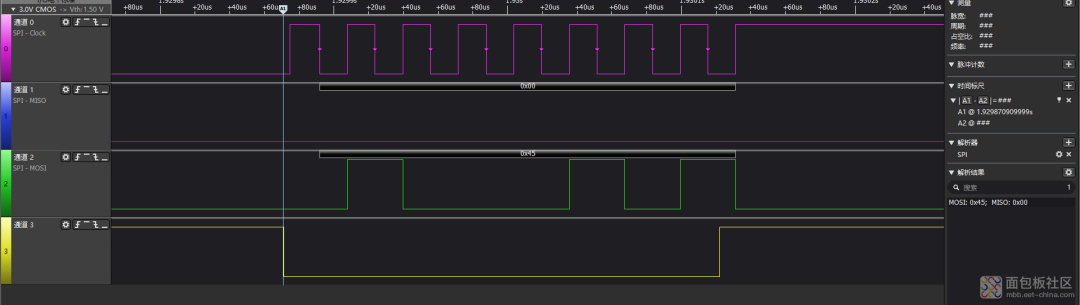

0,逻辑分析仪抓数据可以看到,在使能SPI模块以后,由于CPOL=1,空闲时候时钟为高电平,所有先拉高时钟,即使CPHA=0,第一个时钟跳变沿也是放弃采样,在第二个时钟跳变沿开始采样数据,也就说smt32固定有半个时钟周期是当作使能SPI模块以后,稳定通信的时间间隔。实验4:CPOL = 1,CPHA = 1,同理,也是在使能SPI模块以后,半个周期时间间隔,才从第二个(第三个)跳变沿采样时间作者:宏杰, 来源:面包板社区

链接:https://mbb.eet-china.com/blog/4027574-437007.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

您可以分享的内容:

1. 您设计的电路原理图

2. 针对您设计电路图进行说明分析

3. 可以从设计思路、电路分析及应用、优化、疑问等展开讨论

活动奖品:

一等奖:300元 京东E卡

优秀奖若干:50元 京东E卡

参与即得20元京东E卡奖励!

优秀参与者随机掉落“电路好书”!