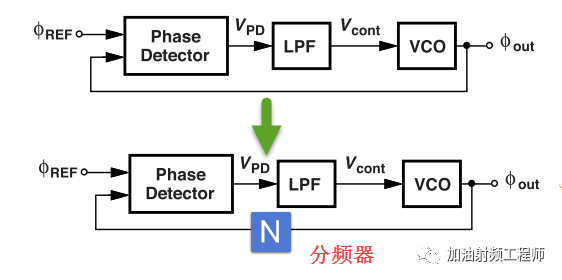

锁相环中的分频器,是一个神来之笔,有了这个分频器,一个PCB板上,只需要一个好晶振,就可以获得几乎任何频率的,而且指标优良的信号。

分频器放置于锁相环的反馈回路中,作用是将VCO的高频率信号以指定的分频倍数分频到参考频率,然后输入到鉴相器,与参考时钟,也就是晶振,进行比较。

频率低的分频器,可以用一个通用可编程计数器实现。

比如说,有一个计数器,它对输入时钟信号的上升沿进行计数,每计到N个上升沿,就输出一个上升沿,那么这个计数器就可以看做分频比为N的分频器。

但是这种通用可编程计数器只能在较低的频率下工作(通常在1GHz以下),所以就不满足我们射频上的需要了。而且,退一万步讲,就算频率上满足要求了,但是功耗性能也不是最优的。

分频器的输入端是锁相环中工作频率最高的电路,也是功耗最大的电路。

在射频锁相环的分频器设计中,按照工作频率,将整个分频器分为前端和后端两部分。

前端呢,负责高频信号的分频,将高频信号分频到较低频率。

后端呢,可以使用可编程计数器,进一步将信号分频至所需的频率。

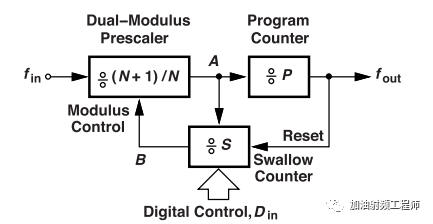

前端电路称为预定标器,最常用的是双模预定标器,即具有两个分频比为N或N+1的预定标器,常见的分频比有8或9,4或5等,分频比由一位输入控制信号来决定。

在现代锁相环中,经常用到的分频器是基于双模预定标器的双模分频器,如下图所示。

其中,预定标器由控制信号控制其分频比为N或者N+1,P和S为两个可编程计数器,这里分别设置为分频比P和S,并且满足P大于等于S。

双模分频器的工作原理是这样的:

(1) 在一个周期开始时,预定标器设定为分频比N+1,即每输入N+1个振荡器时钟沿,预定标器输出一个时钟沿给下面的计数器P和S。

(2) 当计数器S得到S个输入时钟沿时,因为S值通常小于P值,所以其首先输出一个时钟沿,然后停止计数。此时,分频器已接收到S(N+1)个振荡器时钟沿。

(3) S计数器的输出时钟沿,改变了预定标器的控制信号,预定标器分频比改变为N,

(4) 在P计数器接收到下(P-S)个预定标器输出时钟沿后,P计数器计数达到P,输出一个时钟沿,这意味着分频器又接收到(P-S)*N个振荡器时钟沿。

(5) P计数器的输出时钟沿重置整个分频器,一个分频器周期就结束了。

这样,在一个分频器周期内,总共接收到S(N+1)+(P-S)N,也就是PN+S个振荡器时钟沿,这样就实现了PN+S的分频比,其中P大于或等于S。

这样的话,只要改变S的值,就可以使分频比以1的步进变化。