关键词:硬件,概览

1、引言

本应用笔记为系统开发者概述了开发板特性的硬件实现。开发板特性为供电电源、时钟管理、复位控制、自举模式设置和调试管理。

本文档详细介绍了如何使用 STM32U575xx 和 STM32U585xx 微控制器(也称为 STM32U575/585)。其中介绍了使用这些 MCU开发应用程序所需的最少硬件资源。

本文还包括了详细的参考设计原理图,说明了其主元件、接口和模式。

本文档适用于基于 Arm®的 STM32U575/585 微控制器。

2、电源管理

2.1 电源

STM32U575/585 器件要求 1.71 至 3.6 V 的工作电压电源(VDD)。

下面列出的独立电源可用于特定外设:

提示 如果 VDDA 引脚保持为高阻抗或连接至 VSS,则可施加到 I/O(具有"_a" I/O 结构)上的最大输入电压将降低(参见器件数据手册以了解更多详细信息)。

提示 – 如果有两个 VCAP 引脚(UFBGA169 封装),则每个引脚必须连接至 2.2 µF 电容(总量约为 4.4 µF)(最大 4.7 µF)。每个 VCAP 还需要一个 100 nF 陶瓷电容。

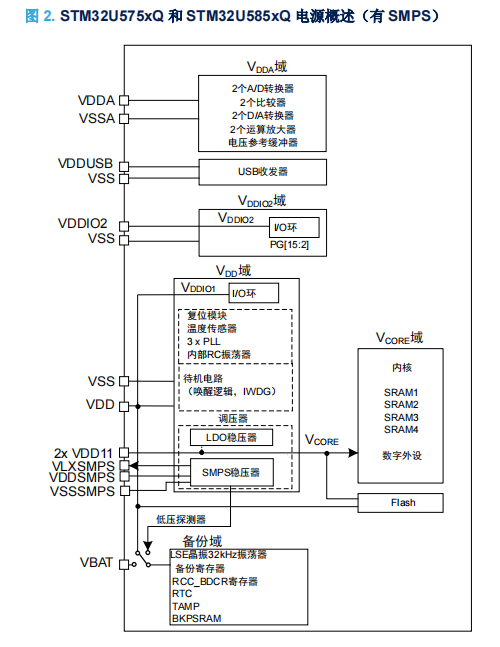

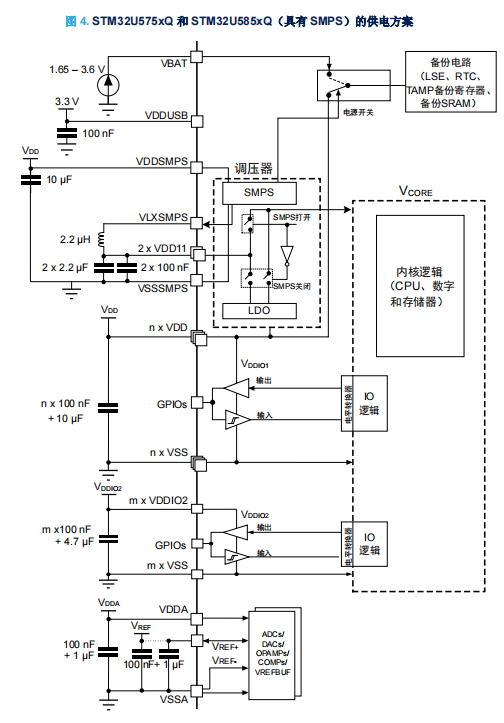

– SMPS 电源引脚(VLXSMPS、VDD11、VDDSMPS、VSSSMPS)仅在具有 SMPS 的封装上可用。在此类封装中,STM32U575/585 器件并联嵌入了两个稳压器(一个 LDO 和一个 SMPS),以便为数字外设提供VCORE 电源。VDD11 引脚上需要总 4.7 μF 的外部电容和 2.2 µH 线圈。此外,每个 VDD11 引脚需要一个100 nF 陶瓷电容。

– Flash 由 VCORE 和 VDD 供电。

提示 如果 VDDUSB 引脚保持为高阻抗或连接至 VSS,则可施加到 I/O(具有"_u" I/O 结构)上的最大输入电压将降低(参见器件数据手册以了解更多详细信息)。

提示 在小封装上,VDDA、VDDIO2 或 VDDUSB 独立电源可能不作为专用引脚出现,且内部连接至 VDD 引脚。如果产品上不支持某功能,则该功能也不会出现。

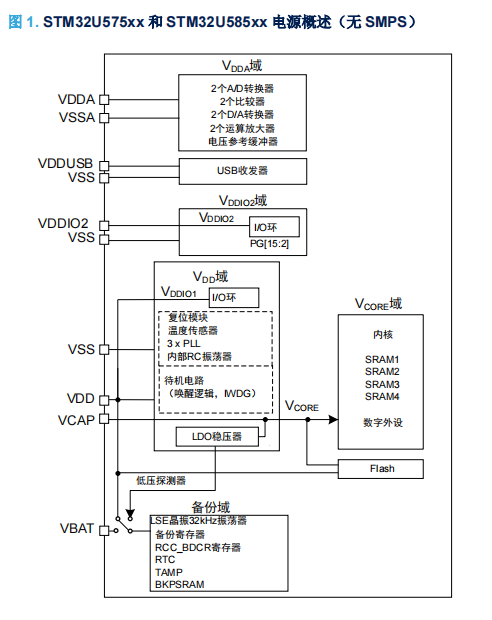

在无 SMPS 的器件中,I/O 和系统模拟外设(如 PLL 和复位模块)由 DD 电源供电。为数字外设和存储器供电的VCORE 电源由 LDO 生成。

提示 如果选定的封装具有 SMPS 降压转换器选项,但 SMPS 不被应用程序使用(而是使用嵌入式 LDO),则建议设置 SMPS 电源引脚,如下所示:

• 将 VDDSMPS 和 VLXSMPS 连接至 VSS

• 将 VDD11 引脚通过两个(2.2 µF + 100 nF)电容连接至 VSS(如在正常模式下)

2.1.1 独立模拟外设电源

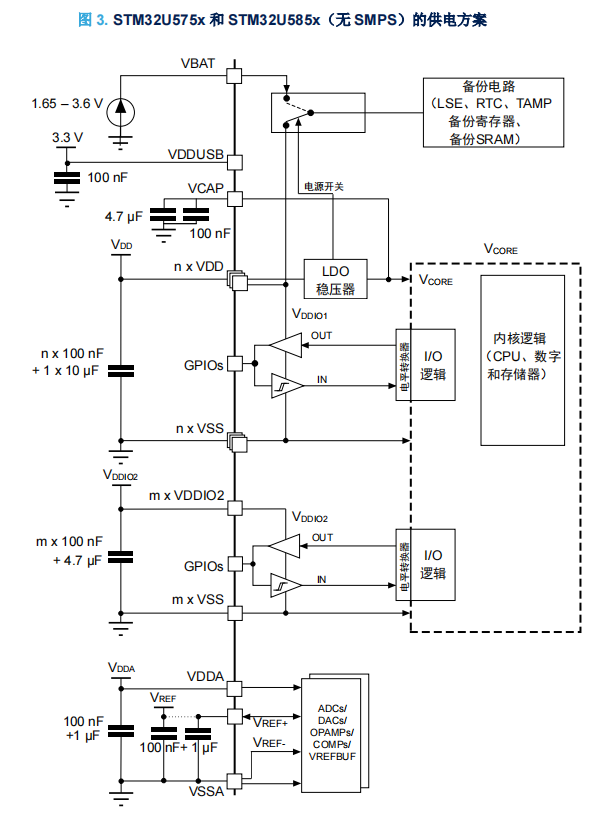

为了提高 ADC 和 DAC 转换精度、扩展供电的灵活性,模拟外设配有独立电源,可以单独滤波并屏蔽 PCB 上的噪声。

模拟外设的电压电源输入在单独的 VDDA 引脚上可用。VSSA 引脚提供了独立的电源接地连接。

VDDA 电源电压可与 VDD 不同。复位后,由 VDDA 供电的模拟外设是逻辑隔离且电隔离的,因而不可用。当 VDDA电源存在时,使用这些外设前,必须通过设置 PWR_SVMCR 寄存器中的 ASV 位,解除此隔离。

VDDA 电源可由模拟电压监测(AVM)监控,并与两个阈值(AVM1 为 1.6 V,而 AVM2 为 1.8 V)进行比较。有关更多详细信息,请参见器件数据手册和参考手册的“外设电压监测(PVM)”部分。

当使用单供电时,VDDA 引脚可外部连接至同一 VDD 电源,为得到无噪声的 VDD 参考电压,需通过外部滤波电路。

ADC 和 DAC 参考电压

为确保低电压输入和输出上的更好精度,用户可将 VREF+连接至一个独立的、低于 VDDA 的参考电压源。

对于模拟输入 (ADC)或输出 (DAC)信号, VREF+为最高电压,以满量程值表示。VREF+可由外部参考或VREFBUF(可以输出可配置电压:1.5、1.8、2.048 或 2.5 V)来提供。VREFBUF 还可通过 VREF+引脚为外部元件提供电压。

有关更多信息,请参见器件数据手册和参考手册的“电压参考缓冲器(VREFBUF)”部分。

2.1.2 独立 I/O 电源轨

来自端口 G(PG[15:2])的一些 I/O 由单独的电源轨供电。此轨的电源范围为 1.08 V 至 3.6 V,可通过 VDDIO2 引脚外部提供。VDDIO2 电压电平完全独立于 VDD 或 VDDA。

VDDIO2 引脚仅可用于一些封装(参见数据手册中的引脚排列详细信息,以了解 I/O 列表)。

复位后,由 VDDIO2 供电的 I/O 是逻辑隔离且电隔离的,因而不可用。当 VDDIO2 电源存在时,从 PG[15:2]使用任一I/O 前,必须通过设置 PWR_SVMR 寄存器中的 IO2SV 位,解除此隔离。

VDDIO2 电源由 VDDIO2 电压监测(IO2VM)监控且与内部参考电压(3/4 VREFINT,约为 0.9 V)进行比较。有关更多详细信息,请参见器件数据手册和参考手册的“外设电压监测(PVM)”部分。

2.1.3 独立的 USB 收发器电源

USB 收发器通过一个单独的电源 VDDUSB 供电。VDDUSB 范围从 3.0 V 到 3.6V,完全独立于 VDD 或 VDDA。

复位后,由 VDDUSB 供电的 USB 功能是逻辑隔离且电隔离的,因而不可用。当 VDDUSB 电源存在时,使用 USB OTG 外设前,须通过设置 PWR_SVMR 寄存器中的 USV 位,解除此隔离。

VDDUSB 电源由 USB 电压监测(UVM)监控且与内部参考电压(VREFINT,约为 1.2 V)进行比较。有关更多详细信息,请参见器件数据手册和产品参考手册的“外设电压监测(PVM)”部分。

2.1.4 电池备份域

为了在 VDD 掉电时,还能保留备份寄存器的内容,且为 RTC 供电,可将 VBAT 引脚连接到电池或者其他备用电源

上。

VBAT 引脚为 RTC、TAMP、LSE 振荡器和 PC13 到 PC15 I/O 供电,允许 RTC 在主电源关闭时也可工作。

当在 PWR_BDCR1 寄存器中设置 BREN 位时,可通过 VBAT 引脚为备份 SRAM 供电。

VBAT 电源的开关由复位模块中内置的掉电复位电路进行控制。

Caution:

提示 • 由于电源开关仅能传递有限的电流(3 mA),因此使用输出模式的 PC13 到 PC15 I/O 受限:速率必须限制在2 MHz,最大负载为 30 pF。这些 I/O 不能作为电流源使用(如,驱动 LED)。

• 在 VDD 下,TAMP_OUTx 引脚(PE3、PE4、PE5、PE6、PA0、PA1、PC5)与其连接到的 GPIO 保持相同的速度特性。但是,在 VBAT 下,TAMP_OUTx 引脚的速度必须限制为 500 kHz。

• 在 VDD 或 VBAT 下,PC13 引脚的速度必须始终限制为 2 MHz。

备份域访问

系统复位后,备份域(RCC_BDCR、PWR_BDCR1、RTC、TAMP、备份寄存器及备份 SRAM)将受到保护,以防止意外的写访问。要使能对备份域的访问,请按以下步骤进行操作:

1. 通过在 RCC_AHB3ENR 寄存器中设置 PWREN 位,使能电源接口时钟。

2. 在 PWR_DBPR 寄存器中设置 DBP 位,使能对备份域的访问。

VBAT 电池充电

当 VDD 存在时,可通过 5 kΩ 或 1.5 kΩ 的内部电阻为 VBAT 上的外部电池供电,具体取决于 PWR_BDCR2 寄存器中的 VBRS 位。

可通过在 PWR_BDCR2 中设置 VBE 位来使能电池充电。在 VBAT 模式下自动禁用。

2.1.5 调压器

STM32U575/585 器件并联嵌入了以下内部调节器,以便为数字外设、SRAM1/2/3/4 和嵌入式 Flash 存储器提供VCORE 电源:

• SMPS 降压转换器

• LDO(线性电压稳压器)

可以在应用程序运行时进行选择,具体取决于应用需求。SMPS 可降低功耗,但 SMPS 产生的噪音可能会影响一些外设行为,需要应用程序在运行外设时切换至 LDO,以达到最佳性能。

除了待机电路和备份域,LDO 或 SMPS 可用于所有电压调节范围(范围 1/2/3/4)、所有停止模式(停止 0/1/2/3)

和待机模式(有 SRAM2)(参见参考手册中的“低功耗模式总结”表)。

无 SMPS 的 STM32U575/585 器件仅嵌入了 LDO 稳压器,该稳压器可控制所有电压调节范围和功耗模式。

动态电压调节管理

LDO 和 SMPS 稳压器可提供四种不同的电压(电压调节),且可在所有停止模式下工作。这两种稳压器均可在以

下范围操作:

通过 PWR_VOSR 寄存器中的 VOS[1:0]字段选择电压调节。

Caution:

在将范围 1 和范围 2 中的系统时钟频率增加至超过 50 MHz 之前,必须启用EPOD(嵌入式功率分配)加速器且使其就绪(有关在电压调节范围之间切换的顺序,参见参考手册)。

2.1.6 I/O 模拟开关的供电

一些 I/O 嵌入模拟开关,用于模拟外设(ADC、COMP、DAC)和 TSC(触摸感应控制器)功能。默认情况下,这些开关由 VDDA 供电,但可以由 VDDA 升压器或 VDD 供电,具体取决于 SYSCFG_CFGR1 寄存器中 ANASWVDD

和 BOOSTEN 位的配置。

建议在 VDDA、VDDA 升压器和 VDD 之间以最高电压值为 I/O 开关供电。

提示 如果可能,选择噪音通常较小的 VDDA 或 VDDA 升压器,而非 VDD。TSC 功能的模拟开关由 VDD 供电。

2.2 电源方案

器件通过稳定的 VDD 电源供电,如下所述:

Caution:

如果有两个 VCAP 引脚(UFBGA169 封装),则每个引脚必须连接至 2.2 µF(典型值)电容(总量约为 4.4µF)。

提示

• SMPS 和 LDO 稳压器同时提供 VCORE 电源,具体取决于应用需求。但是,同时只能有其中一个稳压器为有效。当 SMPS 有效时,它在通过 SMPS VLXSMPS 输出引脚提供的两个 VDD11 引脚上向 VCORE 馈电。然后,在每个 VDD11 引脚上需要一个 2.2 µH 线圈和 2.2 μF 电容。LDO 在有效时向 VCORE 供电并使用

VDD11 引脚上的相同去耦电容对其进行调节。

• 需要在每个 VDD11 引脚/焊球附近添加一个 100 nF 的去耦电容。

2.3 VDDA、VDDUSB、VDDIO2 和 VDD 之间的供电排序

2.3.1 电源隔离

器件具有强大的复位系统,该系统可确保主电源(VDD)在释放 MCU 复位之前达到有效的工作范围。

此复位系统还负责隔离独立的电源域:VDDA、VDDUSB、VDDIO2 和 VDD。此复位系统由 VDD 供电且在 VDD 达到最低电压(在最差条件下为 1 V)之前不工作。

为了避免在可用电源和 VDD(或接地)之前泄漏电流,在下电期间必须先将 VDD 供应至 MCU,最后再释放(有容差)(参见第 2.3.3 节 )。

2.3.2 一般要求

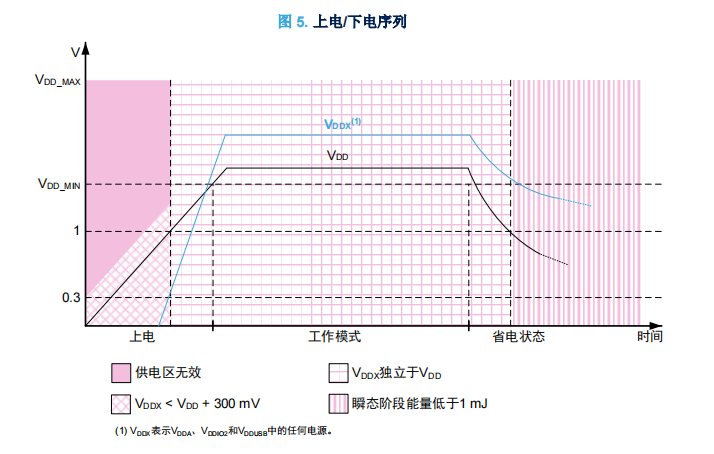

在上电和下电阶段,必须遵守以下电源序列要求:

• 当 VDD 低于 1 V 时,其他电源(VDDA、VDDIO2 和 VDDUSB)必须保持低于 VDD + 300 mV。

• 当 VDD 超过 1 V 时,所有电源均为独立。

提示 VBAT 是独立的电源且没有限制与 VDD。所有电源干线可连接到一起。

2.3.3 下电阶段的特定条件

在下电阶段,VDD 仅在为 MCU 提供的能量仍低于 1 mJ 时暂时低于其他电源。这使外部去耦电容在下电瞬态阶段以不同的时间常量放电(参见图 5)。

VDDX(VDDA、VDDIO2 或 VDDUSB)电源轨必须在 DD 之前关闭。

提示 在下电瞬态阶段,VDDX 可仍临时超过 VDD(参见图 5)。

下电阶段向 MCU 提供能量的计算示例

如果 VDDX 上的去耦电容总和为 10 μF 且 VDD 降至 1 V 以下,而 VDDX 仍为 3.3 V,则去耦电容中的剩余能量为:

E = ½ C x V2 = ½ x 10-5 x 3.32 = 0.05 mJ

去耦电容中的剩余能量低于 1 mJ,因此,可接受 MCU 对其进行吸收。

2.4 复位和电源监控

2.4.1 欠压复位(BOR)

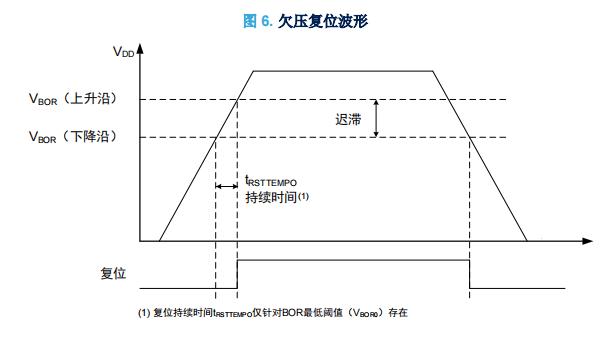

器件具有欠压复位(BOR)电路。除关断模式外,BOR 在所有功耗模式下均激活,且不可禁用。BOR 监测备份域电源电压,即在存在时为 VDD,不存在时为 VBAT。

通过选项字节,可对 5 个 BOR 阈值进行选择。

上电期间,BOR 将使器件保持复位状态,直到电源电压 VDD 达到指定的 VBORx 阈值。当 VDD 降至所选阈值以下时,将使器件复位。当 VDD 高于 VBORx 上限时,释放器件复位,系统可以启动。

有关欠压复位阈值的详细信息,参见数据手册的电气特性部分。

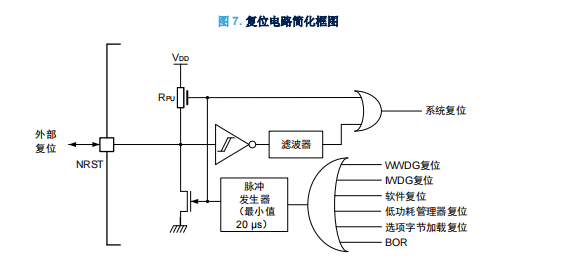

2.4.2 系统复位

除了寄存器 RCC_CSR 中的复位标志和备份域中的寄存器外,系统复位会将其它全部寄存器都复位为复位值。

只要发生以下事件之一,就会产生系统复位(参见参考手册以了解更多详细信息):

• NRST 引脚低电平(外部复位)

• 窗口看门狗事件(WWDG 复位)

• 独立看门狗事件(IWDG 复位)

• 软件复位

• 低功耗模式安全复位

• 选项字节加载复位

• 欠压复位

这些源均作用于 NRST 引脚,该引脚在时延阶段中始终保持低电平。通过启动选项字节选择复位服务入口向量。

芯片内部的复位信号会向 NRST 引脚上输出一个低电平脉冲。脉冲发生器可确保每个内部复位源的复位脉冲都至少

持续 20 µs。对于外部复位,在 NRST 引脚处于低电平时产生复位脉冲。

内部复位情况下,内部上拉 RPU 失效,从而节约功耗。

2.4.3 备份域复位

只要发生以下事件之一,就会产生备份域复位:

备份域复位仅影响 LSE 振荡器、RTC 和 TAMP、备份寄存器、备份 SRAM、RCC_BDCR 和 PWR_BDCR1 寄存器。

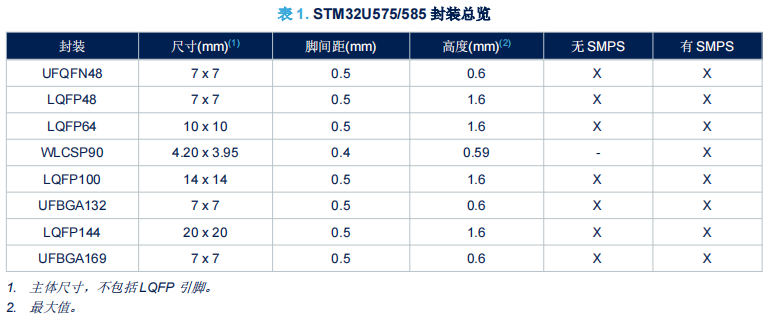

3、封装

3.1 封装总览

封装选择必须考虑一些主要取决于应用的限制。

下面汇总了最常见的一些限制:

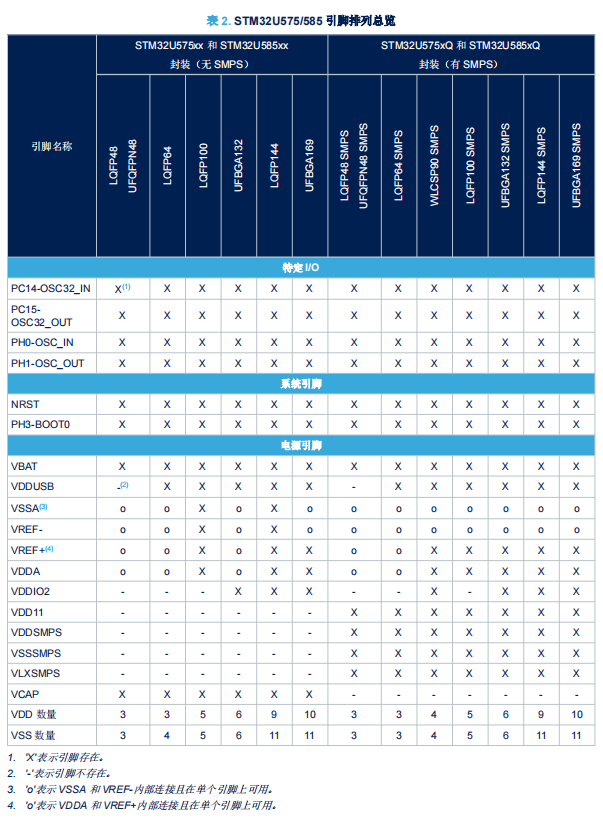

3.2 引脚排列总览

Caution: 在上表的几乎所有电源引脚中,有 SMPS 和无 SMPS 的 STM32U575/585 封装彼此无法兼容。

示例:在有 SMPS 的封装上,VDDIO2 为引脚号 130。而在无 SMPS 的封装上,引脚 130 映射到 VSS 引脚。这意味着在 SMPS 插座上安装传统封装时,系统短路。

4、时钟

可以使用下列时钟源来驱动系统时钟 (SYSCLK):

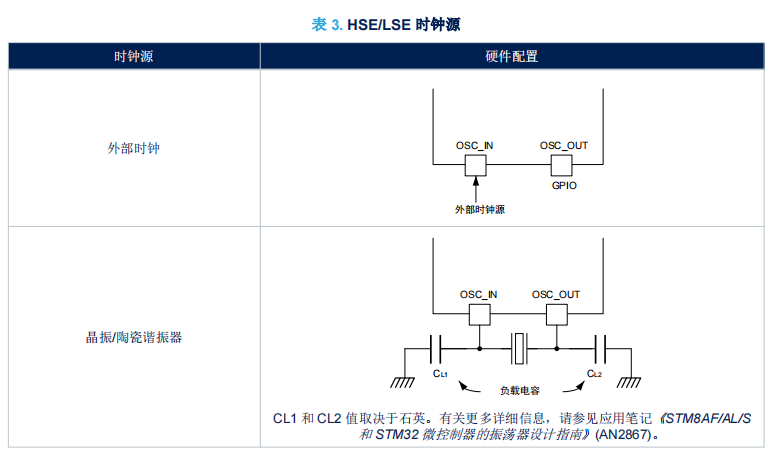

4.1 HSE 时钟

高速外部时钟信号(HSE)有以下几个时钟源:

谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选振荡器的不同做适当调整。

4.1.1 外部晶振/陶瓷谐振器(HSE 晶振)

4 到 50 MHz 外部振荡器的优点是可以生成一个精度非常高的主时钟。相关的硬件配置如表 3 所示。有关详细信息,请参见数据手册的电气特性部分。

4.1.2 外部时钟源(HSE 旁路)

在此模式下,必须提供外部时钟源,频率高达 50 MHz。必须使用占空比约为 40%至 60%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC_IN 引脚,具体取决于频率(参考数据手册),同时 OSC_OUT 引脚可用作 GPIO

使用(请参见表 3)。

提示 有关引脚可用性的详细信息,请参见数据手册的引脚排列部分。要最大程度降低功耗,建议采用方波信号。

4.2 HSI16 时钟

HSI16 时钟信号是从 16 MHz 内部 RC 振荡器生成的。HSI16 RC 振荡器以低成本提供时钟源(无需使用外部元件)。它还比 HSE 晶振具有更快的启动时间。但即使校准后,频率也不如外部晶振或陶瓷谐振器的频率精度高。

HSI16 时钟还可作为备份时钟源(辅助时钟)使用,以防 HSE 晶振发生故障。

有关更多详细信息,请参见参考手册的“时钟安全系统(CSS)”部分。

4.3 MSI(MSIS 和 MSIK)时钟

MSI 由四个内部 RC 振荡器组成:MSIRC0 (48 MHz)、MSIRC1 (4 MHz)、MSIRC2 (3.072 MHz)和 MSIRC3 (400kHz)。每个振荡器提供一个预分频器,从而提供 1、2、3 或 4 分频。

由这些分频振荡器生成两个输出时钟:

可由软件分别使用 RCC_ICSCR1 寄存器中的 MSISRANGE [3:0]和 MSIKRANGE [3:0]字段(且 MSIRGSEL = 1)来调整 MSIS 和 MSIK 频率范围。提供十六个频率范围,由四个内部 RC 生成(参见参考手册以了解更多详细信息)。

如果 HSE 晶振发生故障,则 MSI 时钟还可作为备份时钟源(辅助时钟)(参见参考手册中的“时钟安全系统(CSS)”部分)。

MSI 振荡器可提供一个低成本(无外部元件)低功耗的时钟源。此外,当和 LSE 一起用于 PLL 模式时,MSI 可提供一个非常精确的时钟源,该时钟源可用于 USB OTG-FS 外设,并且向 PLL 反馈,使系统以最大速率 160 MHz 运行。

利用 LSE 进行硬件自动校准(PLL 模式)

当应用中存在 32.768 kHz 外部振荡器时,MSIS 或 MSIK 可配置为 PLL 模式。此模式已启用,如下所示:

• 对于 MSIS:在 RCC_CR 寄存器中将 MSIPLLEN 位置为 1

• 对于 MSIK:在 RCC_CR 寄存器中将 MSIPLLEN 位置为 0

如果 MSIS 和 MSIK 范围是从同一 MSIRC 源生成的,则 PLL 模式应用于 MSIS 和 MSIK。当配置为 PLL 模式时,

MSIS 或 MSIK 可利用 LSE 自动校准。该模式可用于所有 MSI 频率范围。48 MHz 时,处于 PLL 模式的 MSIK 可用

于 USB OTG FS 器件,不需要外部高速晶振。

关于如何测量 MSI 频率偏移的更多详细信息,参见参考手册的“利用 TIM15/TIM16/TIM17 的内部/外部时钟测量”部

分。

4.4 LSE 时钟

LSE 晶振是 32.768 kHz 低速外部晶振或陶瓷谐振器(参见表 3)。它为 RTC(实时时钟)外设提供低功耗且精度高的时钟源,用于时钟/日历或其他定时功能。

使用 RCC_BDCR 寄存器中的 LSEDRV[1:0]位,可在运行时更改晶振驱动强度,以实现稳定性、短启动时间和低功耗之间的最佳平衡。

外部时钟源(LSE 旁路)

在此模式下,必须提供频率高达 1 MHz 的外部时钟源。必须使用占空比约为 50%的外部时钟信号(方波、正弦波或三角波)来驱动 OSC32_IN 引脚,同时 OSC32_OUT 引脚可以作为 GPIO 使用(参见表 3)。

5、自举配置

5.1 启动模式选择

启动时,可通过 BOOT0 引脚、nBOOT0 和NSBOOTADDx[24:0]/SECBOOTADD0[24:0]选项字节来选择启动存储

器地址,启动地址包括:

BOOT0 值可能来自 PH3-BOOT0 引脚或选项位,具体取决于在需要时释放 GPIO 焊盘的用户选项位的值。

当通过复位 TZEN 选项位(TZEN = 0)禁用 TrustZone®时,启动空间如下表中详述。

当通过设置 TZEN 选项位(TZEN = 1)启用 TrustZone 时,启动空间必须位于安全区域。SECBOOTADD0[24:0]选项字节用于选择启动安全内存地址。可通过设置 BOOT_LOCK 选项位选择唯一的启动条目选项。所有其他启动选项将被忽略。

下表详细介绍了启用 TrustZone 时的自举模式。

5.2 嵌入式加载程序和 RSS

嵌入式自举程序位于系统存储器中,由意法半导体在生产阶段编程。它被用来通过使用下列串行接口之一重新编程:

有关 STM32 加载程序的更多详细信息,请参见应用笔记《STM32 微控制器系统存储器自举模式》(AN2606)。

RSS(根安全服务)嵌入在名为“安全信息块”的 Flash 存储区,在 ST 生产期间编程。

例如,RSS 使用 RSS 扩展固件(RSSe SFI)启用 SFI(安全固件安装)。当生产被分包给第三方时,该特性允许客户保护烧写到 STM32 器件的固件的机密性。参照应用笔记安全固件安装(SFI)概述(AN4992)。

在通过 TZEN 选项位启用 TrustZone 后,RSS 在所有器件上可用。

6、调试管理

串行线/JTAG 调试端口(SWJ-DP)是 Arm 标准 CoreSight™调试端口。

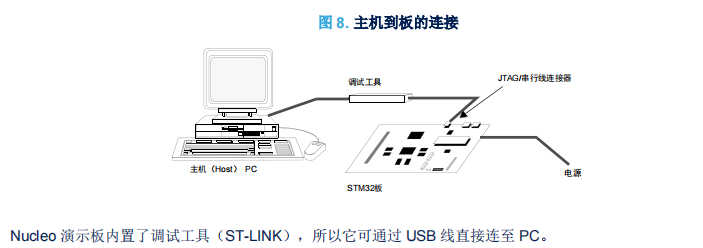

主机/目标接口为连接主机与应用板的硬件设备。此接口由三部分组成:硬件调试工具、串行线连接器,以及连接主机与调试工具的电缆。

下图显示了主机到开发板的连接。

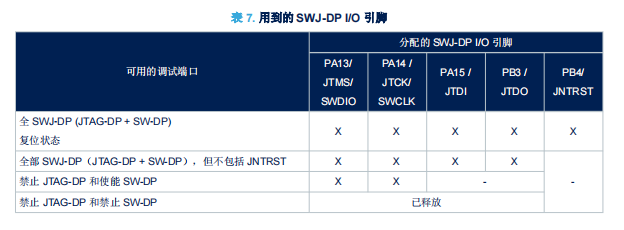

6.1 SWJ-DP(串行线和 JTAG 调试端口)

SWJ-DP 整合了:

在 SWJ-DP 中,SW-DP 的 2 个 JTAG 引脚与 JTAG-DP 的 5 个 JTAG 引脚中的部分引脚复用。

提示 所有 SWJ-DP 端口 IO 都可以通过软件重新配置为其他功能,不过在这种情况下不能再进行调试。

6.2 引脚排列和调试端口引脚

器件的不同封装有不同的有效引脚数。因此,一些与引脚可用性有关的功能可能会因封装不同而不同。

6.2.1 SWJ-DP 引脚

五个引脚被用作 SWJ-DP 的输出,作为 GPIO(通用 I/O)的复用功能。所有封装(如下表详述)都提供这些引脚。

6.2.2 灵活的 SWJ-DP 引脚分配

复位(SYSRESETn 或 PORESETn)后,将用于 SWJ-DP 的全部 5 个引脚指定为专用引脚,可供调试工具立即使用。

提示 除非由调试工具明确编程,否则不分配跟踪输出。

下表显示释放一些引脚的多种可能性(有关更多详细信息,参见参考手册)。

6.2.3 JTAG 引脚上的内部上拉和下拉电阻

JTAG 输入引脚不得悬空,因为这些引脚直接连接到用于控制调试模式功能的触发器。还必须特别注意SWCLK/TCK 引脚,该引脚直接连接到一些触发器的时钟。

为避免 I/O 电平浮空,器件在 JTAG 输入引脚上嵌入以下内部电阻:

用户软件释放 JTAG I/O 后,GPIO 控制器便会重新对其进行控制,然后,软件可将这些 I/O 作为标准 GPIO。

GPIO 控制寄存器的复位状态会将 I/O 置于以下同等状态:

提示 JTAG IEEE 标准建议在 TDI、TMS 和 nTRST 上增加上拉电阻,但对 TCK 没有特殊建议。然而,就器件而言,针对 JTCK 采用了集成的下拉电阻。由于带有上拉和下拉电阻,因此无需添加外部电阻。

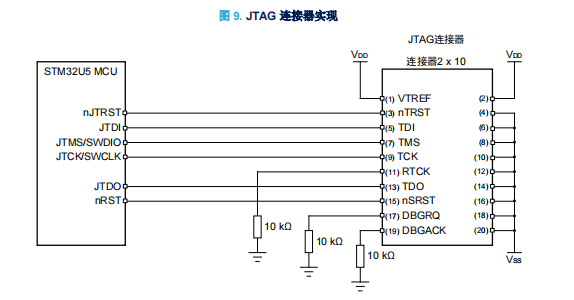

6.2.4 使用标准 JTAG 连接器的 SWJ-DP 连接

下图显示了器件和标准 JTAG 连接器之间的连接。

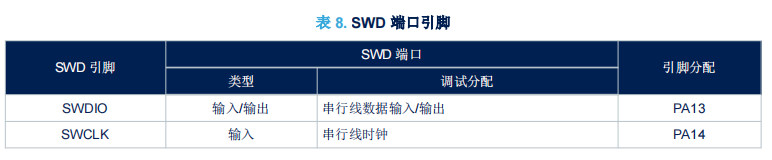

6.3 串行线调试 (SWD) 引脚分配

所有封装(如下表详述)都提供相同的 SWD 引脚分配。

复位后,将用于 SWD 的引脚指定为专用引脚,可供调试工具立即使用。

但是,MCU 为禁用 SWD 提供了可能,因此可释放相关引脚供 GPIO 使用。

有关如何禁用 SWD 端口的更多详细信息,请参见参考手册的“I/O 引脚复用功能复用器和映射”部分。

6.3.1 SWD 引脚上的内部上拉和下拉

用户软件释放 SWD I/O 后,GPIO 控制器便会控制它。GPIO 控制寄存器的复位状态会将 I/O 置于同等状态:

由于带有上拉和下拉电阻,因此无需添加外部电阻。

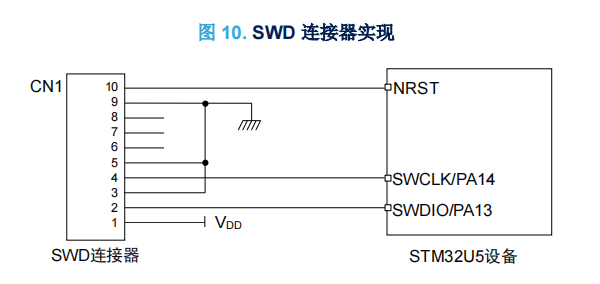

6.3.2 使用标准 SWD 连接器的 SWD 端口连接

下图显示了器件和标准 SWD 连接器之间的连接。

7、 建议

7.1 PCB(印刷电路板)

由于技术原因,最好使用多层 PCB 的单独一层专用于接地(VSS),另一层专用于 VDD 供电。

这提供了不错的去耦和屏蔽效果。对于很多应用,由于经济原因不能使用此类板。在这种情况下,主要要求就是要

确保接地和供电有良好的结构。

7.2 元件位置

PCB 的初始布局必须将电路分为不同模块:

7.3 接地和供电

必须遵守与接地相关的以下规则:

为提高模拟性能,用户必须对 VDD 和 VDDA 使用单独的电源,将去耦电容放置在离器件尽可能近的位置。

供电(VSS、VDD、VSSA、VDDA、VDDUSB、VDDIO2 或 VDDSMPS)必须靠近地线实现,以最小化供电环的面积。这是因为供电环起到了天线及 EMI 主发收的作用。所有无元件的 PCB 区域都必须填充额外的接地,以创造屏蔽环境(尤其是当使用单层 PCB 时)。

7.4 去耦

所有供电和接地引脚都必须适当连至供电电源。这些连接(包括焊盘、线和过孔)都必须有尽可能低的阻抗。典型情况下,这可通过使用粗的线宽做到,最好在多层 PCB 中使用专用供电层。

此外,每个供电电源对都必须使用滤波陶瓷电容(100 nF)及约 10 µF 的钽电容或陶瓷电容去耦,两个电容并联在器件上。

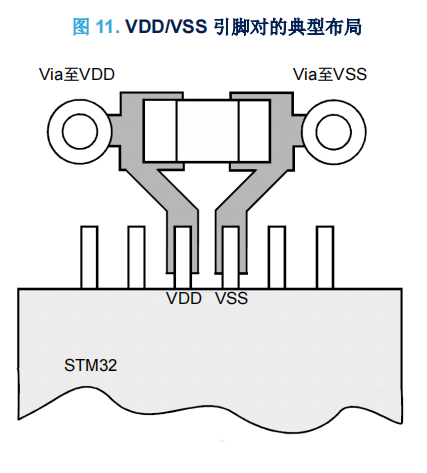

在某些封装中,多个 VDD 引脚使用同一个 VSS 引脚,而不是一对电源引脚(每个 VDD 对应一个 VSS)。这种情况下,电容必须处于每个 VDD 引脚和公共 VSS 引脚之间。这些电容必须放置在 PCB 尽可能接近适当引脚的位置,或在这些引脚下面 PCB 的底层。其典型值为 10 至 100 nF,但准确值取决于应用需要。

下图显示了这种 VDD/VSS 引脚对的典型布局。

7.5 其它信号

当设计应用时,可通过仔细研究以下几点来提高 EMC 性能:

7.6 不使用的 I/O 和特性

所有微控制器都是为多种应用设计的,通常一个应用不会使用 100 %的 MCU 资源。

为了提高 EMC 性能和避免额外功耗,器件不使用的功能必须禁用且与时钟树断开连接,如下所示:

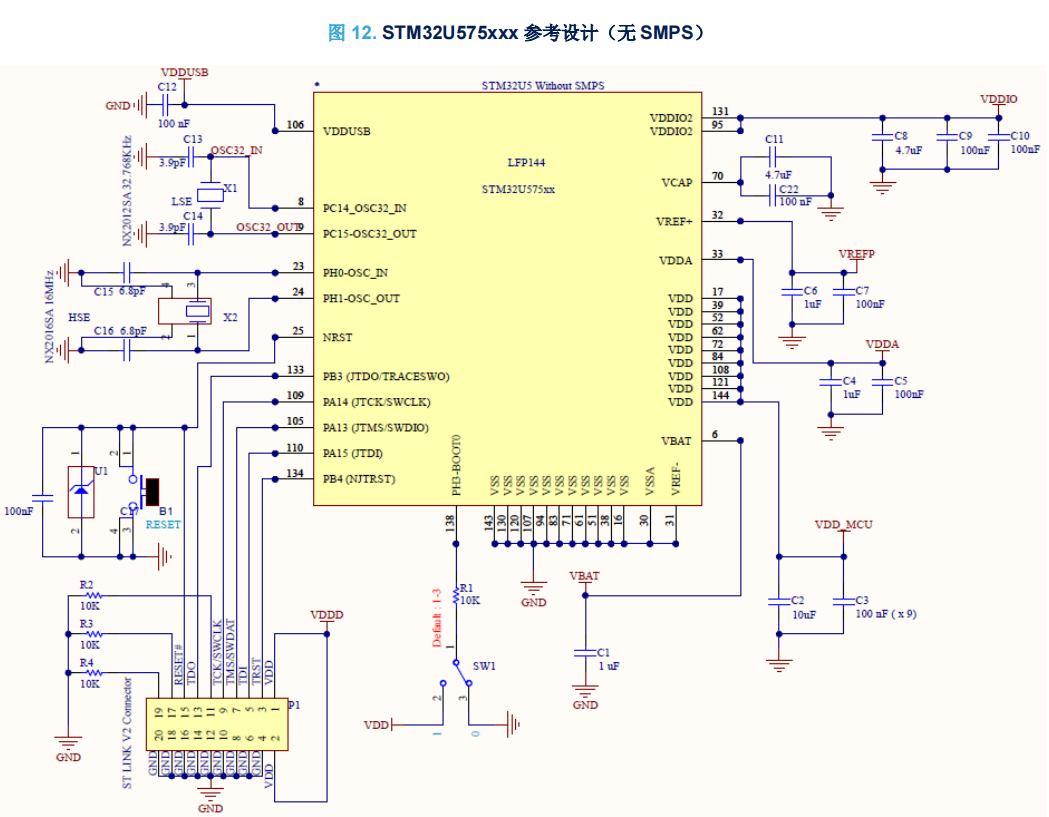

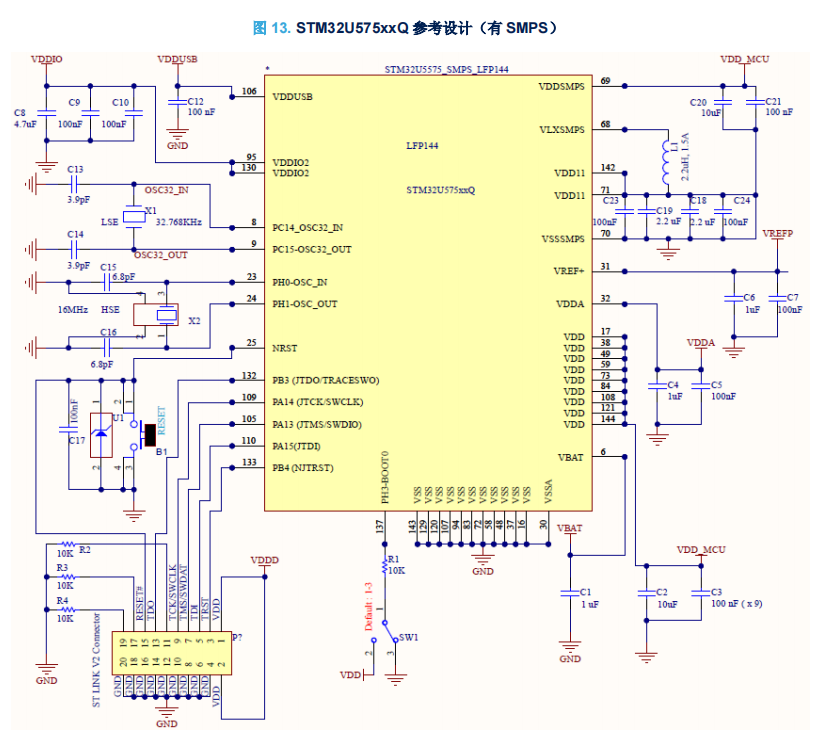

8、 参考设计

8.1 说明

下图中显示的参考设计基于 LQFP144 中的 STM32U575/585 器件。使用第 8.2 节 中给出的引脚对应关系,可将不同封装的任何 STM32U575/585 器件定制此参考设计。

时钟

两个时钟源用于 MCU(参见第 4 节 以了解更多详细信息):

• LSE:X2 - 32.768 kHz 晶振用于嵌入式 RTC

• HSE:X1– 16 MHz 晶振,用于 MCU

更多详细信息,参见第 4 节 。

复位

复位信号在第 8.2 节 中显示的参考设计图中为低电平有效。

复位源包括:

更多详细信息,参见第 2.4 节 。

自举模式

用户可以在板上添加一个开关,以更改自举选项。

更多详细信息,参见第 5 节 。

提示 当从待机模式唤醒时,BOOT 引脚被采样,且用户必须注意其值。

SWD 接口

参考设计显示了 STM32U575/585 器件和标准 SWD 连接器之间的连接。

更多详细信息,参见第 6 节 。

提示 建议连接复位引脚,以便能从工具复位应用。

电源

更多详细信息,参见第 2 节 。

8.2 元件参考

下表列出了 STM32U5 参考设计的组件(基于 STM32U5 Nucleo 板):

© THE END

▽点击“阅读原文”,可下载原文档