如果参考平面上有间隙,然后信号穿过该间隙,会在PCB中产生很多不良性能。比如:

EMI发射增加,EMI抗扰度受损,串扰增加,信号上升时间的恶化等。

但是,你说有影响就有影响了?咱还得眼见为实,是不是。

接下来,就来看一看实测数据吧!

参考平面有缝隙,会产生共模电流,进而使EMI发射增加

当信号下方的参考平面有间隙时,可能会导致系统电缆上产生共模(CM)干扰电流,从而导致辐射EMI发射。

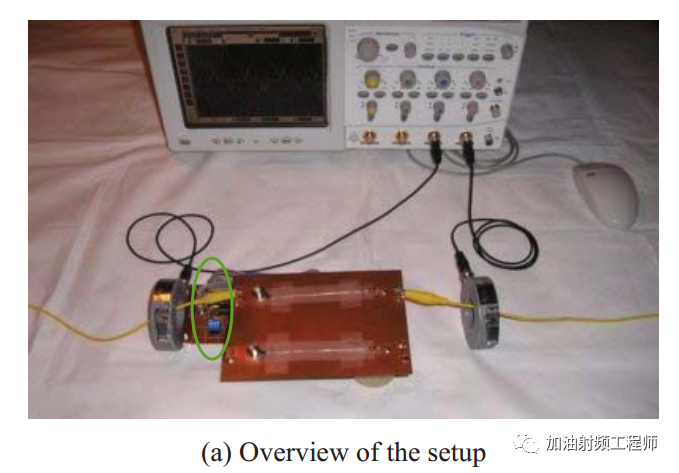

测试系统如下图所示。

首先, 一个工作频率约为 30 MHz、信号边沿速率约为 2 纳秒、振幅约为 3 V 峰峰值的小型振荡器通过短 BNC 耦合器耦合到上图的测试板(猜测是绿色方框里面的是振荡器,耦合器应该在背后,因为现在图片上正对着的是BNC插座芯的那一边)。

然后,用一对 2 米长的导线通过鳄鱼夹夹到电路板两侧的参考平面。

最后,通过一对匹配电流探头测量这些导线中产生的 CM 电流。

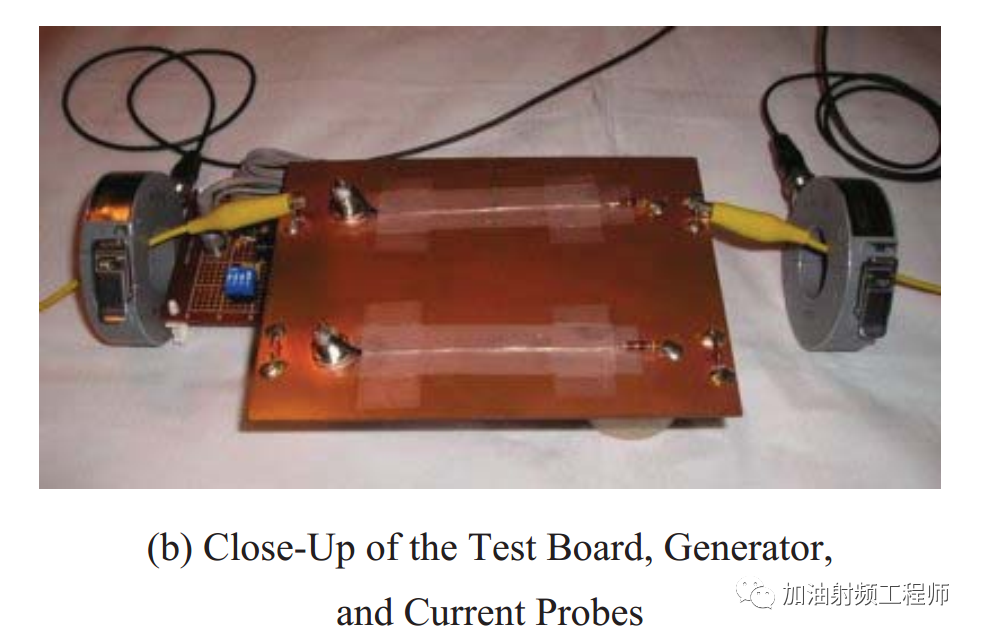

测试板、发生器和电流探头的特写如下图所示。

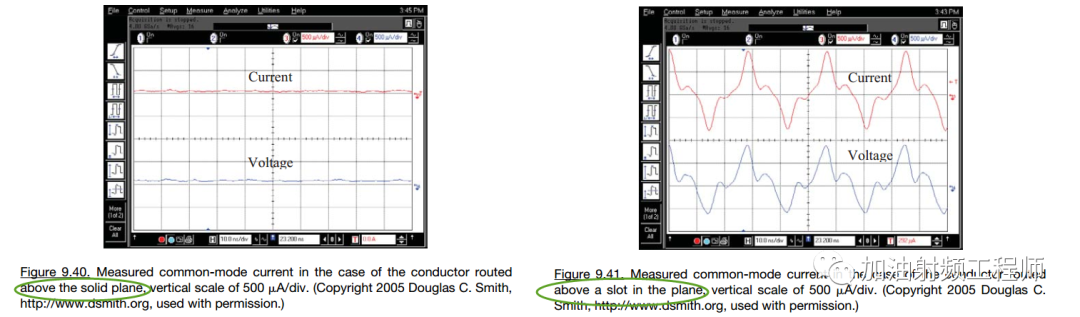

下图显示了在 2 米长的导线上测得的共模电流,左侧是实心参考平面的结果,右侧是带缝隙的参考平面的结果(感觉图中,是不是应该标注current1和current2,而不是current和voltage??)。可见,参考平面有缝隙的导线,测到的CM电流要大。

参考平面有缝隙,会使得PCB的EMI抗扰度下降

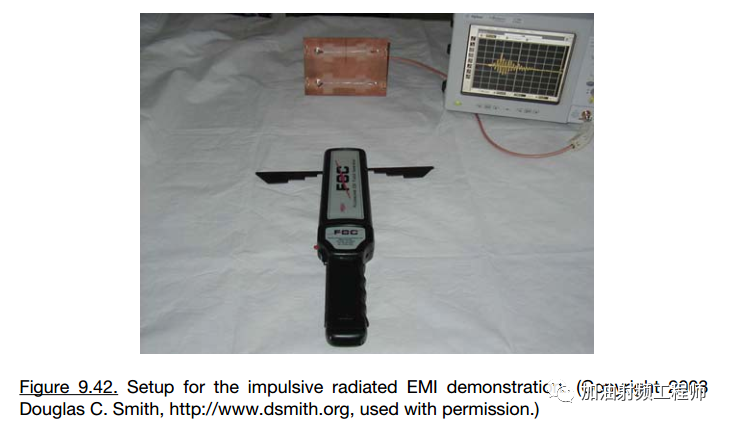

测试系统如下图所示。

测试板还是那块测试板,但是在距离其20厘米处,有一静电枪,对其进行低压静电放电(ESD的)。

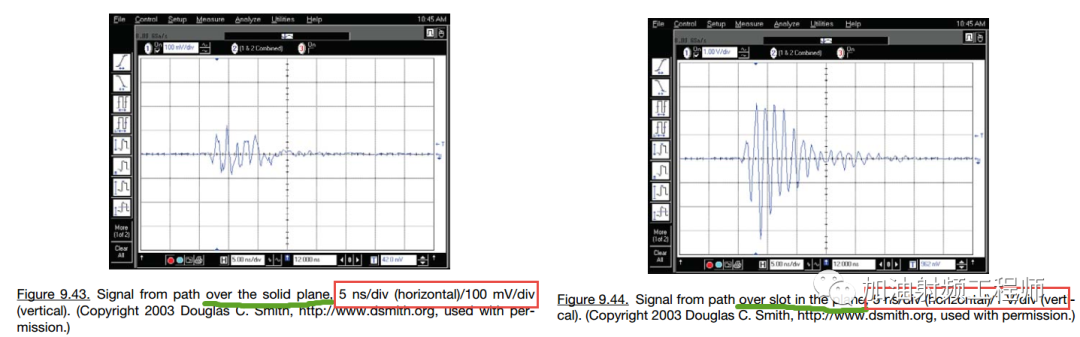

下图左侧,显示了在实体平面上布线的导体接收到的干扰信号。辐射干扰引起的信号幅度约为 100 mV,不足以破坏大多数数字电路的性能。

下图右侧,是参考平面有缝隙的导体接收到的干扰信号,幅度增加到3v左右 。足以对大多数数字电路的功能产生破坏。

由此证明了,在参考平面的缝隙上布线,对信号导体所产生的另一个不利影响,即更容易接收干扰信号。

这是因为,由信号导体和其在参考平面中的缝隙边缘周围产生的回流路径,形成了大环路,而这个大环路构成了一个高效的天线,有效地拾取了感应辐射干扰。

有间隙的参考平面会是一个串扰源

走线穿过参考平面经常导致的另一个问题是穿过间隙的导体之间的过度耦合(或串扰)。

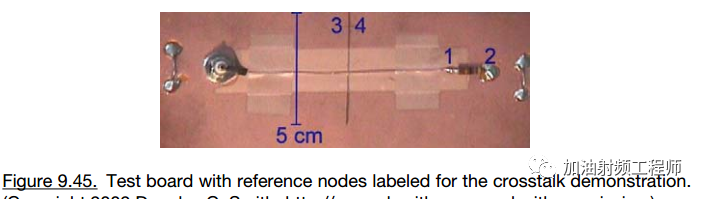

如下图所示。为上述测试板的一部分,上面有一条长约 12 cm 的导线(约 50 Ω),穿过参考平面中 5 cm 长的缝隙。然后在这个导线中灌入升时间约为 300 ps 的 300 mV 信号。

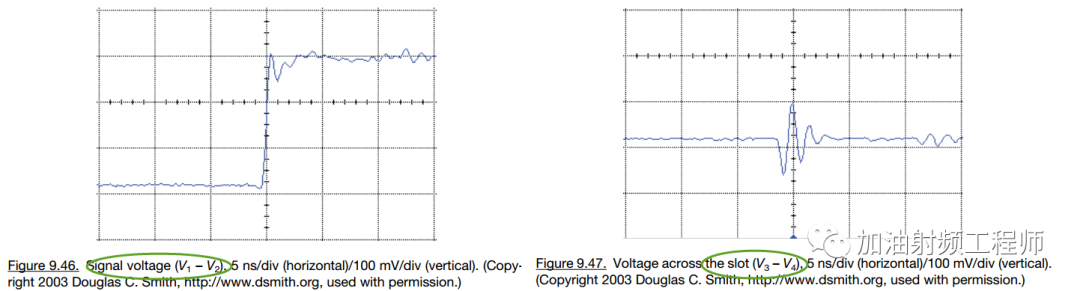

47ohm 负载电阻器(节点 1 和 2)两端的波形下图左侧所示,而节点 3 和 4 处参考平面断路的电压如下图右侧 所示。右图中的峰值电压,幅度几乎为 100 mV,表示信号的回流流过缝隙周围路径时,会有比较大的阻抗。

一般情况下,当导线之间的距离超过10h时,互相之间就不会有什么影响了。

但是由于这个缝隙的存在,即使两根导线距离1厘米,也会导致严重的串扰。上图中3,4结点处的电压会被耦合到其他导线中去。

因为,在这种情况下,两个导体必须在参考平面中的缝隙边缘周围共享一个公共返回路径(即公共阻抗)。

会引起信号上升时间的变化

即使参考平面中的间隙相对较小且上升时间约为 300 ps,导体上的信号穿过参考平面中的间隙也可能会经历显著的转换(上升/下降)时间失真(构成信号完整性问题)。

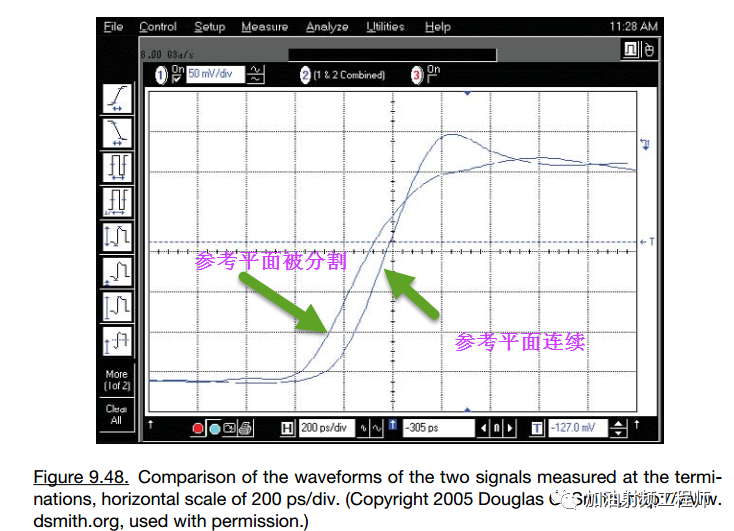

上升时间约为 300 ps 的测试信号从信号发生器通过 BNC 耦合器直接施加到测试板上的两条导线中,其中一条路径在连续平面上布线,而第二条路径穿过平面上的5厘米间隙。

上图中,描述了在终端测量的两个信号的上升沿。参考平面连续的信号表现出明显更快的边沿速率和轻微的过冲,而通过平面间隙的速率较慢,过冲被滤除。

过间隙的信号的边沿速率较慢的原因是,其参考平面中的回流路径被迫绕过间隙的边缘。此外,跨越间隙时回流路径中的阻抗不连续性导致信号的较高频率分量的反射。

从信号完整性和功能的角度来看,这种失真是无法容忍的。

参考平面的分割会产生辐射

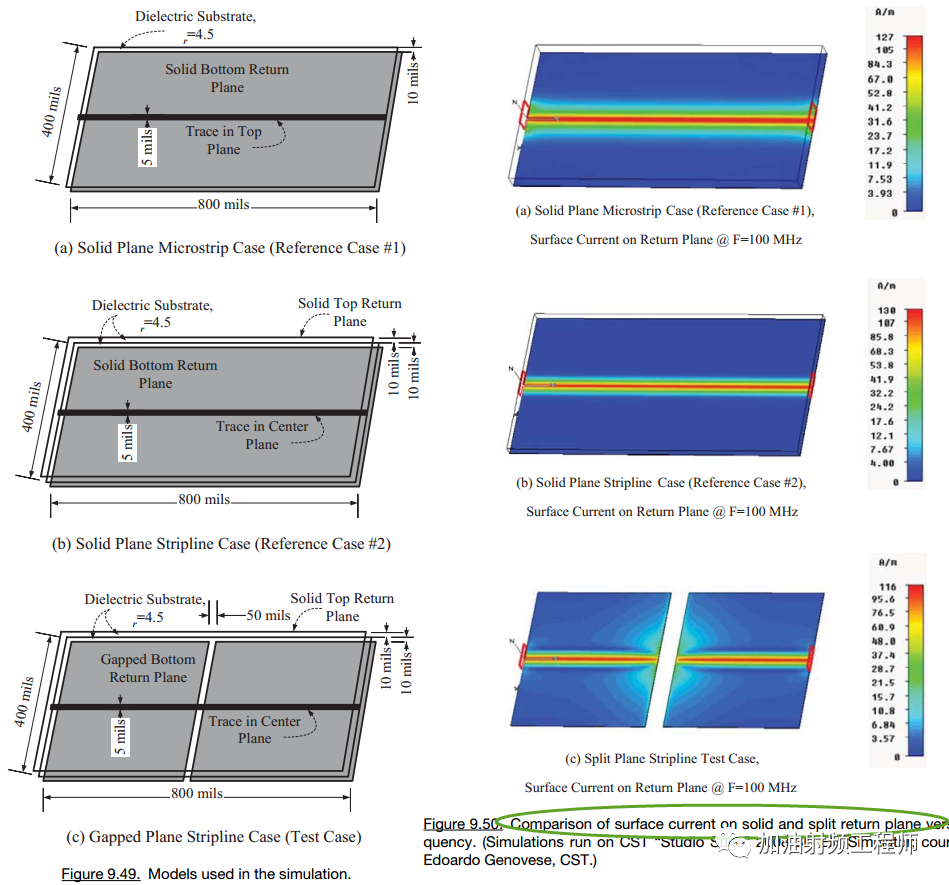

用三维仿真软件,对以下三种情况进行仿真。

case1: 微带线,参考平面为实平面,PCB大小为400X800X10mil,线宽为5mil。

case2: 带状线,两个参考平面都是实平面,PCB大小为400X800mil,上下介质厚度均为10mil,线宽为5mil。

case3: 带状线,一个参考平面为实平面,另一个平面有缝隙,PCB大小为400X800mil,上下介质厚度均为10mil,线宽为5mil,但是在下面的参考平面上有一个50mil宽的缝隙。

板子的介电常数,均为4.5.

具体结构如下图所示,右侧是参考平面上的回流分布。发现作为带状线,虽然上下两面都有参考平面,但是如果其中一个参考平面上有缝隙,也会对带状线的性能产生影响。

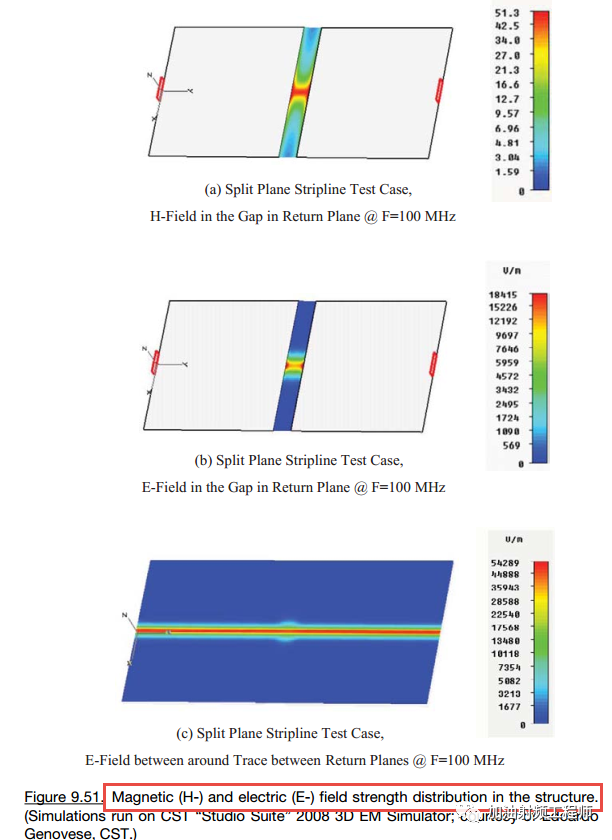

下图中表明,在间隙处电流不连续,H 和 E 场分布发生显著增强。这表明波传播确实发生在间隙中。

参考文献:grounds for grounding,9.4.1