以消费电子领域为例,从DDR2(LPDDR2)演进到DDR5(LPDDR5)的过程中,最大数据速率提升了8倍,IO电压降低了40%。对于电子系统设计而言,这极大降低了电子系统尤其是DDR接口的时序裕量和噪声容限,使得设计验证的难度大幅度增加。而为了满足高速率和低功耗的要求,设计中必然会面临设计裕量,信号完整性和时序电气规则的挑战。

1

设计裕量的挑战

2

信号完整性的挑战

3

电气规则的挑战

为了应对这种挑战,当前DDR内存通过优化内部拓扑结构和内部引入诸多校准机制(DDR内存/内存控制器协同工作)的方式,来降低DDR接口设计的复杂度,例如:

DDR内存模组内部采用Fly-By拓扑结构,以减少Stub的数量和长度,从而降低信号干扰

采用Write/Read Leveling, Preamble training, DQ VREF training等来矫正DQS,DQ,CK,ACC的延迟差异和参考电压范围等电气性能

采用ZQ校准和多种片内终结(ODT)模式提供终端阻抗,来减少数据线、选通线和地址线的信号反射

采用数据总线翻转(DBI)来减少信号翻转率,以便降低信号干扰

增加CRC冗余来提高信号传输可靠性等

同时,JEDEC和芯片厂商也会提供信号参考范围和布线规则,协助PCB设计师进行DDR接口设计。

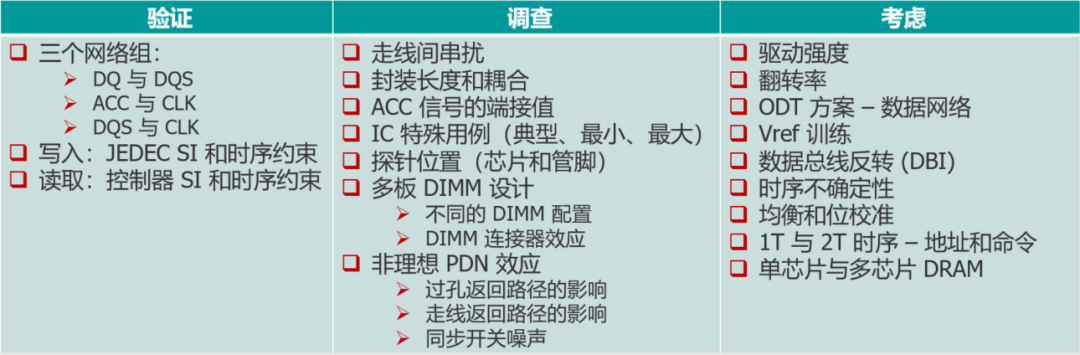

然而,现实中对于可靠的PCB设计来说,这并不能完全解决DDR接口设计问题。尤其是仅依靠器件内部的优化校准和芯片厂商的布线规则是不够的,设计师还需要根据JEDEC信号参考范围,考虑所有的PCB电气效应和寄生效应,通过工具仿真验证或者设备测量,来确保PCB的DDR接口设计具备大量的时序裕度、信号完整性和DDR电气性能。DDR4接口仿真的设计主要因素包含了下图表内所示各注意事项,以及对Vref需验证电压范围,对于控制器和DDR时序的不确定性在读写两端需验证眼图。

此图版权归Mentor所有

由于PCB设计中DDR接口的仿真、建模的复杂性,PCB的DDR接口设计越来越被广大设计师重视。为提高设计验证效率和质量,Mentor出品的HyperLynx DDRx 向导为PCB设计师带来了可全方位覆盖完整的DDR接口仿真、建模和验证方案,以导航向导的方式,引导用户完成接口仿真配置,实现一次配置,全接口仿真验证,并将结果以HTML报告的形式呈现给用户,方便阅读,查找和分享。针对PCB中的DDR接口的设计,HyperLynx提供布线后仿真验证机制,检查以上各个DDR接口验证要素。同时,Mentor还提供了基于HyperLynx DRC平台的设计规则检查工具,保证DDR布线能够符合设计规范要求。对于DDR4/DDR5设计中日益严重的电源完整性的问题对于信号质量的影响,Mentor也提供了完整的电源完整分析工具和PowerAware仿真解决方案。

关于确保 DDR4 电气性能符合预期的数据速率的具体演示,欢迎扫码观看Mentor于5月28日20:00举办的线上研讨会