用于先进封装的UCIe,如硅衬垫、硅桥或再分配层(RDL)扇出

用于标准封装的UCIe,如有机衬底或层压板

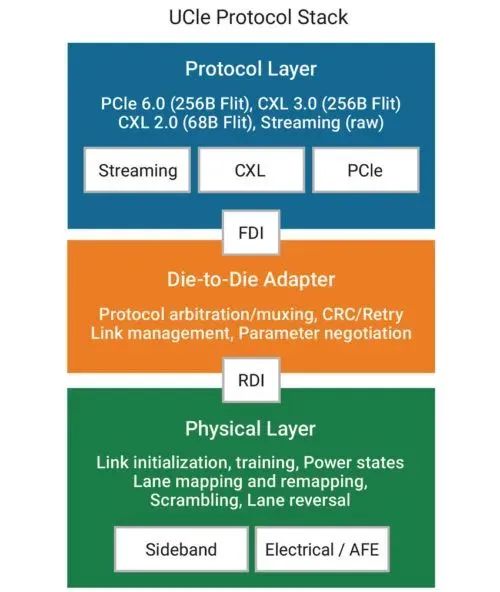

最上端的协议层通过基于流量控制单元(FLIT)的协议实现,确保最大效率和降低延迟,支持最流行的协议,包括PCI Express®(PCIe®)、Compute Express Link(CXL)和/或用户定义的流协议。

第二层用于对协议进行仲裁与协商,以及通过裸片间适配器进行连接管理。基于循环冗余检查(CRC)和重试机制,该层还包括可选的错误纠正功能。

第三层为物理层(PHY),规定了与封装介质的电气接口,是电气模拟前端(AFE)、发射器和接收器以及边带通道允许两个裸片之间进行参数交换与协商的层级。逻辑PHY实现了连接初始化、训练和校准算法,以及测试和修复功能。

PHY──支持标准和高级封装选项,可采用先进的FinFET工艺,获得高带宽、低功耗和低延迟的裸片间连接。