来源:无锡亚科鸿禹电子有限公司

作者:市场总监 白建东

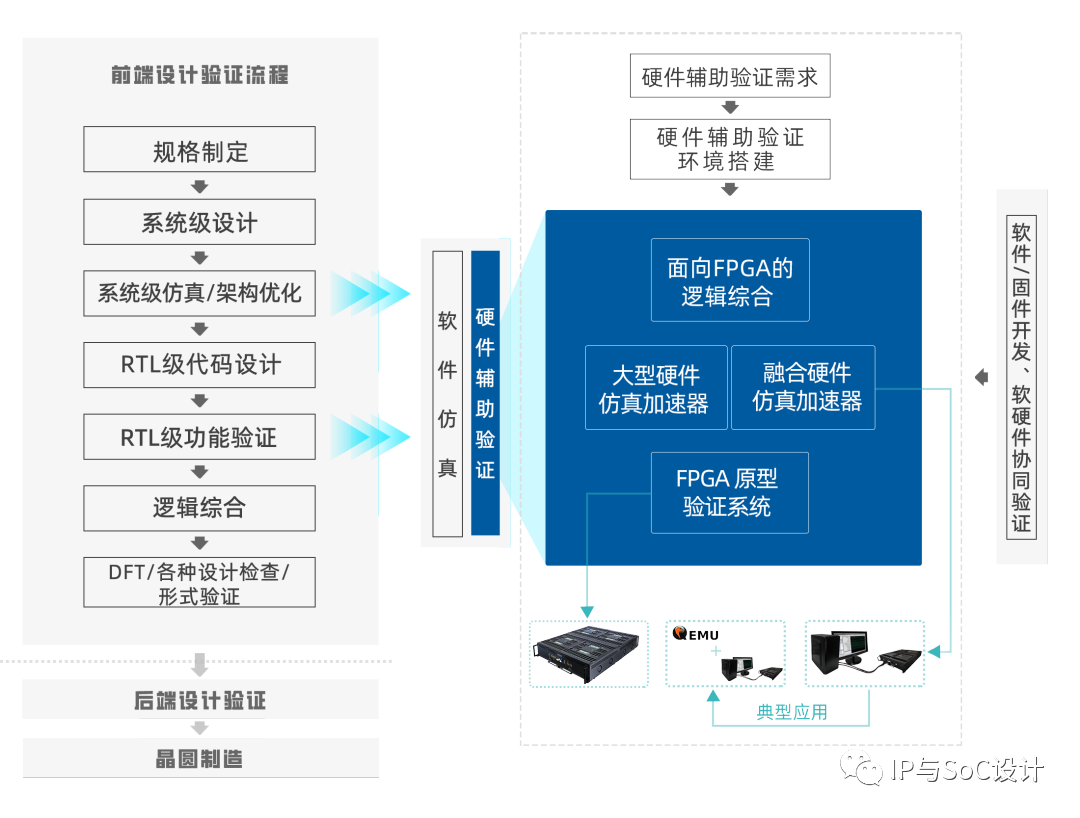

近年来,芯片规模,功能复杂度以及集成度的不断增加,验证工作面临着非常大的挑战。软件仿真(Simulation),FPGA原型验证(FPGA Based Prototyping)和硬件仿真加速(Emulation)这三种有效的功能验证的方法,在验证流程中发挥着非常重要的作用。软件仿真有着出色的信号可见性,FPGA原型验证有着极强的实时性和系统开发性,硬件仿真加速则兼具了信号可见性,可调试性,以及仿真加速的能力,这几种验证方法在芯片前端设计的功能性验证阶段发挥着重要的作用。FPGA原型验证和硬件仿真加速作为硬件辅助验证的两种手段,在芯片设计的过程中相辅相成,互为补充,为芯片成功流片保驾护航。硬件仿真加速阶段,一般用于代码还不很成熟的开发的中后期阶段,需要能够提供更大的系统容量,更方便的调试手段和方法,主要用来验证设计的RTL代码,兼顾软硬件协同验证和软件开发。而FPGA原型验证阶段一般应用于代码比较成熟的的偏后阶段,主要是做软件开发和软硬件协同验证。

图一 硬件辅助验证在流程中的位置

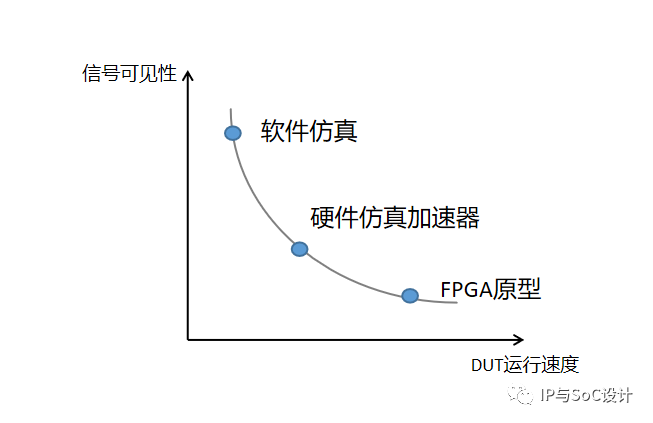

几种不同的仿真验证手段的效果对比

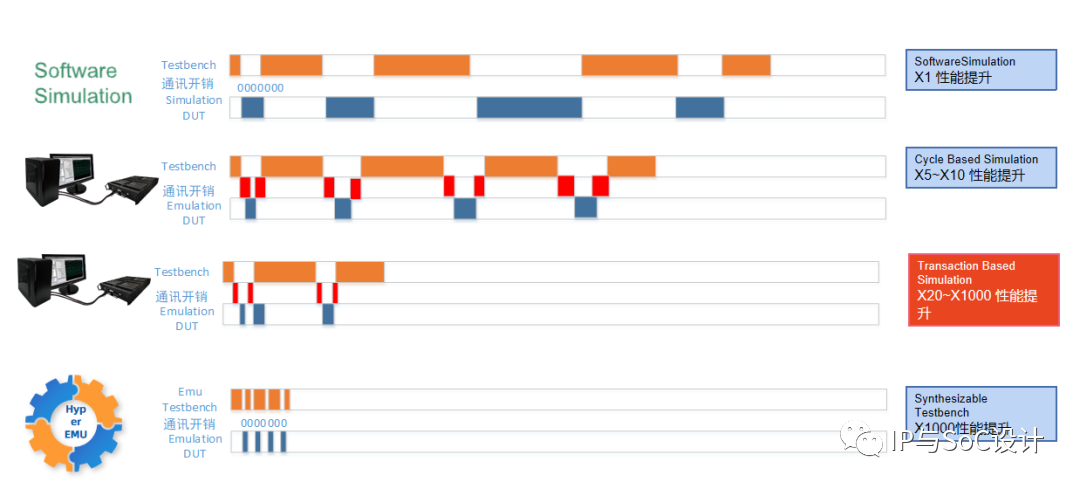

一般意义上,我们将FPGA原型验证和硬件仿真加速都归为硬件辅助验证手段,比较有效和最为常见的仿真加速方式分为:软件仿真(Software Simulation),周期精确级的仿真加速(Cycle Based Simulation ),事务级的仿真加速(Transaction Based Simulation),和完全可综合的仿真加速(Synthesizable Simulation)这几种方法。通过不同的仿真加速方法,对验证速度能够有接近千倍的提升。

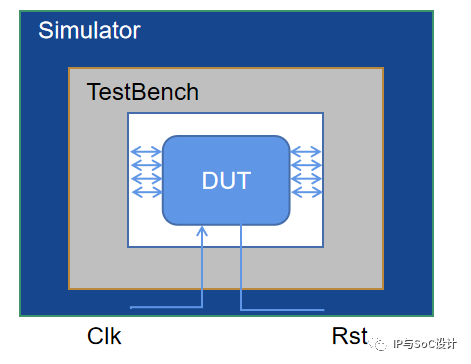

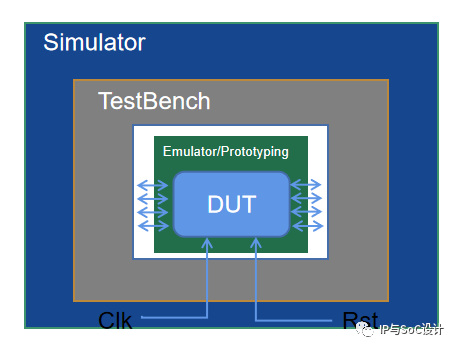

第一种,软件仿真(Software Simulation),最常见的仿真方法,将Testbench和DUT都在仿真软件中运行。最主流的仿真软件的算法机制大部分都是“基于事件的算法”这种算法更适合处理离散的时间,状态和变量。仿真器首先在编译数据结构的时候会建立一个事件队列,仿真从时间0开始,在时间0的所有事件队列处理完毕以后,才可以进入下一个时间周期。而在同一个时间周期内的事件在“硬件”上都是并行的。

图二 Simulator仿真的结构

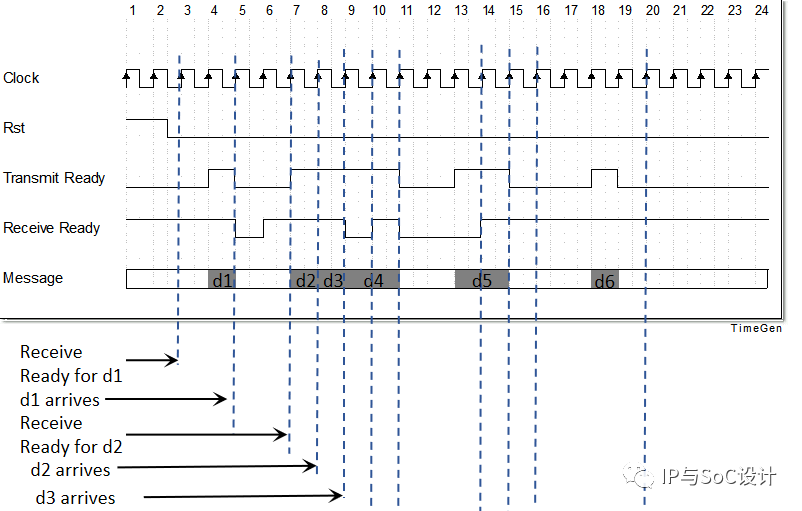

图三 基于事件的Simulator算法

第二种:周期精确级的仿真加速(Cycle Based Simulation Acceleration )

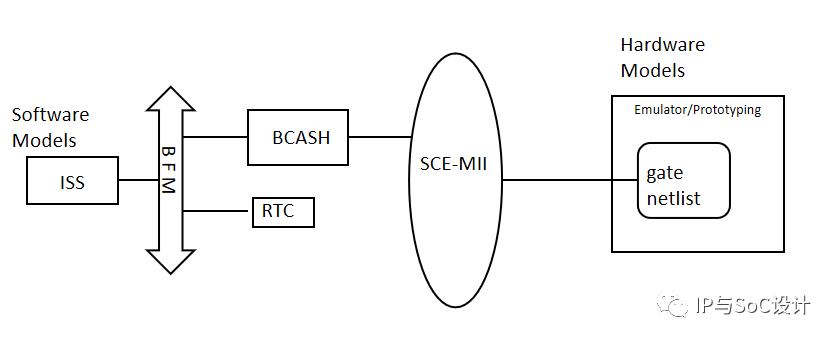

我们在针对软硬件联合仿真的方式做说明之前,需要对SCE-MI/MII(标准协同仿真建模接口)做一下说明,该接口是为了标准化软件模型和硬件平台之间的通讯而定义的,属于Accellera标准,目的是使用者将DUT和Testbench做连接,通过事务器模型(Transactor)能够轻松的实现互联。下图是该协议的基本结构说明。

图四 SCE-MII基本结构

周期精确级的仿真加速,是通过专用的硬件来运行用户设计,通过仿真软件运行Testbench,根据专用的软硬件协同工作的协议来进行软件硬件侧的数据转换和交付,从而实现软件仿真加速的一种方法。该方法在软硬件两侧交互的周期中,严格按照时间单位推进每一步的协议转换,并且采用双握手的方式进行通讯确认,这将产生大量的软硬件之间的交互开销,所以在加速的效果上不是十分的理想。这种方式的优点是针对一些非标协议的转换和时钟同步结构的设计有很大的灵活性。

图五:周期精确级的仿真加速结构

图六:双握手协议示意

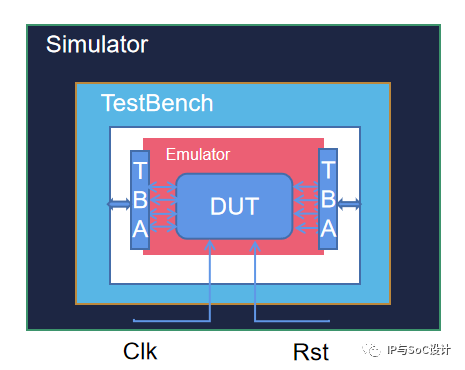

第三种:事务级的仿真加速(Transaction Based Acceleration)

事务级的仿真加速是将DUT和部分Testbench运行在硬件辅助验证工具之中,通过事务器与仿真器中运行的Testbench进行通讯,可以实现将无时序激励变为有时序功能的交互。这是因为软件侧的一个操作所花费的时间在一般情况下会远大于硬件侧的时钟周期。当发送一个带时序的激励时,软件侧需要花更多的时间进行时序的构建,会在一定程度上影响软硬件协同仿真平台的性能。所以在软硬件验证过程中,事务级仿真加速能够很好的解决这类型的问题。比如对于一个拥有AXI或者AHB接口的DUT,软件侧需要按照AXI或者AHB的时序规则构建激励,而扩展了无时序激励变有时序功能时,仅需要将AXI或者AHB的总线数据按顺序发送至硬件侧,硬件侧可以自动完成时序的构建,这样的功能结构能够大幅度提高仿真的效率。

图七:事务级的仿真加速结构

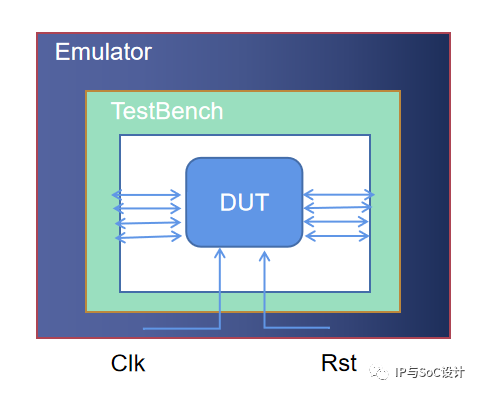

第四种:完全可综合的仿真加速(Synthesizable Testbench Simulation )

图八:完全可综合的仿真加速结构

这种仿真加速方式相较于Transaction的仿真加速,是需要将用户的DUT和测试激励完全综合进仿真加速器,这样可以大大的减少因为软硬件的交互而产生的通讯开销,从而可以极大地提高仿真速度。

不同的软硬件结合的仿真加速方式能够带来不同的加速比,周期精确级的仿真加速因为通讯开销带来的影响,相较于软件仿真基本上可以做到5-100倍的仿真加速;基于事务级的仿真加速则能够为用户带来20-1000倍的加速体验,尤其适用于各种专用的算法实现,比如:视频编解码的处理,交互数据量巨大的通讯芯片验证等。而完全可综合的仿真加速则可以针对全流程的设计验证提供最有效的仿真加速手段。

图九:几种不同的仿真加速的加速比

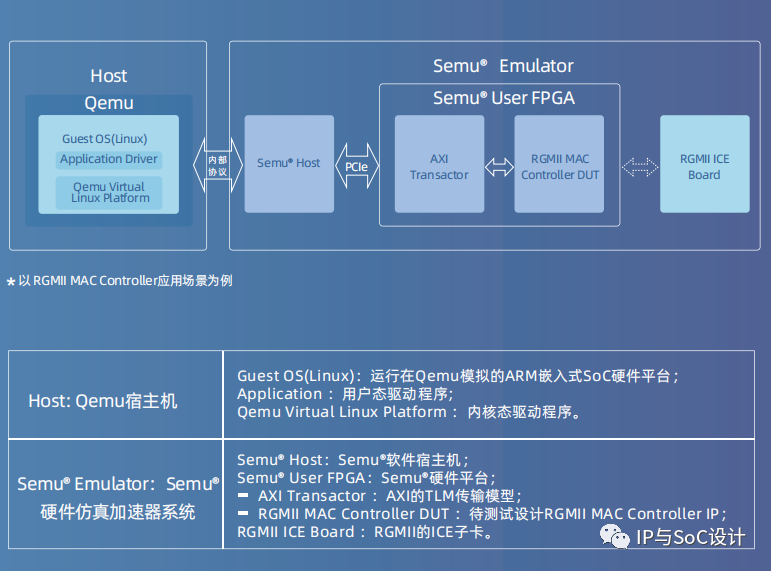

基于硬件辅助验证的混合仿真是指利用硬件仿真加速器和虚拟原型同时运行SoC的不同设计模块,在SoC整体架构硬件实现之前提供嵌入式软件和硬件的协同仿真,从而加速SoC的研发进程。可以实现硅前硬件和嵌入式软件协同混合验证,为系统架构的优化、嵌入式软件以及RTL的早期开发提供准确,即时的仿真验证环境,有力推动产品开发左移。

一般的混合仿真系统由Qemu宿主机和硬件仿真加速系统两部分构成,其中,宿主机的操作系统中会运行基于开源环境的目标嵌入式处理器和基于Qemu Virtual Linux Platform的内核驱动程序以及用户态的驱动程序。通过专有协议实现软件和用户设计的通讯,将运行硬件仿真加速工具的宿主机和硬件平台,通过TLM(Transaction Level Model)的传输模型,将用户设计的IP和实现硬件结构的功能子卡进行联合,从而实现一个完整的混合仿真系统。

图十:混合验证工作流程

设计验证过程综合时间长,迭代频率高,需要设计工程师和验证工程师花费大量的工作时间和精力。近年来,随着多种图像处理器,人工智能加速算法,大数据采集,多处理器应用等应用方向的芯片设计增加,各种GPU,TPU,XPU等大逻辑量的IP被集成至单颗芯片内,造成设计、仿真和验证的数据量出现了指数级的增长,所以综合和仿真等过程都展现出“过长的编译综合时间”、“编译迭代耗时过长”等情况,工程师大量的时间浪费在了等待综合编译上。

流程节点不同,存在不同的综合策略需求。硬件仿真加速阶段,一般用于代码还不很成熟的开发的中后期阶段,需要能够提供更大的系统容量,更方便的调试手段和方法,主要用来验证设计的RTL代码,兼顾软硬件协同验证和软件开发。而原型验证阶段一般应用于代码比较成熟的的偏后阶段,主要是做软件开发和软硬件协同验证。在以上两个流程阶段,综合加速的需求各有侧重点。硬件仿真加速阶段代码的成熟度不高,迭代频繁,需要更高速的编译速度来提高迭代效率,以及对RTL代码的忠实的一致反映以便于调试;而原型验证阶段代码相对成熟,需要产生出更高效的功能等效系统来提高运行速度。

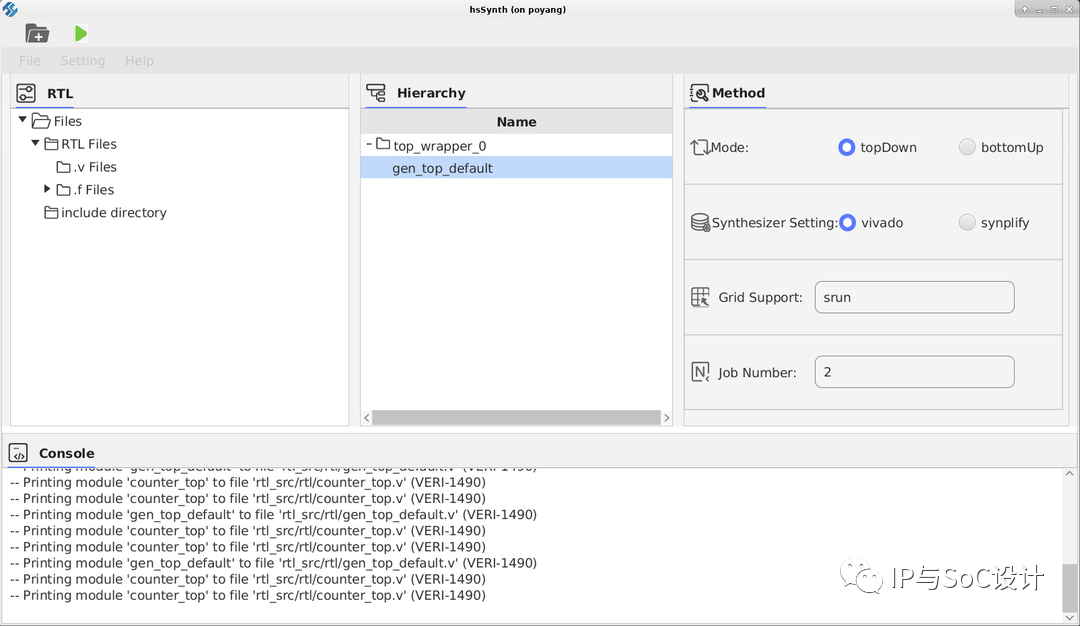

高效并行综合是将用户的RTL代码按照不同模组分类,分别调用综合工具,同时进行综合,从而实现快速综合的目的,按照不同的阶段,可以设置不同的综合流程,可以实现“Top-down”和“Bottom-up”两种方式;支持多种的逻辑综合器,比如:Xilinx Vivado®, Synposys Synplify®和其他的一些开源的逻辑综合器,支持GUI和Batch模式,用户可以灵活选择功能展现模式;可以支持模组并行化处理,既支持本地多线程并行处理,也可以有效的支持多种作业调度系统;可以设置不同的参数来制定不同的综合策略,从而实现综合效率的最大化,比如:面积优先,速度优先,最大化、小化优先等策略。通过并行逻辑综合方案可以提供出色的自动化流程,大大缩短编译所需时间,提高整体的效率和利用率,极大的提高生产率。

图十一:并行综合处理界面

FPGA产品自带的在线逻辑分析仪工具(ILA 或 SignalTap)可以为FPGA提供观测信号的便捷性,但因为其本身的属性问题,存在了诸多的短板,例如:数据波形存储在片上的RAM中,需要均衡用户设计占用的存储资源和用于调试的存储资源;受限于FPGA片上RAM的容量,对待抓取的信号的位宽和深度都有限制;待抓取波形需要从FPGA的RAM资源中通过JTAG导出到工作站中,由于传输速度过慢,当数据量巨大时,传输时间占用更加的明显;芯片逻辑容量增加,原厂的逻辑分析仪无法满足调试需求。

硬件辅助验证工具中的专用逻辑分析仪有效的解决了以上的几个问题。

1)波形数据存储在FPGA外部存储,几乎不占用FPGA的片上ram资源;FPGA器件因为其工艺特殊性,一般会集成一些RAM资源在FPGA种,但是该种资源的深度和位宽都非常的小,无法满足超大容量的存储需求,亞科鸿禹新研发的hsTrace,在系统内部集成有专用的外置存储空间,可以完全不占用FPGA的RAM资源。

2)外接存储容量最高可支持16GB的存储空间,极大地提高了波形数据的采样大小;硬件辅助验证工具外置专用的存储空间,可以使数据存储和读取的资源加大,也就意味着可以提供更深的存储空间和更宽的存储位宽,为解决当下验证功能的需求提供了基础。

3)波形数据的传输通过网口(或PCIE)实现,传输速率也得到了极大的提升。FPGA原厂提供在线逻辑分析仪的调试通道是通过JTAG接口完成的,JTAG的最大传输速度只能到12Mhz,我们选用的PCIE的传输带宽能够到5Gbps,这为大数据量吞吐提供了硬件通道。

4)支持多颗FPGA的硬件辅助验证工具,实现多FPGA的系统级debug。

5)每颗FPGA可以设置4K*10组的采样信号量;通过专用的传输接口和存储器,可以针对单颗FPGA的采样信号进行增加,这意味着可以有更多和更深的信号被采样到,也就是可以完成更多数量的观测,适应当前的复杂协议的应用。

硬件辅助验证工具可以有效加速软件仿真速度,用于验证设计的RTL代码、软硬件协同验证和软件开发。近些年,硬件辅助验证出现了一些明显的发展趋势:

1)企业级和桌面化的硬件仿真加速需求快速增长。当前,以GPU,5G,存算一体为代表的超大型的集成电路设计层出不穷,对系统仿真速度和代码快速签核提出了大量的需求。由于数据计算量大,用户测试场景复杂所以需要能够在超大型的硬件仿真加速工具下进行用户设计和验证环境的部署。企业级的硬件仿真加速器可以为用户提供指数级的逻辑验证容量,高效的纠错能力,信号可见和功耗分析的特征。桌面化的硬件仿真加速器可以为用户提供混合验证环境,能够为各类型的CPU用户,提供更早期的环境验证。企业级硬件仿真加速器侧重在多用户,多区域访问的特性,桌面化能够提供更加便利的调试手段,所以两种不同的应用方向各自发展。

2)硬件仿真加速器的专用化越来越明显。加密算法,WIFI应用等各种测试数据量巨大,而算法相对单一的用户,对仿真需求增大。而传统的仿真加速器并不能非常有效的解决这类用户的问题。所以,针对各类型应用而专用的仿真加速器产品非常适合这种类型的应用。集中固定的硬件扩展卡或者专用的降速桥都可以为某些类型的应用提供完整的加速环境。

3)全流程验证需要在硬件仿真加速工具中完成。早期的硬件仿真加速器出现在代码设计的后端,用于确认代码功能的正确性。现在随着设计的时间需求进坡度增加,越来越多的流程会被集成至硬件仿真加速工具中来实现。早期的功耗分析,系统环境搭建,逻辑调试等功能都逐渐的被集成至硬件仿真加速工具中。

4)仿真和验证环境有统一性的趋势。仿真代码和用户芯片设计代码是分开处理的,涉及到一些无法综合的代码可以分别在仿真和验证场景中实现,但是用户期望的是设计代码和测试代码保持一致。所以硬件仿真加速工具会增加大量的功能属性用于统一仿真代码和设计代码,从而减少因为设计不一致而造成的功能风险。

5)需要支持多种的软件仿真工具。因为硬件仿真加速器的历史原因,各家的工具分别只能支持自己家的软件仿真工具,而对于不同的用户来说,有一些诉求是能够支持不同家的仿真工具的。

6)待验设计的运行频率逐渐升高。硬件仿真加速器的运行频率,因为软硬件交互的原因,会产生大量的通讯开销,会对待验设计的运行速率有很大的影响,绝大多数情况下只能运行在几百K-几兆Hz,随着各种专用算法的出现,验证的实时性也相当的重要。所以对于硬件仿真加速器来说,能够提供比较实时的运行频率,是非常关键的。

本文内容仅代表作者观点,不代表平台观点。

如有任何异议,欢迎联系我们。

如有侵权,请联系删除。