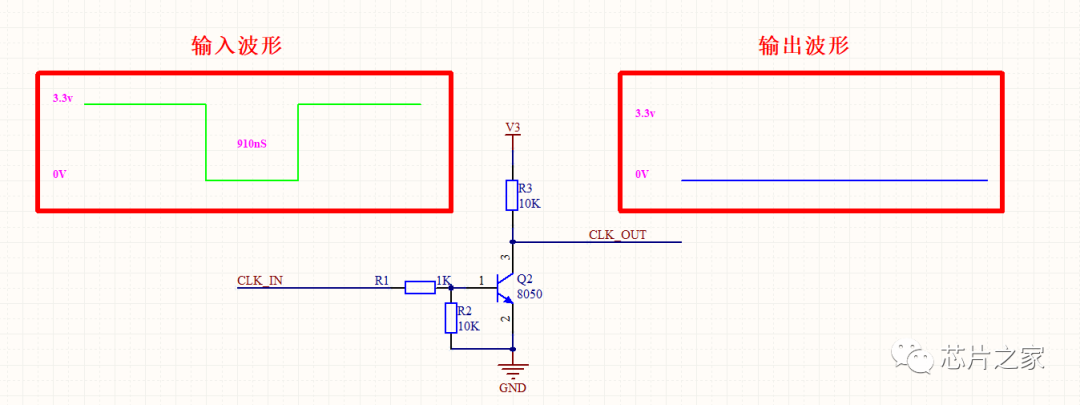

看论坛上有位网友发了一个很有意思的电路,大概意思是自己搭了一个很基本,非常简单三极管驱动电路,本意是想将信号反向一下,但是输出并不像预期的那样,输出波形纹丝不动,并没有进行反向输出,查了之后看三极管导通频率为100MHz,但是现在的脉冲才1M左右,非常郁闷,请求指导。

有人觉得三极管是假的,有人建议降低R3的阻值,还有人觉得8050的开关速度不够,很多猜想。其中有位网友建议,R1上面并联一个100nF的电容试试,楼主并联之后,果不其然,问题得到解决,如下图所示:由于电荷存储效应,晶体管BE之间有一接电容,与Rb构成RC电路,时间常数较大影响了晶体管的导通和截至速度(即开关速度)。- 控制脉冲低电平时,电路达到稳态时,晶体管截至,电容两端电压为零。

- 控制脉冲高电平到来时,由于电容电压不能突变,电容需继续保持零,这样,左边输入突变为高电平,晶体管基极B电压突变到高电平,使晶体管迅速导通;电容被充电到脉冲电平电压;进入到稳态,电容电压为脉冲电平电压。

- 此后,当控制脉冲低电平到来时,由于电容电压不能突变,需继续保持脉冲电平电压,因此,基极电压从零(实际为be压降)跳变到负的脉冲电平电压,使得晶体管迅速从饱和状态转到截至状态;此后,电容通过R放电,达到稳态时,两端电压为零。

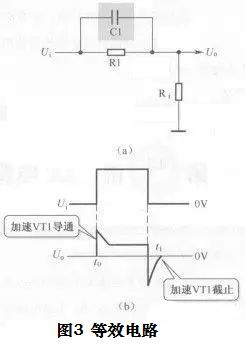

电路中,电容并联在R1上,称之为加速电容,目的是加快三极管导通和截至的转换速度。加速导通过程:当输入信号电压Ui从0V跳变到高电平时,由于电容Cl两端的电压不能突变,加到VT1基极的电压为一个尖顶脉冲,其电压幅值最大,如下图3所示,这一尖顶脉冲加到VT1基极,使VT1基极电流迅速从OA增大到很大,这样VT1迅速从截止状态进入饱和状态,加速了VT1的饱和导通,即缩短了VT1饱和导通时间(三极管从截止进入饱和所需要的时间)。

维持导通过程:在t0之后,对Cl的充电很快结束,这时输入信号电压Ui加到VT1基极的电压比较小,维持VT1的饱和导通状态。加速截止过程:当输入信号电压U从高电平突然跳变到0V时,如图3(b)所示的tl时刻,由于Cl上原先充到的电压极性为左正右负,加到VT1基极的电压为负尖顶脉冲。由于加到VT1基极的电压为负,加快了VT1从基区抽出电荷的过程,VT1以更快的速度从饱和转换到截止状态,即缩短了VT1向截止转换的时间。干货 | 警惕:别让这些设计中的小细节毁了整个PCB设计添加微信回复“进群”

拉你进技术交流群!

国产芯|汽车电子|物联网|新能源|电源|工业|嵌入式…..

在公众号内回复您想搜索的任意内容,如问题关键字、技术名词、bug代码等,就能轻松获得与之相关的专业技术内容反馈。快去试试吧!

如果您想经常看到我们的文章,可以进入我们的主页,点击屏幕右上角“三个小点”,点击“设为星标”。