近些年随着人工智能技术的发展,深度神经网络算法逐步在星载、机载等遥感数据处理中得到广泛应用,在灾害预警及应急、海洋应用、环境监测、国土资源等方面起到越来越重要的作用,如图 1 所示。但卫星、无人机等需要对遥感 图像进行实时处理的应用场景,都对实现平台具有严格的体积、重量、功耗的限制。而深度神经网络又具有运算复杂度高、存储带宽需求大的特点。在高时效性要求与资源功耗等空间环境的强约束下,通用处理平台难以支撑在轨人工智能 应用的计算需求。这都使得人工智能技术在上述领域应用面临着巨大的挑战。因此亟需开展支持星载、机载人工智能应用的核心硬件与基础软件技术研究。

为了解决上述问题,我们提出了基于 FPGA 的深度卷积神经网络的核心硬件系统架构,并基于此架构搭建了遥感图像智能处理系统。该系统具有高性能、低功耗、延时低等特点,可以为空间人工智能应用提供支撑。

本作品在 FPGA 上实现了改进后的 YOLOv2 目标检测网络,能够完成对遥感场景下飞机、汽车、港口等多尺度、多类型目标的高精度快速检测及分类,在海洋、水旱等监测与应急救灾等多领域中都可以发挥重要作用。此外,本作品相比于与 CPU、GPU 通用处理平台功耗更低,并且具有同等功率下运行效率高(能效比高)等优势。在星载、机载等资源受限的条件下,作品可以满足深度神经网络的庞大的计算量与存储需求,为遥感图像的在线处理提供了可能。同时,本作品为我们后续研制相关 ASIC 芯片提供了前端验证。卫星所获取到的遥感图像可以通过该芯片完成在轨实时处理,仅将有效信息下发地面站,从而减少星地链路的传输压力。

本设计提出了一种用于光学遥感目标智能检测识别的 FPGA 实现方法。

首先,我们选取 YOLOv2 作为基础网络,对该网络的结构进行了优化。改进后的网络在多尺度、多类型目标的遥感图像处理任务中表现出更优的性能。并引入了基于对称量化的混合精度运算,降低了网络中的浮点运算规模,使该网络更 适合部署在 FPGA 硬件平台上。

其次,我们提出了一种卷积神经网络处理引擎,该引擎可以实现卷积神经网络中常见的操作,例如卷积、激活、池化等。该引擎还可以实现网络中所涉及到 的多种卷积类型。在此基础上,我们充分挖掘神经网络中卷积运算的并行运算潜力,搭建运算流水线结构,提高了处理性能。此外,我们还提出了一种有效的数据存储和访问策略,该策略可实现低延迟计算和高存储带宽利用率。

最后,我们成功在 Xilinx VC709 上部署了改进的 YOLOv2 网络。与传统实 现平台相比,该作品在保证检测精度的同时,极大地降低了功耗和运算复杂度, 更加适合部署在低功耗应用场景。

(1) 面向 FPGA 对算法进行优化。采用混合精度神经网络处理方法,利用低位宽的整数运算对部分浮点运算进行近似,从而优化硬件结构,降低逻辑资源与存储资源开销。

(2) 构建通用可配置的向量处理引擎。由于改进的 YOLOv2 网络引入了空洞卷积、转置卷积等多种类型的卷积运算,增大了部署在 FPGA 上的难度。因此我 们凝练多种卷积运算类型的共同处理特点,提出了一种可配置的向量处理引擎。该引擎可以在 FPGA 上实现多类型卷积运算,节省了资源,且极大提高了设计的灵活性。

(3) 构建适用于神经网络的并行处理策略。本设计挖掘神经网络中卷积运算的并行运算潜力,合理利用 FPGA 上的运算资源,搭建运算流水线结构,实现卷积神经网络前向推断的高效处理。提高了处理性能。

(4) 搭建了基于 FPGA 的低功耗遥感图像处理系统。与传统的卷积神经网络的实现平台 GPU 相比,该作品的功耗要低一个数量级。同时,在 DOTA 遥感数据集上的测试表明,本作品的检测性能与 GPU 一致。因此本作品在功耗和处理速度之间取得折衷,在功耗受限的特定应用场景中部署更具优势。

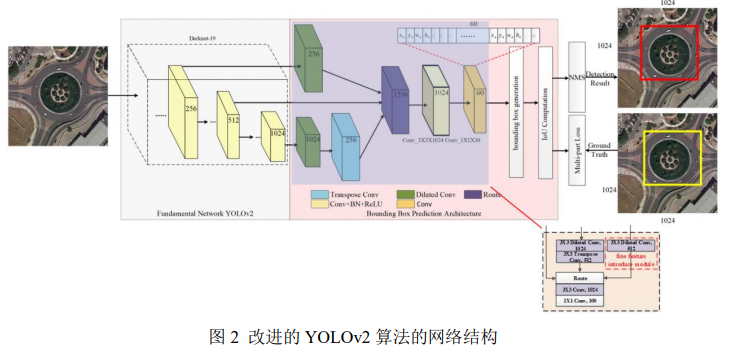

近年来,多种基于卷积神经网络的方法被提出,例如 R-CNN、SSD和 YOLO 等,都被广泛用于深度学习领域的目标检测。与其他方法相比,YOLO 确保了准确性和速度之间的极佳折衷。在本作品中,我们选用了一种改进的 YOLOv2 网络用于遥感物体检测。该网络采用了扩展卷积和转置卷积,从而提高了复杂光学遥感场景中 多尺度物体的性能。该网络在模型复杂度和对象检测性能之间进行了权衡。其网络 结构如图 2 所示,其中,基础工作包含多个计算层,它们相互连接在一起。主要层 是卷积层,池化层,批量归一化层和激活函数。

目前,多数的卷积神经网络训练后的网络模型为浮点类型。若采用该方式进行前向推断,所有运算操作均为浮点类型,会给 FPGA 实现带来巨大的存储和计算压力。

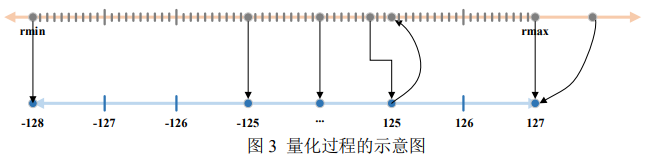

针对上述问题,我们采用了基于量化算法的深度神经网络混合精度计算方法, 利用低位宽的数据类型进行数据表达与计算,从而有效优化硬件结构设计。量化算法可看作对卷积神经网络模型进行近似线性变换,在不改变卷积神经网络的运算类型与运算结构的前提下,将全浮点的网络参数全部转化为适合 FPGA 实现的整数型, 以此降低硬件加速器的复杂度;同时保持一定的浮点精度计算,支撑遥感图像智能处理的海量计算需求。量化过程的示意图如图 3 所示。但是上述方法在训练阶段难以直接实现,这是由于整型表达导致了网络不可导。此外,混合精度计算带来一定的误差,影响网络处理性能。针对上述问题,我们采用了模拟硬件处理的量化神经网络训练方法,有效保证低位宽数据表达网络的正常训练,采用为了有效抑制量化推断带来的误差。在前向推断阶段,应用上述方法设计混合精度处理引擎,相比于浮点计算引擎,能够大幅降低计算引擎所需资源。在有限的逻辑资源条件下,所能集成的引擎集成度大幅调高,系统处理能力及效率也随之提高。

1、卷积层

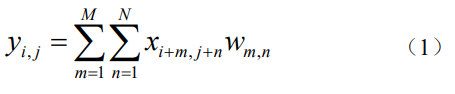

卷积层是卷积神经网络的核心处理,一个二维卷积的操作如图 4 所示。一个 卷积层的内部包含多个卷积核,每个卷积核的所有元素都对应一个参数,每个卷 积核对应一个偏置。我们用 y 来表示图像卷积后的输出,用 i 和 j 来表示输出图 像的行和列,用 x 表示输入图像,用 w 表示卷积核的参数,用m和n来表示卷 积核的行和列,M 和 N 表示卷积核的长和宽,则卷积的过程遵循公式 1:

卷积示意图如图 4 所示:

卷积运算是一种具有多层次循环的乘累加运算。在神经网络中卷积运算涉及的数据量很大,FPGA 的运算单元有限,往往不能并行处理全部的输入数据;同时 FPGA 片上存储资源也是有限的,卷积运算的大量原始图像、参数与中间结果也不能完全存在片上,因此需要将运算数据分块处理。数据切分往往涉及多个维 度,并且当原始数据被分块时,处理时会产生多个中间结果,中间结果可通过叠加得到最终结果。

2、批次规范化层

目前多数卷积神经网络会在卷积层后插入批次规范化层,其的定义如公式 2 所示:

其中,μ 和 σ 表示输入特征图的均值和标准差估计值。γ 和 β 是批归一化层的学习参数。从公式上看批次规范化层可分为两部分,第一部分是输入的规范化;第二部分是在此基础上进行线性变换。从运算类型上来看,批次规范化层属于像素级乘加运算。

3、激活函数

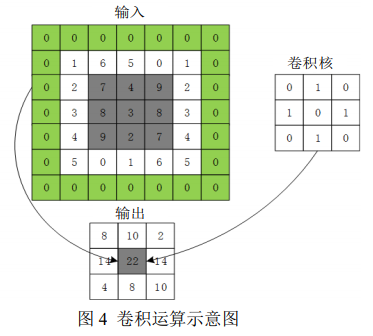

卷积神经网络中每个神经元节点都是接收上一层网络的输出值作为本层网络的输入值,并将本层网络的操作结果传递给下一层。在多层的卷积神经网络之中,上一层的输出值与下一层的输入值之间会插入激活函数,如图 5 所示。

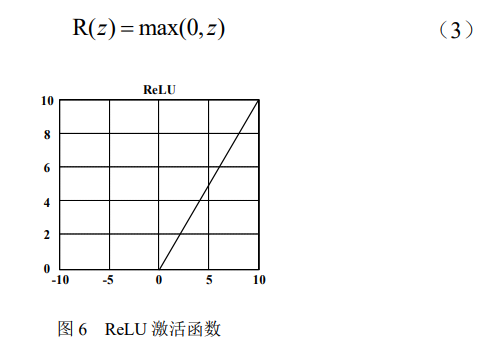

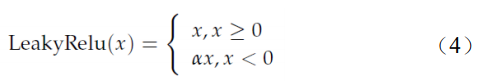

常用的激活函数 ReLU 函数如公式 3 所示,图 6 为 ReLU 激活函数示意图。

ReLU 函数的本质是与 0 做比较,大于 0 的数字保持不变,小于零的数值激活为 0,计算过程简单易于实现。但是 ReLU 函数也存在一定的问题,对于负数 输入可能会导致梯度弥散,因此也有网络采用 LeakyReLU 作为激活或函数。LeakyReLU 是原始 ReLU 的一个变体,如公式 4 所示:

4、池化层

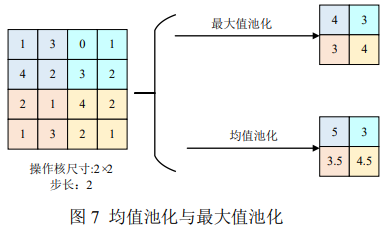

池化操作分为最大值池化与均值池化。在卷积神经网络中,卷积层后面往往跟着一个池化层。在卷积层提取完特征之后,会有一个池化层来对输入特征图像的信息进行过滤,并且进行特征选择。

池化计算层的使用是模仿人类大脑提取信息时的降维和抽象的过程。它主要有三个作用:

1)池化采样使网络模型降低了对特征位置的敏感程度,容许特征学习过程中一些特征位置细微改变的存在,让网络在处理图像扭曲方面的能力得到增强;

2)池化层又称降采样层,它降低了特征映射图的维度,同时减小了下一层 计算输入的数据规模,进而减小计算量和参数个数,这对于硬件实现是非常有利的;

3)池化层在一定程度上能够降低数据过拟合的风险。池化操作主要是将单个点的结果替换为某个区域的特征统计量。均值池化在相邻的 2×2 的区域内,将四个数求和再求平均值,得到输出结果,用四个像素点 的平均值来代替这一区域的像素值;最大值池在相邻 2×2 区域内的最大值来代替这一区域的像素值,如图 7 所示。

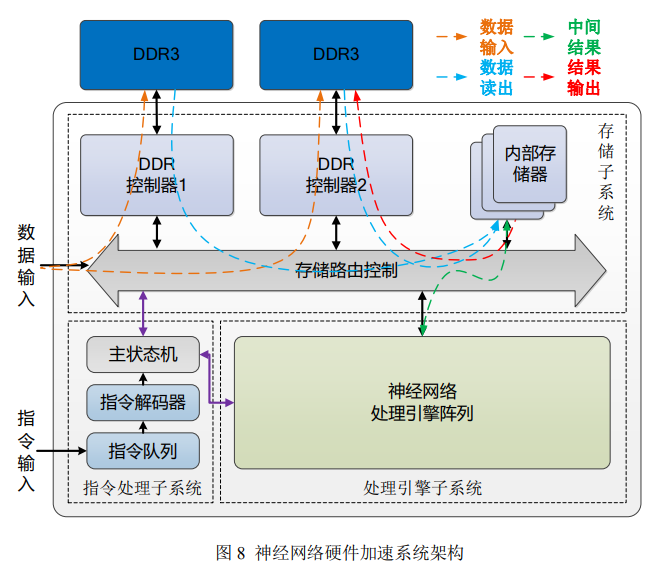

神经网络算法处理过程均具备可并行度高、可复用度高、处理数据量大、处理流程复杂的特点,可归类为数据流驱动的运算密集型处理过程。为了满足以上处理特点,需要设计大规模的处理阵列进行并行处理,为满足这一条件本方案采用 Xilinx VC709 板卡作为实现平台。Xilinx VC709 板卡上核心 FPGA 为 XC7V690T,配备独立双通道 DDR3(512bit@200MHz)。基于该平台,本方案设计了神经网络硬件加速系统架构,如图 8 所示。

我们所提出的神经网络硬件加速系统架构主要包括 3 个子系统:

1、处理引擎子系统

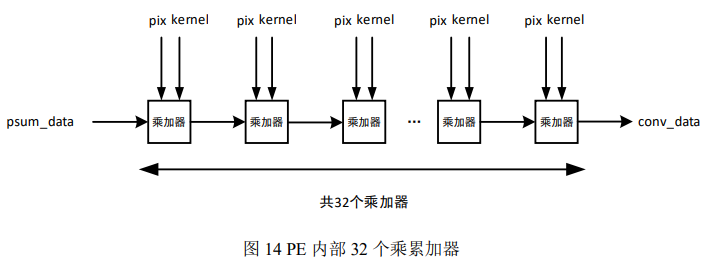

该子系统负责神经网络具体算法的实施,主要完成计算处理的任务。神经网 络处理引擎阵列由 32 个处理引擎组成,每个处理引擎由 32 个乘累加器构成,进行高并行向量乘加运算。

除引擎阵列外,该子系统配有相应的输入与输出控制,输入控制负责从输入存储子系统获取原始数据;输出控制负责实现中间结果与最终结果的存储路由。处理引擎子系统的所有控制需要与主状态机进行交互。

2、存储子系统

存储子系统实现对内外部的存储模块进行管理,可分为存储器单元以及存储路由控制。

存储器单元:用于实现数据缓冲,分为外部存储器和内部存储器。外部存储器采用 2 片容量大、顺序访问速度快的 DDR 芯片,用于保存原始数据与模型参数,数据缓冲周期长的数据保存在其中,内部存储器采用访问速度快、位宽大、 功耗低、容量小、可随机访问的 BRAM,用于缓存部分数据及数据运算中间结果,数据缓冲周期短的数据保存在其中。为保证不同图像处理引擎访问存储器单元时不发生数据堵塞,将存储空间划分成不同容量的独立子存储单元。内部缓存包括:输入特征图缓冲区、参数缓冲区、输出特征图缓冲区以及中间结果缓冲区。

存储路由控制:每个子存储单元通过输入/输出接口与存储仲裁单元相连,处理引擎也通过数据访问接口与存储仲裁单元相连,可实现多通道引擎和存储器之间的访问映射。内部存储器与处理引擎阵列子系统间的内存访问映射由主状态进行配置。

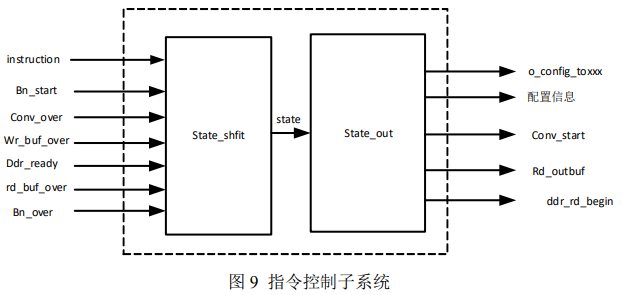

3、指令处理子系统

指令处理子系统又指令队列、指令解码器、主状态机构成。指令队列从外部接收指令需要处理的指令并储存,所有指令顺序排列,先入先出。指令解码器负责从指令队列中取出指令,进行指令解析并传输给主状态机。主状态机将存储访问指令传输至存储子系统,用于配置该条指令的数据读/写通路;将处理指令传输至处理引擎子系统,用于选择处理算法引擎与配置引擎参数。主状态在算法处理过程中与存储子系统和处理引擎子系统均进行交互,以实现流程控制。当指令队列中所有指令全部处理完成后,从外部继续接受下一批处理指令,直至指令全部处理完成。

接收解析后的指令,对各个模块进行配置。主状态机将存储访问指令传输至存储子系统,用于配置该条指令的数据读/写通路;将处理指令传输至处理引擎子系统,用于选择处理算法引擎与配置引擎参数。主状态在算法处理过程中与存储子系统和处理引擎子系统均进行交互,以实现流程控制。

如图 9 所示,主状态机由状态切换模块和状态输出模块组成。用于配置信息和模块间的握手。

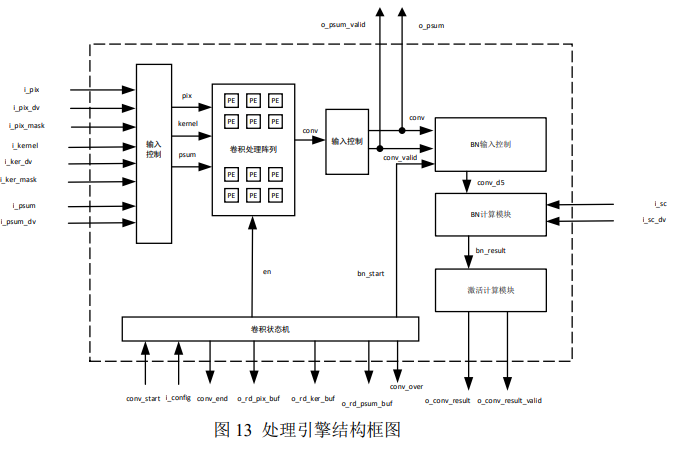

该模块包含三个功能,分别是卷积运算、批量标准化(BN)融合层运算、激活 融合层运算。本设计方案中的运算模块最多可对 32 个输入通道的数据进行乘累 加运算,并将 32 个输出通道的结果并行输出。

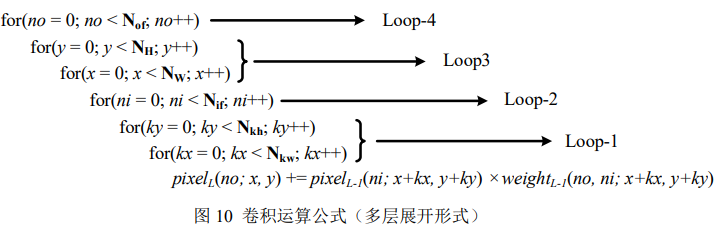

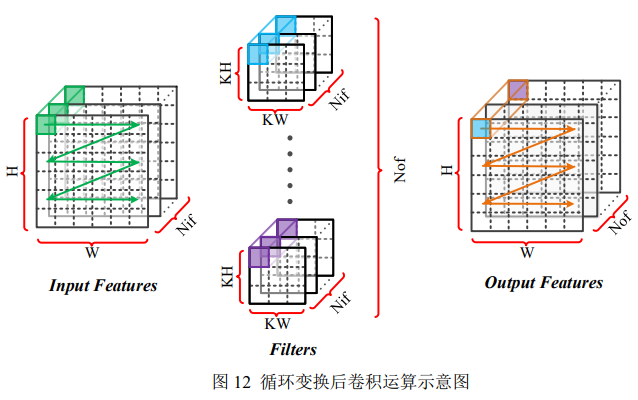

为了令我们的处理引擎子系统可以适用于多种卷积类型在 FPGA 上的实现, 我们对卷积运算进行了分析和改进。以常规卷积层为例,以单张图计算 (BatchSize=1),其输入特张图张量为三维张量 Tensor(Nif, NH, NW),权重参数 为四维度张量 Tensor(Nof, Nif, Nkh, Nkw),输出特征图为三维张量 Tensor(Nof, NH, NW)。其中 Nif、NH、NW为分别表示输入特征图张量的输入通道数、高、宽;Nkh、 Nkw为卷积核的高、宽;Nof为输出特征图张量的输出通道数其计算公式

卷积运算可看为两部分,上三层循环为输出结果索引不参与叠加过程,下三 层循环为卷积计算核心部分。下三层循环计算可看作图 12 中绿色立方体与紫色立方体的对应点乘法后再求和。目前已有的工程中我们按照上述循环展开方式进行设计,首先计算二维卷积核内部计算,而后通过循环叠加将所有输入通道进行 组合。但是这种方案在支持多种卷积运算时需要进行数据读取重排序,在硬件实现时数据流控制较难。此外,卷积运算是一种具有多层次循环的乘累加运算。在神经网络中卷积运算涉及的数据量很大,FPGA 的运算单元有限,往往不能并行处理全部的输入数据;同时 FPGA 片上存储资源也是有限的,卷积运算的大量原始图像、参数与中间结果也不能完全存在片上,因此需要将运算数据分块处理。数据切分往往涉及多个维度,并且当原始数据被分块时,处理时会产生多个中间结果,中间结果可通过叠加得到最终结果。

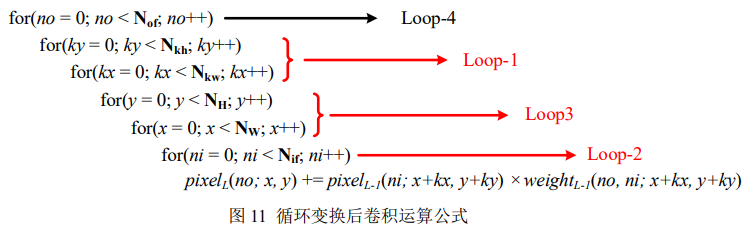

针对上述问题,本方案采用了循环变换。对图 10 中公式进行循环变换,将 Loop{1, 2, 3, 4}的顺序变换为 Loop{2, 3, 1, 4},循环变换后的卷积运算公式如图 11 所示。

从上述公式可以看出,经过循环变换后的卷积计算在运算类型和运算数量上没有任何变化,只改变了循环叠加顺序。根据上述公式进行卷积运算可以分解为两个步骤:

1、特征图均按照输入通道维度进行数据采样,采样的数据构成特征图向量, 其维度为(1, Nif,)。卷积核采用按输出通道进行同位置独立采样(第一次运算时为所有输出通道卷积核第一行第一个点的所有输入通道数据),采样后的数据构成二维矩阵,其维度为(Nif, Nof)。采用后的特征图向量与卷积核矩阵进行向量乘矩阵运算,即可得到特征图结果向量,其维度为(1, Nof),这些结果对应输出特征图第一行第一个点的所有通道数据。该过程如图 12 所示。

2、向右向下(向右至行尾后,从第二行第一个点开始)依次取特征图向量, 此过程可以看作是步骤 1 中采样位置在特征图张量上的向右向下依次滑动。保持步骤 1 中的卷积核矩阵不变,重复步骤 1 即可获得所有输出特征图中间结果,其 过程如图 12 所示。

3、向右向下依次卷积核向量构成卷积核矩阵,重复步骤 1、2,获得第二组中间结果,这些中间结果与步骤 2 中所有结果进行对应位置相加,最终获得所有输出结果。应用此方法能够突破原有方案中卷积核尺寸限制以及卷积类型的限制,通过循环叠加次数来实现不同尺寸卷积运算。

卷积运算模块主要由卷积输入控制模块、卷积输出控制模块、卷积计算阵列模块和卷积状态控制、BN 输入控制模块、BN 融合模块、激活融合模块组成。图 13 为卷积运算模块的结构框图。

其中卷积计算阵列模块包含 32 个计算单元(PE),每一个 PE 能一次完成 32 个数的乘累加运算。整个系统设计中包含 32 个并行排列的 PE。每个 PE 内部由 32 个乘累加器组成,接收输入特征图、卷积核及中间结果。如图 14 所示,每 个 PE 内部的 32 个 MAC 相互级联,主要针对常规的卷积运算。

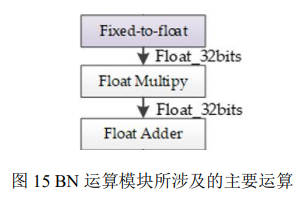

BN 运算模块中包含 32 个 BN 处理单元,可以同时计算 32 个点的批量标准化及反量化运算,分别对应 32 个计算通道。每个计算单元中主要执行 3 步运算。定点转浮点、浮点乘法、浮点加法。如图 15 所示:

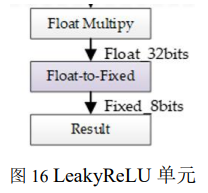

激活运算模块中包含 32 个激活处理单元,可以同时计算 32 个点的激活及量化运算。本层的两个参数存储在片上的两块 ROM 中,在换层时会提前被读出, 通过判断当前点的正负来参与运算。此外,本模块还会进行一个定点转浮点的运算。从而得到了 8bit 定点的输出结果。如图 16 所示:

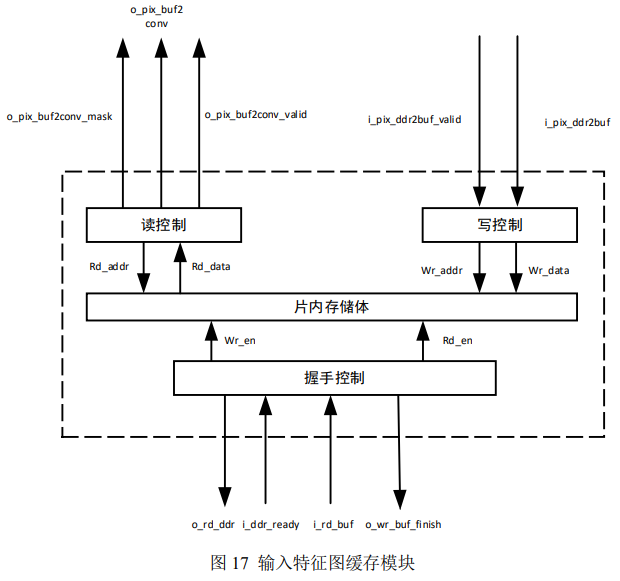

输入特征图缓存模块的功能是暂存来自 DDR 控制器发送的输入特征图数据,并对运算模块发出的读请求进行响应,按照所需的数据顺序进行读出。

输入特征图缓存模块由写控制、读控制、请求处理控制、片上存储体组成, 如图 17 所示。其中,存储体是一块数据位宽为 256 的 BRAM 构成。大小为 1MB

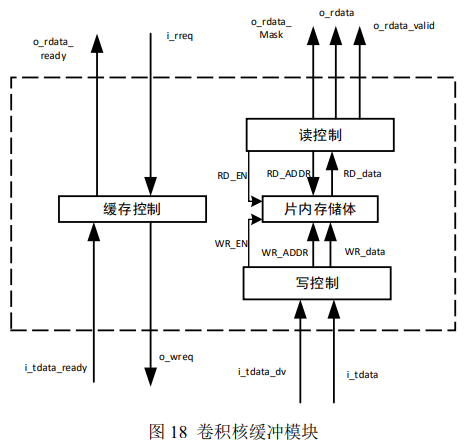

卷积核缓存模块的功能是对卷积核数据进行缓存,并处理来着卷积运算模块的读请求,将数据按特定的顺序反复读出。该缓存模块能够同时存储 32 个输出通道的卷积核。

卷积核缓存模块由写控制、读控制、请求处理控制、片上存储体组成,如图 18 所示。其中,存储体是 32 块数据位宽为 256 的 BRAM 构成,大小为 1MB。

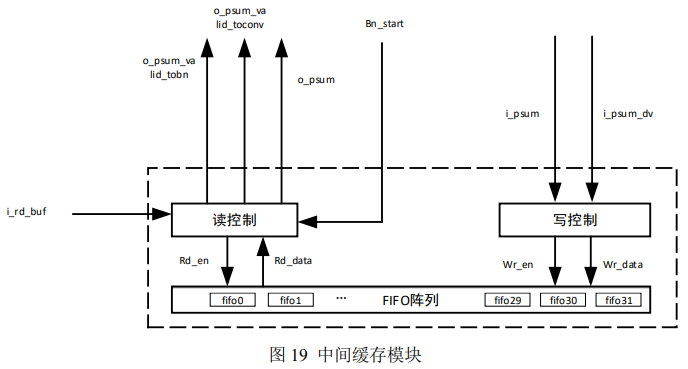

中间缓存模块的功能是对卷积运算模块输出的中间结果进行缓冲,当卷积运算完成时,为卷积后续的 BN 模块提供数据。

如图 19 所示,中间缓存模块由读控制、写控制以及 FIFO 存储阵列组成,其中 FIFOs 由 32 个端口位宽位 32 的 FIFO 组成。总大小为 10243232b。

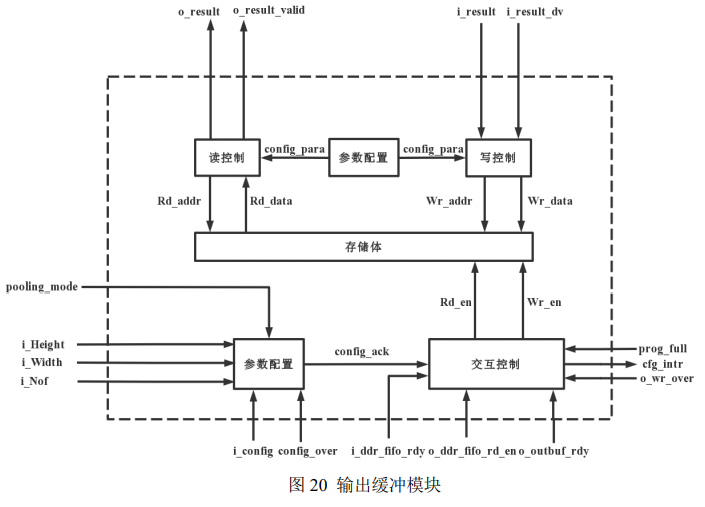

输出缓存模块用于存储经过 BN,融合等操作的计算结果。当存储的数据达到预设值时,向 DDR 发送数据,该缓冲区大小为 1MB。

输出缓存模块由参数配置、读控制、写控制、交互控制和存储体组成,如图 20 所示。

本作品在 Xilinx VC709 板卡上实现了改进版 YOLOv2 目标检测算法。硬件 部分已完成了指令处理子系统、处理引擎子系统以及存储子系统。其中,处理引擎子系统包含了普通、转置、空洞卷积,以及池化、激活等操作,满足本设计所采用的改进版 YOLOv2 的运算需求。

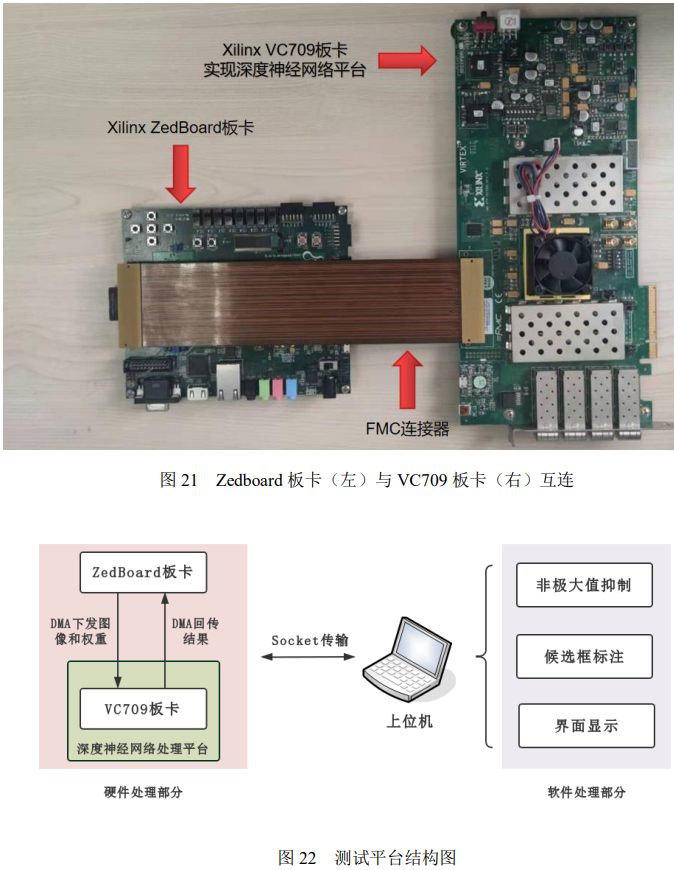

本作品的具体测试平台包括上位机演示系统、Xilinx Zedboard 板卡以及 Xilinx VC709 板卡。其中,Zedboard 板卡和 VC709 板卡通过 FMC 连接器交互, 如图 21 所示。本作品具体运行流程如下:

1、上位机演示系统负责前端界面的显示,并完成待检测图片的加载、回传结果的后处理及展示。待检测图片和回传结果经由网线传输。

2、Zedboard 板卡负责 Linux 操作系统及驱动的加载,并接收上位机传送的待测图片,并将待测图片、YOLOv2 配置指令和相关参数经由 FMC 连接器送与 VC709 板卡处理,检测结果通过 FMC 连接器返回,并发往上位机。

3、VC709 板卡完成了指令处理子系统、处理引擎子系统以及存储子系统的实现,该板卡根据卷积神经网络的配置指令和参数,对待测图像进行检测,并通 过 FMC 连接器将检测结果返回给 Zedboard。

1、FPGA 板卡:Xilinx Zedboard 和 Xilinx VC709

2、数据传输:双绞线、FMC 连接器

3、设计软件:Xilinx Vivado 2019.2

4、用于对网络结果进行后处理及界面显示的上位机

1、准确性:利用 GPU 平台改进的 YOLOv2 网络在 DOTA 遥感数据集上测试,mAP 指标可以达到 69.0。我们在 FPGA 上所实现的该深度卷积神经网络的测试结果与 GPU 平台运行结果一致,保证了作品的准确性。

2、运行效率:基于改进的 YOLOv2 网络,对单张尺寸为 1024x1024 的图像进行多目标检测的处理时间为 0.9248 秒。若加上数据传输、结果后处理以及图像显示等过程,单张图像的处理及展示时间约为 1.5 秒。(在视频展示时,多张 图测试过程中,由于作品的处理速度快于每张图所展示的时长,所以可以看到原图和检测结果几乎同时显示。)

3、功耗:本作品在 200M 的时钟频率下,总功耗为 16W,单位功耗处理能力为 25GOPs/W。与 GPU 平台相比,具有更低的功耗和更优的能耗比。因此本作品更适合部署在对实现平台的体积、重量、功耗有限制的应用环境中。

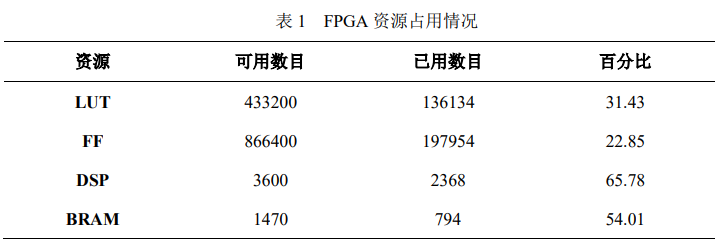

本作品 FPGA 资源占用情况如表 1 所示,其中 DSP 占用了 65.78%,BRAM 占用了 54.01%,资源使用情况合理。该硬件平台能够有效部署 YOLOv2 目标检测网络,实现多尺度、多类型目标的高精度快速检测及分类。

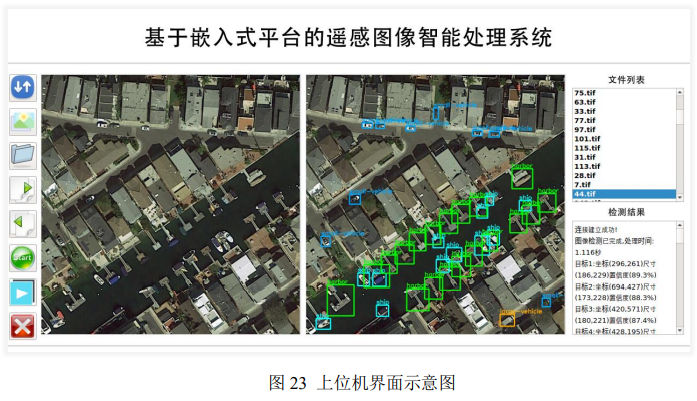

本作品基于改进的 YOLOv2 网络,在实现飞机、车辆等多目标的检测的同时, 可实现多检测目标的分类,其上位机界面显示结果如图 23 所示。

(1)目前卷积神经网络的部署仍采用人工方式生成对应的指令代码,未来可结合软件编译工具,是指令代码生成自动化,从而达到多种网络的动态部署和资源的动态分配。

(2)目前该作品暂不支持深度可分离卷积、分组卷积和 Shortcut 等运算方式,未来可在处理引擎子系统上进行扩展,进一步提高该作品的通用性。

(3)目前我们在 FPGA 上实现了深度卷积神经网络。但 FPGA 作为一种通用处理器,其处理性能和功耗控制都存在瓶颈。因此后续我们会以本作品为基础, 设计与开发用于遥感图像在轨实时处理的 ASIC 芯片。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群