01

—

使用AURIX TOM模块生成交流电机的PWM驱动

1简介

2 GTM and PWM 的生成

2.1 用于PWM生成TOM模块介绍

2.2居中对齐和边沿对齐PWM

3 PWMAC驱动器功能概述

3.1 PWMAC通道和顺序

3.2 ADC的PWMAC触发

4带GTM的PWMAC驱动器

4.1 ADC触发

5实施示例–PWMAC

5.1简介

5.2 PWMAC驱动程序

5.3 PWMAC驱动程序API

5.4驱动程序配置

1. 简介

通过使用英飞凌AURIX™系列产品中引入的通用计时器模块(GTM),可用于交流电动机控制的PWM信号的生成。

》交流电机的驱动

如下图所示:只需要在A,B,C三相提供120相位差的正弦电压,电机就会稳定的转动起来,调节正弦电压的幅值和频率,就能调节电机的转速和扭矩。这是我们所需要的输出。

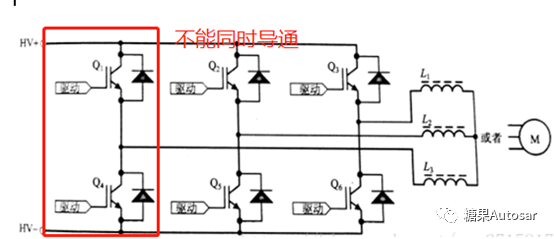

》三相桥臂电路

而我们所提供的输入是稳压直流电源,电机控制中的控制二字指的就是通过6路PWM,控制三相桥臂电路中的6个MOS管的开断,来达到直流电源变正弦交流的目的。

注意:每个桥臂上有两个电力电子器件,比如IGBT。这两个IGBT不能同时导通,否则就会出现短路的情况。

》死区

因此,设计带死区(英飞凌中成为Deadtime)的PWM波可以防止上下两个器件同时导通。也就是说,当一个器件导通后关闭,再经过一段死区,这时才能让另一个导通。

》》死区的原理和作用

死区就是在上半桥关断后,延迟一段时间再打开下半桥或在下半桥关断后,延迟一段时间再打开上半桥,从而避免功率元件烧毁。这段延迟时间就是死区。总结:死区持续的时间区间内上、下半桥的元件都是关断的。

》》死区的副作用

死区时间是PWM输出时,为了使H桥或半H桥的上下管不会因为开关速度问题发生同时导通而设置的一个保护时段,所以在这个时间,上下管都不会有输出,当然会使波形输出中断,死区时间一般只占百分之几的周期。但是PWM波本身占空比小时,空出的部分要比死区还大,所以死区会影响输出的纹波,但应该不是起到决定性作用的。

GTM提供了两种可用于PWM生成的模块:

•定时器输出模块(TOM)

•与ARU连接的定时器输出模块(ATOM)

这两个模块均可用于生成多个PWM信号,相互依赖或相互独立。

TOM模块只能用于生成简单的PWM。 ATOM模块还可以生成复杂的信号,这些信号主要用于引擎管理应用程序中的点火/喷射脉冲的生成。

每个TOM(定时器输出模块)最多包含16个通道(TOM_CHx)。每个通道都有其自己的16位计数器,可用于生成PWM的边沿。

TOM通道分为两组,每组八个通道。每个组均由TOM全局通道控制(TGC)单元控制。

计数器频率可以从CMU(CMU_FXCLK)提供的五个预分频器时钟之一中选择。此外,每个TOM通道均含有两个捕获比较单元(CCU0和CCU1),以将计数器CN0与可配置值进行比较。 CCU0用于确定PWM的持续时间,而CCU1定义占空比持续时间。

使能后,在实际开始生成PWM之前,PWM通道首先计数到CM0的值。因此,第一个PWM周期的持续时间取决于CN0的初始值,该值在复位后为零。

注意:可以给通道预加载不同的CN0值,以实现不同相位的PWM。

可以在CM0匹配(周期)上产生一个中断,而在CM1匹配(占空比)下产生另一个中断。。当TOM通道的计数器被该通道的前一个通道复位时,可以定义两个捕获比较单元,以生成任意PWM周期的脉冲,该周期由前一个TOM通道定义。

对于每个捕获比较单元,都有一个影子寄存器来存储下一个PWM周期的PWM特性个除此之外,还有一个为新的PWM周期选择不同的时钟预分频系数的影子寄存器。

关于这个模块的详细介绍请参见上一篇文章。

2.2 居中对齐和边沿对齐PWM

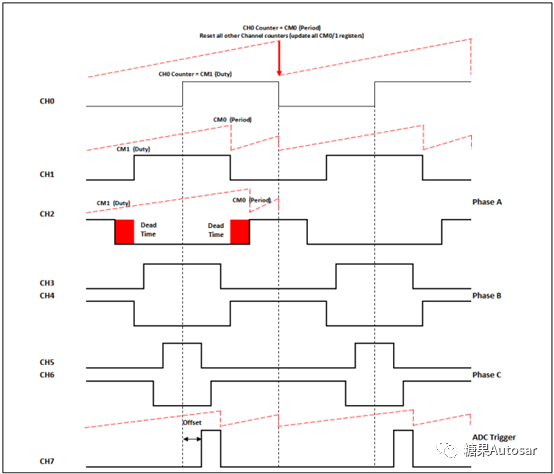

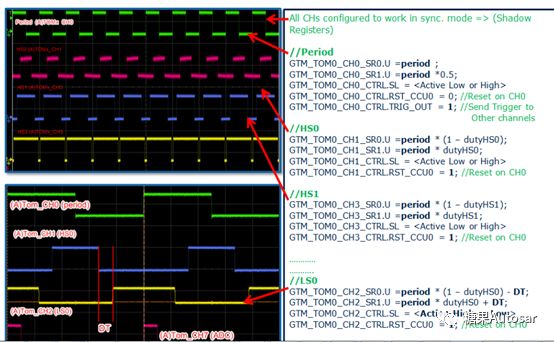

为了使用(A)TOM来实现居中对齐和边沿对齐PWM,第一个通道(CH0)必须向所有其他后续通道提供主PWM周期和复位信号。 下图提供了一个示例:

生成任何类型的PWM调制以及对称/非对称死区时间,使用GTM都可以考虑以下方法:

-配置(A)TOMx_CH0(主资源),以将复位信号发送到所有其他通道 。

-将其他所有通道也配置为在来自CH0(TRIG [x-1])的触发信号上也要复位

-将正确的公式应用于所有相位和触发通道的CM0(周期)和CM1(占空比)寄存器(CH1..CH7)。

在以下各段中将提供一个实际的配置示例。

PWMAC驱动器的主要目标是为DC / AC逆变器生成启动命令,并有可能在命令生成期间的特定瞬间触发AD转换。

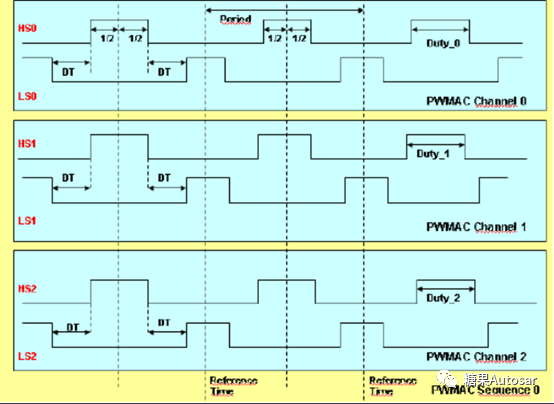

PWMAC通道(或PWMAC相位)由两个带死区时间的中心对齐PWM通道组成。这两个PWM通道可以是反相器相位的高端和低端。 PWMAC通道不能单独存在,而必须始终是PWMAC序列的一部分。每个PWMAC通道都有其独立的占空比。

PWMAC序列是共享相同参考时间的PWMAC通道的集合,因此序列中的所有PWM信号都以该参考时间为中心。此外,包含在相同序列中的所有PWMAC通道共享相同的周期和死区时间。下图显示了三个PWMAC通道的PWMAC序列。

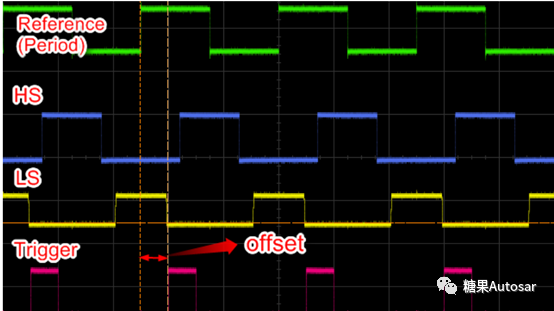

可选地,每个PWMAC序列都拥有另一个数字信号,称为PWMAC触发,可以用作触发AD转换的源。触发器以“参考时间”为中心,并且可以指定“偏移”。见下图:

如前几节所述,GTM提供了两种对实现PWMAC驱动程序均有效的模块:TOM和ATOM。

要实现一个PWMAC通道(或相位),该通道由两个具有指定死区时间的居中对齐的PWM组成,需要使用三个(A)TOM通道:

•通道0提供参考周期(主资源)

•其他两个通道,通常是CH [i]和CH [i + 1]

因此,要实现包含三相,需要的CH0以及其他六个(A)TOM通道的PWMAC序列,以实现3个高侧(HS)和3个低侧(LS)居中对齐的PWM信号。

需要将通道零配置为将CCU0触发(周期匹配)发送到其他通道(GTM_(A)TOM_CH0.TRIG_OUT = 1)。

所有其他通道都需要配置为在从通道零的TRIG_0上开始重置自己的计数器(CN0),或者在达到其自己的编程周期后复位。

要启用此选项,需要将位字段GTM_(A)TOM_CHx_CTRL.RST_CC0设置为1;

下图显示了一个生成带有三相加触发的序列的示例。

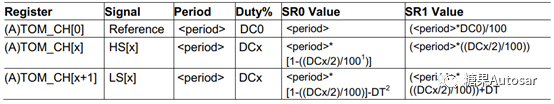

寄存器SR0(阴影寄存器)包含周期,而SR1包含占空比。为了生成居中对齐(或边沿对齐)的PWM信号,应采用以下公式:

当占空比HS0在[0.00,0.50](0%-100%)的范围内时。见下表:

每个(A)TOM通道都需要配置为以同步更新模式工作(使用影子寄存器)。下面代码提供了TOM[y]通道配置的示例。该配置对于ATOM还是有效的,区别在于ATOM的GTM_ATOM[y] _CH [i] _CTRL.B.MODE位字段必须设置为2(PWM模式),因为ATOM可以工作在四种不同的模式下,并且TGC寄存器(TOM全局控制)必须由AGC(ATOM全局控制)代替。以下是配置的代码示例:

| GTM_TOM[y]_TGC0_GLB_CTRL.B.UPEN_CTRL[i]=0x10;//enable CH0 update from shadow reg. SR0/SR1 GTM_TOM[y]_TGC0_ENDIS_CTRL.B.ENDIS_CTRL[i]=0x10; //enable channel on an update trigger GTM_TOM[y]_TGC0_FUPD_CTRL.B.FUPD_CTRL[i]=0x10; //Channel Force update enabled GTM_TOM[y]_TGC0_OUTEN_CTRL.B.OUTEN_CTRL[i]=0x10//Output (A)TOM_OUT(0) enable/disable GTM_TOM[y]_CH[i]_CTRL.B.CLK_SRC_SR = <clockSrc>; //Clk source select for channel 0,1, GTM_TOM[y]_CH[i]_CTRL.B.SL = 0; //Signal level for duty cycle 0B Low signal level, 1B High signal level GTM_TOM[y]_CH[i]_SR0.U = <Period>; GTM_TOM[y]_CH[i]_SR1.U = <Duty>; //Special Configuration GTM_TOM[y]_CH[i]_CTRL.B.TRIGOUT = 1; //Only needed for the CH0 (Reference Period) GTM_TOM[y]_CH[i]_CTRL.B.RST_CCU0 = 1; //Needed for each Phase Channel != CH0 //Only for ATOMs GTM_ATOM[y]_CH[i]_CTRL.B.MODE = 2; //=> SOMP Mode (PWM Generation) |

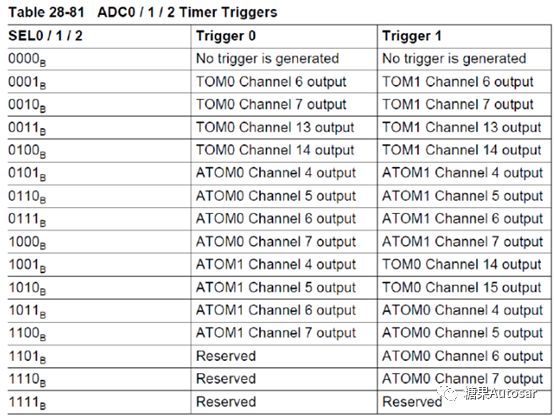

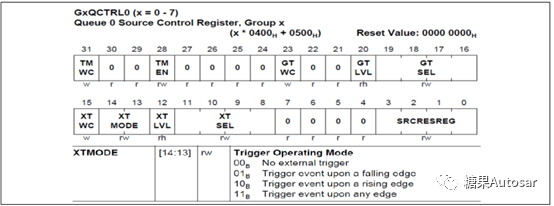

GTM模块提供了多种源来内部触发Delta-SigmaADC或ADC。下图显示了可用于触发常规ADC的定时器通道。

注意:并非所有的ATOM/TOM模块都可以触发ADC转换。有关详细信息,请参阅最新版本的用户手册。注意:这些图未显示所有可用的触发源要触发相应的ADC通道,需要在位字段XTMODE中配置两个触发事件。要测量相电流,只需要一个触发事件即可。见下图:

在PWMAc序列内部,触发信号的配置必须与其他相位信号完全相同,

配置要求如下:

-同步更新

-触发来自CH0(参考)的CCU0复位。

要写入SR0和SR1寄存器的值取决于偏移量和触发信号有效沿。

下面代码提供了一个触发器配置示例(TOMy_CH7)。

| GTM_TOM[y]_TGC0_GLB_CTRL.B.UPEN_CTRL7=0x10;//enable CH0 update from shadow reg. SR0/SR1 GTM_TOM[y]_TGC0_ENDIS_CTRL.B.ENDIS_CTRL7=0x10; //enable channel on an update trigger GTM_TOM[y]_TGC0_FUPD_CTRL.B.FUPD_CTRL7=0x10; //Channel Force update enabled GTM_TOM[y]_TGC0_OUTEN_CTRL.B.OUTEN_CTRL7=0x10//Output (A)TOM_OUT(0) enable/disable GTM_TOM[y]_CH7_CTRL.B.CLK_SRC_SR = <clockSrc>; //Clk source select for channel 0,1, GTM_TOM[y]_CH7_CTRL.B.SL = 0; //Signal level for duty cycle 0B Low signal level, 1B High signal level if (triggerEdge == IfxGtm_Raising) { trigDuty = <CH0_Duty> + <triggerOffset>; GTM_TOM[y]_CH7_SR0.U = trigDuty + <triggerWidth>; GTM_TOM[y]_CH7_SR1.U = trigDuty; Else { trigPeriod = <CH0_Duty> + <triggerOffset> GTM_TOM[y]_CH7_SR0.U = trigPeriod; GTM_TOM[y]_CH7_SR1.U = trigPeriod- <triggerWidth>; } GTM_TOM[y]_CH7_CTRL.B.RST_CCU0 = 1; Needed for each Phase Channel != CH0 |

以下伪代码提供了VADC配置的示例。在该示例中,VADC Group0和Group1由TOM0_CH7和TOM1_CH7触发。

| sint32 vadc_init(void) { uint32 gr, ch; SCU_vResetENDINIT(0); VADC_CLC.U = 0x00000000; // load clock control register while ((VADC_CLC.U & 0x00000002) == 2); // wait until module is enabled VADC_KRST0.B.RST = 0x1; VADC_KRST1.B.RST = 0x1; while (!VADC_KRST0.B.RSTSTAT) ; VADC_KRSTCLR.B.CLR = 0x1; SCU_vSetENDINIT(0); // setting clocks */ VADC_GLOBCFG.U = 0x000008009; //fspb divided by 10 (fadci=10MHz), fadcd=fspb VADC_GLOBCFG.B.SUCAL = 0x1; // turn on calibration for (gr = 0; gr < VADC_GROUPS; gr += 1) MEM (&VADC_G0ARBCFG.U + gr * 0x100) = 0x13; for (gr = 0; gr < VADC_GROUPS; gr += 1) MEM (&VADC_G0ARBPR.U + gr * 0x100) = 0x07000321 | 0x0888; /* use the same setting for all groups VADC0,1,2….*/ for (gr = 0; gr < VADC_GROUPS; gr++) { for (ch = 0; ch < VADC_CHANNELS_PER_GROUP; ch++) { |

| /* setting result control registers for all channels (VADC_GxRCRy) */ MEM (&VADC_G0RCR0 + gr * 0x100 + ch) = (1 << 31); //Enable Service Request /* setting channel registers for all channels (VADC_GxCHCTRy) */ MEM (&VADC_G0CHCTR0 + gr * 0x100 + ch) = 0x00100000; // GLOBAL Result Register } // setting STC to 0x1F, 12 bit resolution (VADC_GxICLASS0) */ MEM (&VADC_G0ICLASS0.U + gr * 0x100) = 0x00000003; /* we wait until calibration is finished for this group VADC_GxARBCFG.CAL==0 */ while (MEM (&VADC_G0ARBCFG.U + gr * 0x100) & 0x10000000) ; } /* enable interrupt, enable and prio of group */ VADC_GLOBEVNP.U = 0x0; //Service Request Enable, Wait for Read Mode VADC_GLOBRCR.U = 0x81000000; // Specific Configuration for ADC0 and ADC1 Configuration */ VADC_G0CHASS.U = 0x000000FF; /*all channels in the Gr0 assigned as priority channel*/ VADC_G1CHASS.U = 0x000000FF; /*all channels in the Gr1 assigned as priority channel*/ VADC_G0ASMR.B.ENGT =1; //Conversion req. are issued if at least one pending bit is set VADC_G0ASMR.B.ENTR =1; //Enable External Trigger (GTM) VADC_G1ASMR.B.ENGT =1; //Conversion req. are issued if at least one pending bit is set VADC_G1ASMR.B.ENTR =1; //Enable External Trigger (GTM) VADC_G0ASCTRL.U = EXTERNAL_TRIGGER << 8 /**! XTSEL => use gate as trigger source */ | TRIGGER_EVENT_RISING_EDGE << 13 /**! XTMODE: 3 = trigger on any edge*/ | 1 << 15 /**! allow write access to trigger config */ | ADC_X_TRIG_0 << 16 /**! GTSEL: => use GTM ADC Trigger 0 */ | 1 << 23 /**! allow write access to gate config */ ; VADC_G1ASCTRL.U = EXTERNAL_TRIGGER << 8 /**! XTSEL => use gate as trigger source */ | TRIGGER_EVENT_FALLING_EDGE<< 13 /**! XTMODE: trigger Edge Sel*/ | 1 << 15 /**! allow write access to trigger config */ | ADC_X_TRIG_1 << 16 /**! GTSEL: => use GTM ADC Trigger 1 */ | 1 << 23 /**! allow write access to gate config */ ; /*! GTM Configuration - Select correct trigger from ADC0/ADC1 */ GTM_ADCTRIG0OUT0.B.SEL0 = 2; /**! TOM0_CH 7 ==> adc_x_trig_0 => ADC0*/ GTM_ADCTRIG1OUT0.B.SEL1 = 2; /**! TOM1_CH 7 ==> adc_x_trig_1 => ADC1*/ VADC_G0ASSEL.U = 0x000000FF; /**! channel 0 is selected as part of the scan*/ VADC_G1ASSEL.U = 0x000000FF; /**! channel 0 is selected as part of the scan*/ return (0); } |

驱动程序演示了如何使用GTM生成居中对齐的PWM波形。并且本章将概述驱动程序的API的含义(应用程序编程接口)及其用法。

此PWMAC驱动程序提供以下功能:

•基于TOM或ATOM模块的PWMAC HS /LS PWM生成

•每个序列的可配置相位数

•每个序列的灵活ADC触发器生成

•每个相位灵活的“死区时间”生成(对称)

•单个PWM信号的有效电平是可配置的。

PWMAC驱动程序使用一些基本方法在TOM / ATOM模块上生成PWM。

这些方法或函数在IfxLldPwm.c文件(PWM底层驱动程序)中实现。见下图为驱动程序的架构:

函数名 |

函数声明 |

功能描述 |

IfxPwmAc_configSequence |

IfxPwm_Status IfxPwmAc_configSequence (IfxPwmAc_Sequence seqId, IfxPwmMAC_CfgSequence* ptrCfgSequence) |

PWMAC <seqId> Sequence configuration. |

IfxPwmAc_setEnable |

IfxPwm_Switch IfxPwmAc_setEnable ( IfxPwmAc_Sequence pwmSequenceId, IfxPwmAc_SwitchMode enDisSw , IfxPwm_Status* status ) |

Function to enable the Sequence <seqId> |

IfxPwmAc_configTrigger |

IfxPwm_Status IfxPwmAc_configTrigger ( IfxPwmAc_Sequence pwmSequenceId, uint32 triggerOffset, IfxPwm_ActiveEdge triggerEdge) |

Function to configure a trigger for the Sequence <seqId> |

IfxPwmAc_setDutyPeriod |

IfxPwm_Status IfxPwmAc_setDutyPeriod(Ifx PwmAc_Sequence seqId, uint32 period, uint32* duty); |

Function to update the Period and/or the duty of all the AC Phases inside the Sequence <seqId> |

传递给所有函数的<seqId>索引相应的结构体数组<sequenceChIdArray>中的元素,它包含所有序列的静态配置。

为了配置驱动程序,要做的第一步是定义一个包含序列静态配置的数组。数组为每个序列指定要使用的(A)TOM通道。该数组在pwmAc_test.c文件中定义

| IfxPwmAc_SequenceChannelsDef sequenceChIdArray[PWMAC_SEQ_MAX] = { //Sequence1 (FirstSequence), { IfxGtm_Tom, //Module Time: TOM or ATOM IfxGtm_Tom0, //Module Number { [0]=IfxGtm_TomCh1, //HS0 Channel, LS0 always the next CH (i.e. CH2) [1]=IfxGtm_TomCh3, //HS1 Channel, LS1 always the next CH (i.e. CH4) [2]=IfxGtm_TomCh5 //HS2 Channel, LS2 always the next CH (i.e. CH6) }, IfxGtm_TomCh7 }, //Trigger Channel (if needed), shall be always CH7 or CH14 //Sequence2 (SecondSequence), { IfxGtm_Tom, IfxGtm_Tom1, { [0]=IfxGtm_TomCh1, [1]=IfxGtm_TomCh3, [2]=IfxGtm_TomCh5 }, IfxGtm_TomCh7 }, //Sequence3, ……… ……… }; |

第二步是配置序列:

| IfxPwmAc_CfgSequence seqCfg,seqCfg1; /*First Sequence*/ seqCfg.period = PWM_PERIOD; //Reference Period seqCfg.PwmAcPhaseNumber = 3; //3 phases seqCfg.deadTimes[0] = 500; //=> DT 1st Phase (5us) seqCfg.deadTimes[1] = 600; //=> DT 2nd Phase (6us) seqCfg.deadTimes[2] = 700; //=> DT 3rd Phase (7us) /*Signal Levels*/ seqCfg.signalLevelHS[0] = IfxGtm_SignalHigh; seqCfg.signalLevelHS[1] = IfxGtm_SignalHigh; seqCfg.signalLevelHS[2] = IfxGtm_SignalHigh; seqCfg.signalLevelLS[0] = IfxGtm_SignalLow; seqCfg.signalLevelLS[1] = IfxGtm_SignalLow; seqCfg.signalLevelLS[2] = IfxGtm_SignalLow; seqCfg.dutyCycles[0] = 500; // DC 1st Phase 50.0% seqCfg.dutyCycles[1] = 250; // DC 2nd Phase 20.0% seqCfg.dutyCycles[2] = 750; // DC 3rd Phase 75.0% /*Second Sequence*/ seqCfg1.period = PWM_PERIOD; seqCfg1.PwmAcPhaseNumber = 2; //2 phases seqCfg1.deadTimes[0] = 500; //=> DT 1st phase (5us) seqCfg1.deadTimes[1] = 600; //=> DT 2nd phase (6us) seqCfg1.signalLevelHS[0] = IfxGtm_SignalHigh; seqCfg1.signalLevelHS[1] = IfxGtm_SignalHigh; seqCfg1.signalLevelLS[0] = IfxGtm_SignalLow; seqCfg1.signalLevelLS[1] = IfxGtm_SignalLow; seqCfg1.dutyCycles[0] = 500; // 50.0% seqCfg1.dutyCycles[1] = 250; // 25.0% |

| /**! * PWM AC channels mapping to IO PORTs */ IfxPwm_ModulePortOutTable modulePortOutTable[NUM_TOUT_PINS] = { /*timer------, channel------, port, pin, toutNum, iocrCfg*/ { IfxGtm_Tom0, IfxGtm_TomCh0, (uint32*) &P00_IOCR8, 9, TOUT18, A_COL }, //P00.9 { IfxGtm_Tom0, IfxGtm_TomCh1, (uint32*) &P00_IOCR8, 10, TOUT19, A_COL },//P00.10 HS { IfxGtm_Tom0, IfxGtm_TomCh2, (uint32*) &P00_IOCR8, 11, TOUT20, A_COL }, //P00.11 LS (0) { IfxGtm_Tom0, IfxGtm_TomCh3, (uint32*) &P00_IOCR12, 12, TOUT21, A_COL }, //P00.12 { IfxGtm_Tom0, IfxGtm_TomCh4, (uint32*) &P14_IOCR0, 1, TOUT102, A_COL }, //P14.1 { IfxGtm_Tom0, IfxGtm_TomCh5, (uint32*) &P10_IOCR8, 8, TOUT110, A_COL }, //P10.8 { IfxGtm_Tom0, IfxGtm_TomCh6, (uint32*) &P10_IOCR4, 4, TOUT106, A_COL }, //P10.5 { IfxGtm_Tom0, IfxGtm_TomCh7, (uint32*) &P13_IOCR0, 2, TOUT93, A_COL }, //P13.2 (TRIG) { IfxGtm_Tom1, IfxGtm_TomCh0, (uint32*) &P20_IOCR12, 12, TOUT68, A_COL }, //P20.12 { IfxGtm_Tom1, IfxGtm_TomCh1, (uint32*) &P20_IOCR12, 13, TOUT69, A_COL }, //P20.13 HS (0) { IfxGtm_Tom1, IfxGtm_TomCh2, (uint32*) &P20_IOCR12, 14, TOUT70, A_COL }, //P20.13 LS (0) { IfxGtm_Tom1, IfxGtm_TomCh3, (uint32*) &P14_IOCR0, 0, TOUT80, B_COL }, //P14.0 HS (1) { IfxGtm_Tom1, IfxGtm_TomCh4, (uint32*) &P00_IOCR4, 5, TOUT14, B_COL }, //P00.5 LS (1) { IfxGtm_Tom1, IfxGtm_TomCh5, (uint32*) &P00_IOCR4, 6, TOUT15, B_COL }, //P00.6 HS (2) { IfxGtm_Tom1, IfxGtm_TomCh6, (uint32*) &P00_IOCR4, 7, TOUT16, B_COL }, //P00.5 LS (2) { IfxGtm_Tom1, IfxGtm_TomCh7, (uint32*) &P00_IOCR8, 0, TOUT17, B_COL }, //P00.8 (TRIG.) …… }; |