AXI总线在FPGA设计中使用越来越频繁,但初学的同学经常会因为对协议的理解不够深入,写出来的代码经常会出现死锁等问题,对FPGA设计与调试带来很多不必要的麻烦。为了解决这个问题,我们可以使用Vivado生成AXI VIP(AXI Verification IP)来对自己设计的AXI接口模块进行全方位的验证(如使用VIP的Master、Passthrough、Slave三种模式对自己写的AXI接口进行仿真验证),提前规避和发现一些不满足AXI总线规范的设计问题。本文就跟大家分享如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法。

01

IP添加完成就可以在tb中实例化。

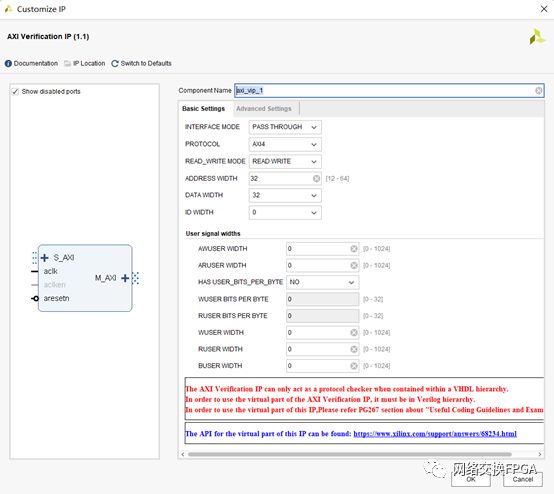

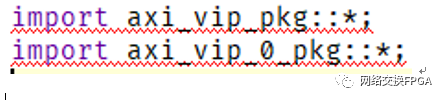

1.2、在sv格式的tb中加入下面两条import语句,第一个import是固定不变的,axi_vip对应axi_vip_pkg,axi-stream vip对应axi4stream_vip_pkg。

第二个import是导入刚才例化的vip的pkg,格式为import {Component Name}_pkg::*; 比如Component Name为axi_vip_0,则import如下图第二行。

vivado自带的编辑器会提示找不到import的这些pkg,但不会影响仿真。

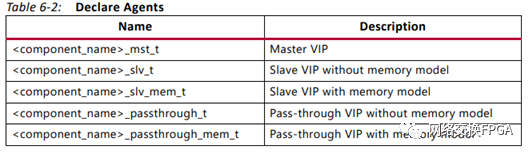

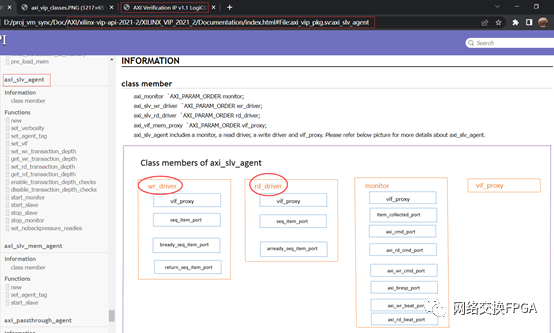

1.3、 在tb中声明相关的agent,使用vip的agent和它支持的一些函数就能实现仿真的功能。AXI vip支持的agent类型如下:

(AXI Verification IP v1.1 第47页)

如果测试一个AXI Master接口,可以声明一个自带memory model的slave agent,结尾为mem_t:

这种自带memory model的slave可以在执行start();之后自动生成AXI Slave时序,支持数据的写入和读出,也支持对memory内容的初始化和后台读写操作。

1.4、Start前的初始化步骤

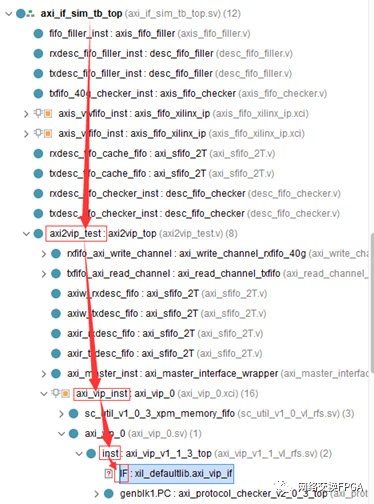

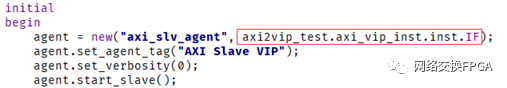

使用new函数将agent指定到待仿真的vip的IF上,

第二行:为agent设置一个标签,在使用多个vip时,方便在仿真时的错误信息中看到是哪个vip产生的。

第三行:设置verbosity为0,为不展示详细的仿真信息。设置为400,则会在仿真时print出详细的仿真信息。(不常用)

第四行:启动slave,之后slave可以根据待测的Master接口的读写时序产生相应的slave时序,被Master进行读写。

仿真过程中,如果axi或axi stream总线上的时序出现了任何错误,vip都会自动结束(暂停)仿真过程,仿真记录的波形会停在总线时序出错的位置偏后一点,控制台中也会显示vip对错误的详细描述。

02

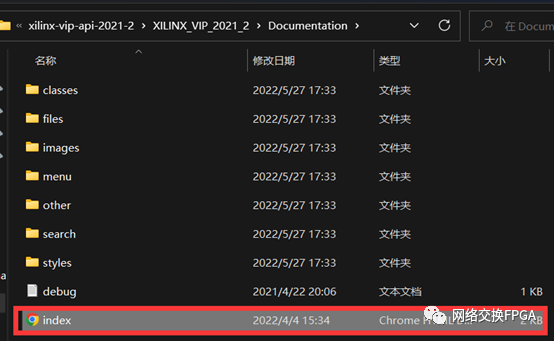

VIP的内部功能结构、支持的仿真函数在xilinx-vip-api-2021-2中有详细的说明。使用浏览器打开下图中的文件,便可以查看到。

axi-vip和axi-stream-vip都有自带的仿真例程,常用的功能在仿真例程中都有涉及。

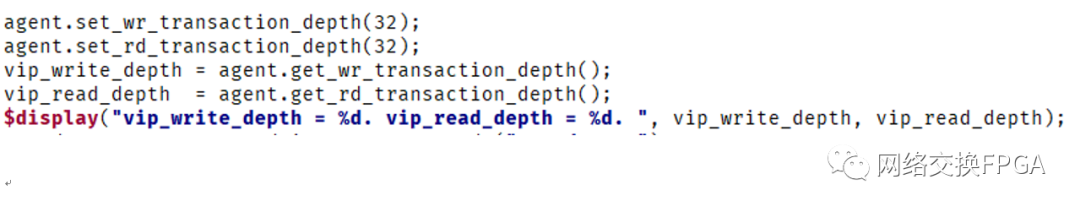

例如,设置slave vip的outstanding深度为32,执行下面代码的前两行即可。第3~4行则是获取agent的读写深度,可以以此确认前面设置的读写深度是否有效。

2.2 自定义ready信号

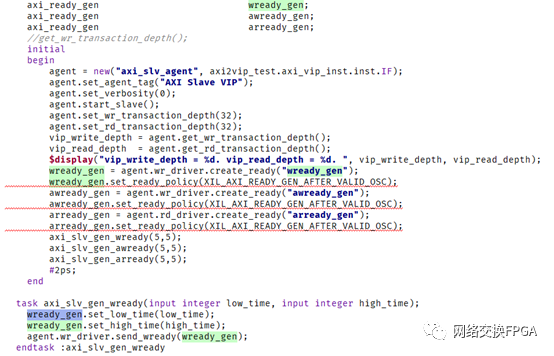

自带memory model的slave vip可以在start_slave();之后产生slave时序,也可以通过slave的wr_driver或rd_driver,自定义ready的高低电平周期。

下图代码展示的是为axi产生自定义wready、awready、arready的方法。在这个initial的末尾,只是为ready信号设置了一个低电平时间为5clk,高电平时间为5clk的初始状态。

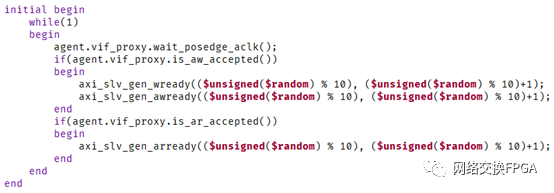

仿真开始后,可以在每次AW(写地址)通道握手之后,将新的awready和wready设置到agent上。在每次AR通道握手之后,将arready设置到agent上。

不能在axi的一个传输周期之内设置多组ready,否则vip会报出类似“太多未处理的ready”等错误信息,即使仿真依旧能够进行。

2.3 Axi slave vip的memory model

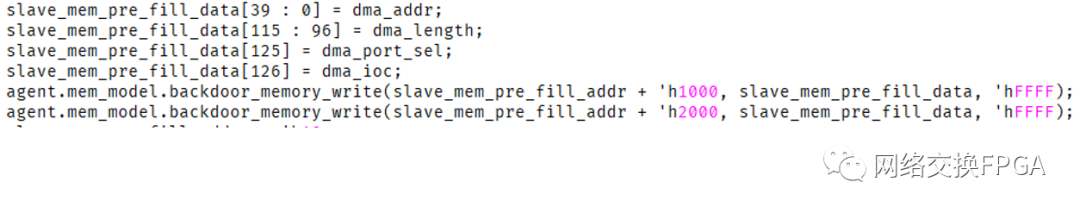

使用agent.mem_model.backdoor_memory_write等函数可以绕过vip直接对memory model进行一些读写操作,在xilinx vip api文档中有详细介绍,需要注意只有带memory model的vip才支持这类功能。

03

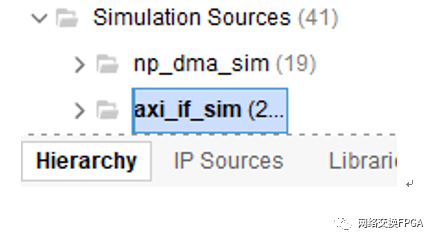

dma_sim_vivado工程中含有两个仿真源,一个是只测试AXI与AXI-Stream通路的回环测试工程,另一个是测试DMA所有功能包括接口的仿真工程。

其中,axi_if_sim中例化了一个axi vip和一个axi stream vip,其测试内容为:

1、 填充axi stream接口的rxfifo。

2、 axi master接口将rxfifo中的数据写入到axi vip的memory。

3、 axi master接口将ax vip中memoty的数据全部读出,并存入txfifo。

4、 txfifo上的axi-stream master接口将txfifo内的数据以axi-stream的形式传给axi stream vip。

5、最后比较axi stream vip接收的数据与一开始填充进rxfifo的数据是否一致,输出仿真结果。

np_dma_sim中的vip使用基本一致,增加的内容在于使用

作者:赵雨晨 图文排版:潘伟涛

责任编辑:潘伟涛