【摘要】汽车电子的快速发展对芯片的功能安全提出了更高的要求。芯片由于热应力、腐蚀和磨损等物理因素会产生随机硬件故障,工程师们需要通过安全的设计和合理的物理布局来规避或者减轻这些随机性的故障,以达到功能安全ISO 26262标准。

关键词:车规芯片,功能安全,冗余设计,ISO26262

1.引言

先进集成电路技术的快速发展推动着汽车行业走向智能化的未来,将这些先进技术应用到汽车中的同时,安全要求也在不断发展并变得更加严厉。为了应对这些挑战,工程师们正在寻求一种高度自动化的集成功能安全解决方案,以帮助产品更快地获得安全标准认证。

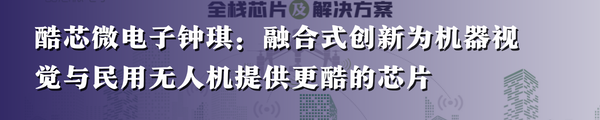

ISO 26262 标准[1]定义了四种不同的汽车安全完整性等级 (ASIL)——A、B、C 和 D——其中 ASIL-D 代表最高安全等级。根据 ASIL 级别,应计算和满足硬件架构指标,包括单点故障指标 (SPFM)、潜在故障指标 (LFM) 和硬件故障概率指标 (PMHF),如表 1 所示。其中,实时故障 (FIT) 率指的是在十亿个设备运行小时内可预期的随机故障数。

表1. 各个汽车安全完整性等级的目标指标

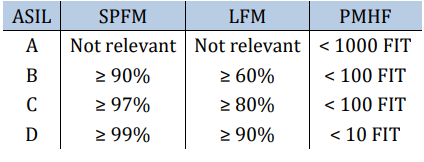

汽车芯片各个部件的安全等级取决于其所需实现的功能。如图1所示,安全气囊、防抱死刹车或动力转向等系统需要 ASIL-D 等级——适用于安全保证的最高严格程度——因为与它们故障相关的风险最高。此外,所有电气和电子系统都必须经过安全分析,例如尾灯和其他部件归类为 ASIL-A,前照灯和刹车灯归类为 ASIL-B,而自适应巡航控制归类为 ASIL-C或D[2]。

图1. 汽车各个功能安全完整性等级要求[2]

安全机制是芯片上检测和减轻故障的一种功能,它能使设计容忍故障并在检测到故障时反馈故障。为了正常工作,安全机制必须尽可能可靠。从芯片设计角度,工程师既需要在芯片架构上进行安全机制的设计,还需要考虑芯片安全策略在物理实现中的保障。下面本文将从芯片安全机制策略及其在物理实现过程中的保障两个方便进行简要概述。

2.芯片安全机制策略

芯片的故障分为随机硬件故障与系统硬件故障。系统故障是设计中的错误或疏忽。系统硬件故障是由人为错误引起的。相比之下,随机硬件故障是在硬件元件的生命周期内不可预测地发生并且遵循概率分布的故障。它以一种不确定的方式产生,并且与任何明显的问题或错误无关。因此,即使在没有明显缺陷或疏忽的正确设计中,我们也必须考虑随机故障发生的可能性。我们可以通过冗余、运行时间监控、验证测试等来缓解这种故障带来的危害。

2.1硬件冗余

硬件冗余是缓解随机硬件故障的有效方式。寄存器硬件冗余首先需要识别那些易受此类故障影响的逻辑路径。然后必须将这些路径上的寄存器进行冗余设计或替换成容错寄存器。实现的方式有 3 种,选择哪种方式取决于 ASIL 级别。

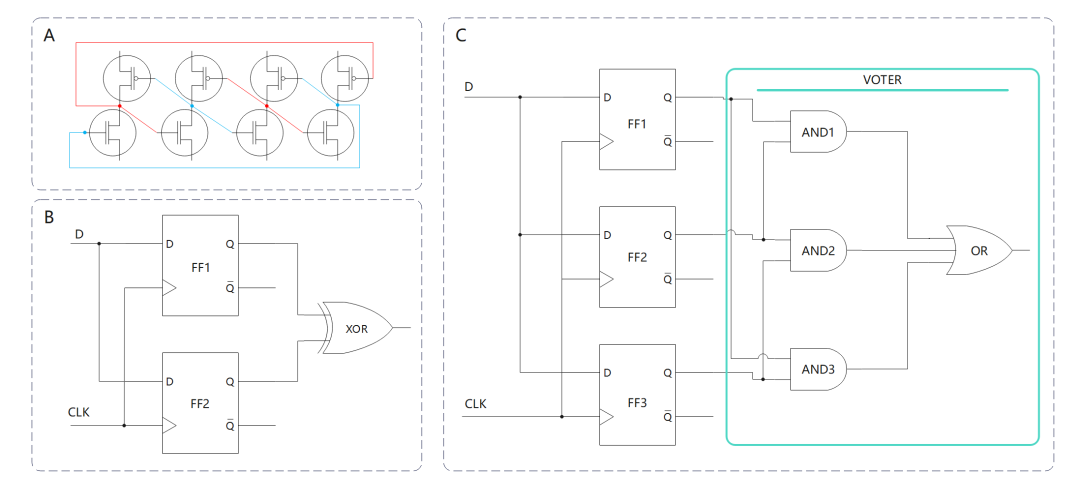

对于较低ASIL级别的路径,关键路径可以简单地使用容错寄存器来加强,以减少失败的机会,如图2A。在这种情况下,既不能纠正也不能检测到故障,只是简单地降低了故障的可能性。

第二种选择是使用双重模块冗余(DMR),如图2B。但是,这种方式仅对错误检测有用,对纠正无效。需要实施其他逻辑来确定发生错误时要做什么。

最严格的设计依赖于可以纠正故障的三重模块冗余 (TMR),如图2C。每个受影响的寄存器由三个相同功能的寄存器和特定逻辑组成的投票器替换。如果其中一个寄存器发生了其他两个没有发生的故障,则两个正确的值将占上风,从而投票器能隐藏故障。重要的是使三个寄存器彼此远离,并将它们与电路的其他部分电气隔离,以尽量减少可能损害它们相互独立性的任何交互。在这三种策略中,这种方案消耗的芯片面积最多。

图2. 寄存器冗余设计方案示意图。A. 容错寄存器,B. 双模块冗余,C. 三模块冗余。

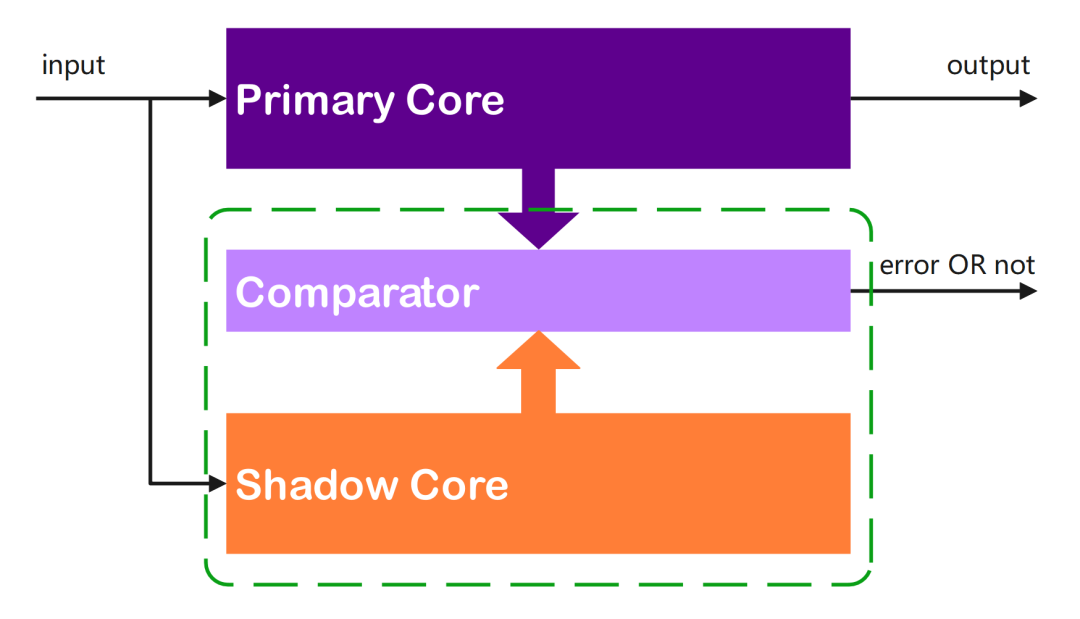

除了对关键路径中的寄存器进行冗余设计以外,另一种硬件冗余设计称为双核锁步(DCLS)。如图3所示,DCLS是通过复制同一个核,同时并行运行同一组操作时,可以比较锁步操作的输出以确定是否发生故障。与DMR类似,DCLS只能判断是否存在故障而无法纠正故障。

图3. 双核锁步示意图。

2.2校验/纠错码

在计算机、电信、信息理论和编码理论中,校验码(EDC)/纠错码(ECC)是信息传输中错误检测/纠正的工具,它们通常用在不可靠或者嘈杂的信道中。实现错误检测和纠正的一般思路是添加一些信息冗余(例如一些额外数据)到消息,从而使接收器可以用它来检查消息的一致性,并恢复被确定为损坏的数据。它们将消息作为二进制数传输的编码方案,即使某些位被错误地翻转,消息也可以被检测或者恢复。它们几乎用于所有消息传输情况,尤其是在 ECC 保护数据损坏的数据存储中。

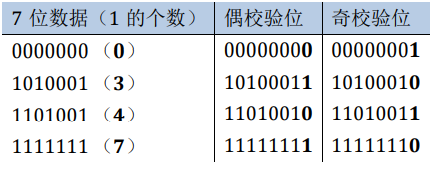

奇偶校验位(Parity bit) 或称校验比特(check bit) 是最简单的错误检测码,通过增加1bit信息冗余表示一个给定位数的二进制数中1的个数是奇数还是偶数。如表2所示,对于7位数据,在偶校验的情况下,如果该1的个数为奇数,则奇偶校验位值设置为 1,从而使整个集合(包括奇偶校验位)中出现 1 的总数为偶数。如果给定一组比特中 1 的计数已经是偶数,则奇偶校验位的值为 0。在奇校验的情况下,编码反转。如果值为 1 的位计数为偶数,则奇偶校验位值设置为 1,使整个组(包括奇偶校验位)中 1 的总计数为奇数。奇偶校验位只有在包括校验位在内的奇数个数据位发生改变时,才能检测出错误且不能对错误进行校正。

表2. 奇偶校验位原理示意图。

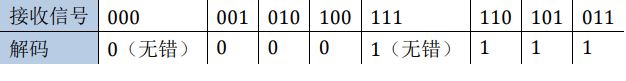

重复码是一种简单的纠错码。(n,1)重复码将每个数据位发送n次(n≥3),通过对比投票的方式进行解码得到正确数据位。以(3,1)重复码为例,经过嘈杂信道,接收器可能收到8个不同版本的输出,如表3。

表3. (3,1)重复码解码纠错对照表。

2.3共存免于干扰

在同一硬件单元中有时不可避免会出现具有不同ASIL安全级别开发的系统,由于在分配了不同ASIL的系统之间控制潜在故障的程度不同,因此以较高ASIL开发的系统的功能(如汽车制动系统)可能受到以较低ASIL开发的系统(如汽车制动灯系统)的影响。

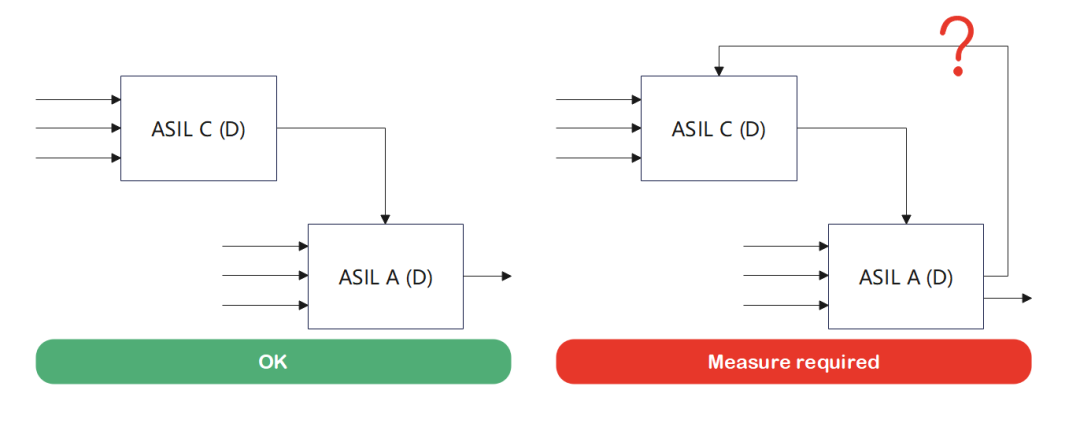

如图4所示,为了防止具有较高错误率 (ASIL-A) 的系统驱动需要较低错误率 (ASIL-C) 的系统,具有不太关键 ASIL 级别的(子)系统不能影响具有更关键 ASIL 的系统。左侧的设计表明 ASIL-A 系统不可能影响 ASIL-C 系统。这意味着 ASIL-C 系统相对于 ASIL-A 系统实现了免于干扰。但是在右侧的系统设计中,存在从 ASIL-A 到 ASIL-C 系统的数据/控制流。因此,ASIL-C 系统并没有实现免于干扰,至少在没有任何进一步分析的情况下,ASIL-C 系统会受到 ASIL-A 系统的影响。在这种情况下,需要采取进一步的设计或验证措施以实现不受干扰。例如,ASIL-C 系统可以首先检查 ASIL-A 系统数据的正确性。考虑到这一措施,ASIL-C 组件将实现免于干扰[3]。

图4. 两个不同安全级别系统之间免受干扰实现策略示意图。

3.安全机制物理实现保障

安全机制的设计需要通过物理布局布线之后才能移交给芯片代工厂加工。随着工艺的演进,单位面积内晶体管数量大幅增加,芯片中金属绕线层阻抗也增加。这些都对于芯片的功能安全具有极大的挑战,因此工程师们还需要从物理层面保障芯片的功能安全性。

3.1强健的绕线设计

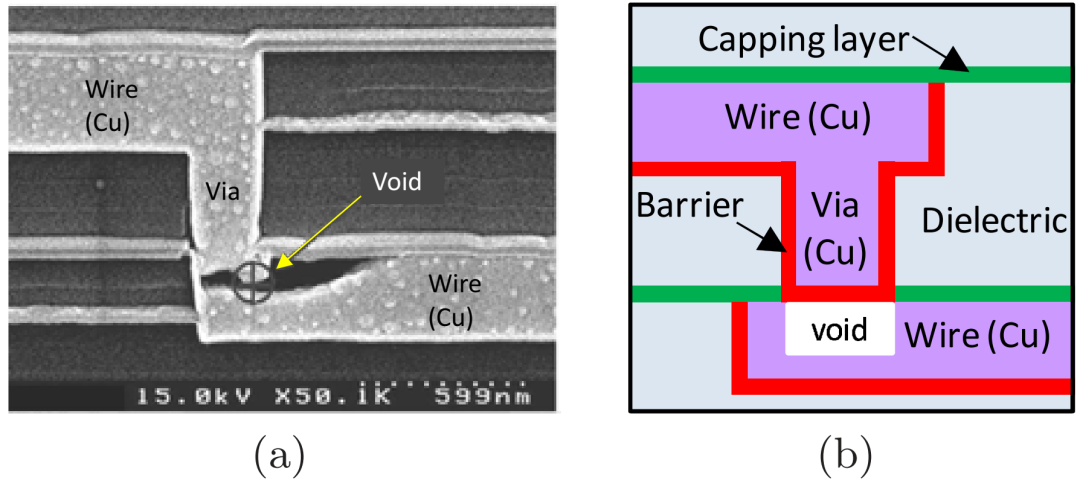

通孔是先进 IC 设计的关键结构,它通过垂直连接层来帮助扩展设计空间。尽管通孔在电路设计中很重要,但通常被认为是工艺和可靠性问题的主要来源之一,这些问题可能会降低电路性能,甚至可能使电路失效 [4]。通孔可靠性问题的一个主要来源是电迁移 (EM),即由电子电流引起的金属原子扩散。随着 IC 技术的进步,电流密度会因横截面通孔面积的减少而增加,这会增加故障发生概率。高温和通孔周围的机械应力甚至会进一步增加 EM 故障概率。对于 EM,通孔和金属线的界面是 EM 的最薄弱环节之一。我们可以在图 5中通过局部通孔和导线的 SEM 图像看到这种现象 [5]。

图5. 电迁移导致的通孔损坏SEM图以及对照示意图[5]。

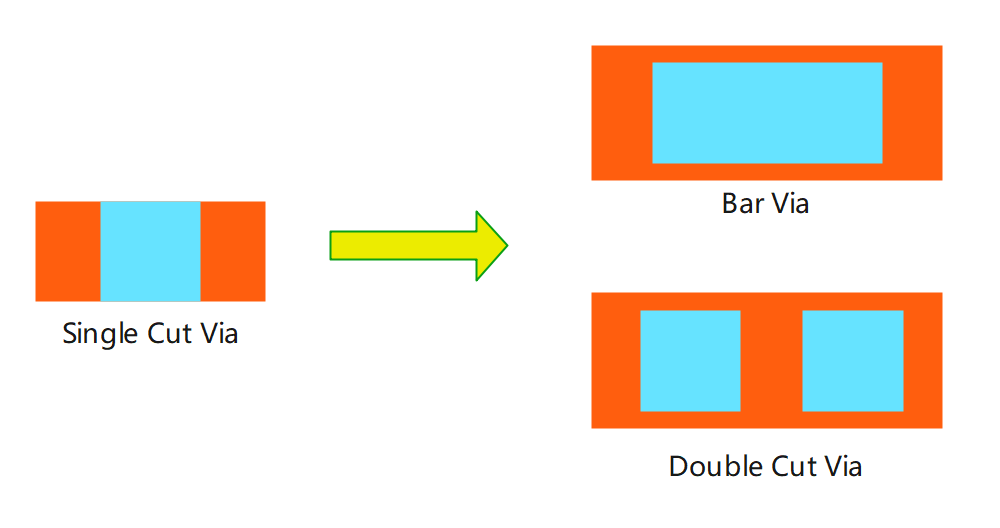

通孔按照形状可分为正方形(square)和长方形(bar)通孔;按照数量可分为单孔(single)和双孔(double)。如图6所示,通孔冗余设计即将方孔替换成面积更大的长方形孔,或者将单孔替换成双孔。通孔冗余设计能减小开路的可能性,减小电阻与电位差,增加抗应力迁移能力,进而改善故障发生概率。

除此以外,我们也可以通过NDR(non-default routing rule,非默认绕线规则)的绕线方式加强布线网络,增强金属线抗干扰能力。NDR绕线指的是在绕线的时候给某些net制定的特殊的绕线规则。现在工具在绕线之前需要制定一个默认规则(default rule),默认所有net都按default rule来绕。而对于指定了NDR的net,EDA工具就会区别对待指定的net。因为NDR的rule和default rule有所区别,绕线的最终结果就会有所不同,相应的也会影响芯片的各项性能。一般来说,使用NDR方式绕线方式(如double width double spacing)能保持更好的信号完整性,但也会占用更多的绕线资源。

图6. 通孔冗余设计示意图。

3.2冗余寄存器物理隔离

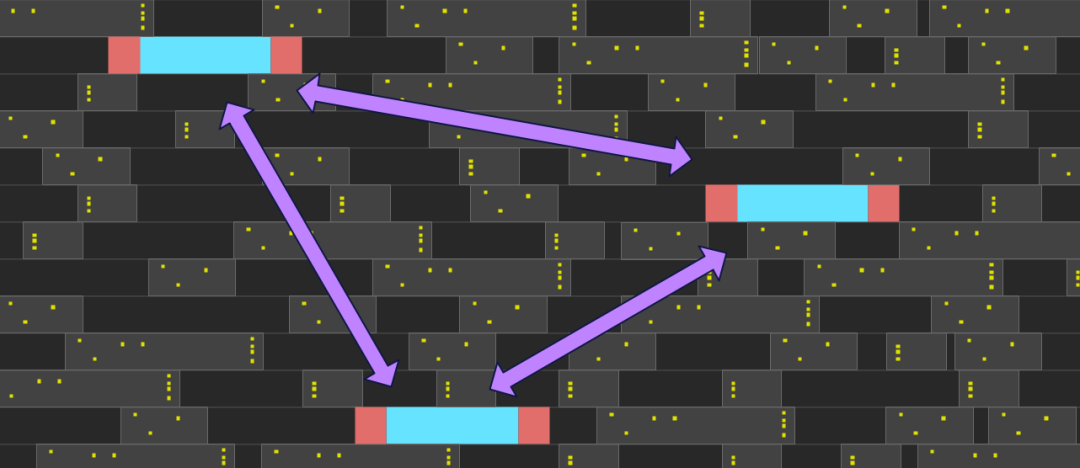

上文中提到了可以通过寄存器的三重模块冗余的方式实现功能安全性能的提升,实际上就是将寄存器复制两份。如果这三个寄存器间距很近,局部的干扰可能会对这三个寄存器中的两个甚至三个产生同样的错误,经过投票机制后仍会导致错误的结果。为了尽可能的降低这种风险,在物理实现中,刻意地将冗余寄存器的位置在横纵方向上进行分离操作将会有助于改善这种风险,如图7所示。我们在物理实现过程中还会使用物理单元(tap cell)将各个寄存器保护起来,以免受到周围其他单元的影响和防止闩锁效应,如图中红色方块所示。为了避免来自时钟树和复位树中存在的共同干扰,可以采取分开生长各个寄存器的时钟树和复位树,减少寄存器之间共同的路径。

图7. TMR寄存器物理隔离示意图。

3.3双核锁步物理隔离与绕线约束

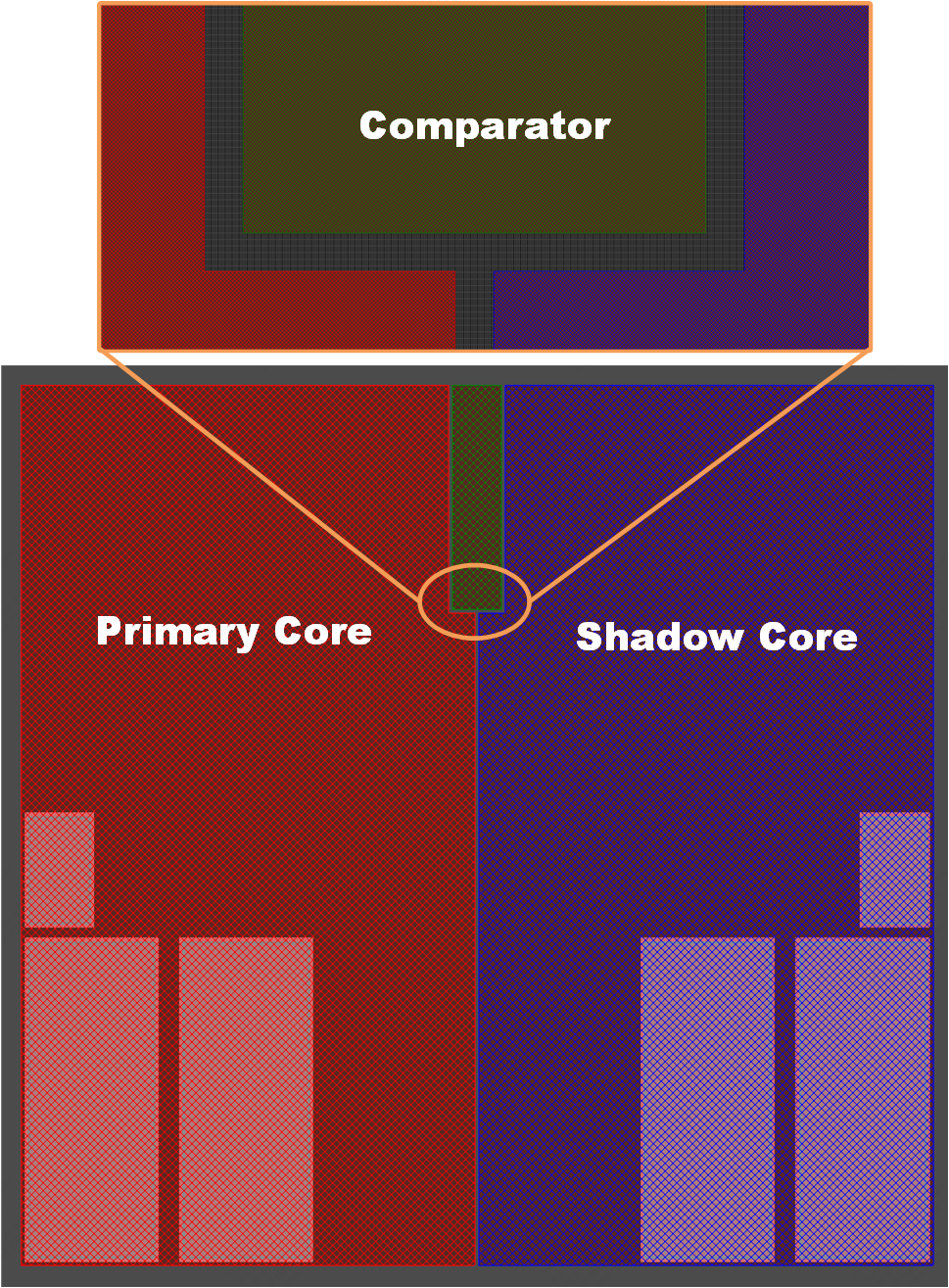

类似地,双核冗余也需要分隔一定距离。如果不考虑功能安全,后端工具会自动根据线长、时序、拥塞和功耗来确定标准单元的位置,因此会打散双核中标准单元的摆放。为了降低双核同时遭遇随机错误的几率,在物理布局布线时,我们首先要规划两个核的“安全区域”使其彼此排斥。如图8所示,双核锁步中的主核(Primary Core)与冗余核(Shadow Core)需要分组实现,并在两个类似镜像的“安全区域”之中各自布局和布线。时钟树综合中,主核和冗余核的时钟树要彼此分离,避免共用时钟路径和时钟缓冲器。同时,还要设置时钟树绕线障碍,防止一个核的时钟线在另一个核的区域里经过或者穿越,确保主核与冗余核的时钟线互相保持一定的距离。数据的对比/校验逻辑是在Comparator中完成的,避免两个隔离核之间有数据的直接交互,在每一个时钟周期对双核的输出进行比较,在发生故障时输出错误标识信号,以供系统及时采取应对措施。

图8. DCLS物理布局布线示意图。

4.结语

随着汽车电子系统功能安全要求的不断提升,对车规芯片安全性的需求也在不断加强,符合功能安全要求已然成为了车规芯片进入市场的必需要求。汽车自动驾驶技术的发展带来的汽车电子复杂度的提升,先进制造工艺带来的晶体管密度的提升,都对芯片的功能安全提出了更高的要求。如何设计生产出国产高安全可靠的车规芯片,需要工程师们对技术难关进行不断攻克并总结经验。

reference:

1.International Organization for Standardization, “ISO 26262-1:2018 – Road Vehicles – Functional Safety”:https://www.iso.org/standard/68383.html

2.ABLIC Inc. "Introduction – What is Functional Safety?":https://www.ablic.com/en/semicon/products/automotive/asil/

3.HEICON Global Engineering GmbH, "ISO 26262 Freedom from interference – What is that?":https://heicon-ulm.de/en/iso26262-freedom-from-interference-what-is-that/

4.Zhou, Han, Liang Chen, and Sheldon X-D. Tan. "Robust power grid network design considering EM aging effects for multi-segment wires." Integration 77 (2021): 38-47.

5.Pak, Jiwoo, Bei Yu, and David Z. Pan. "Electromigration-aware redundant via insertion." In The 20th Asia and South Pacific Design Automation Conference, pp. 544-549. IEEE, 2015.

关于复睿微

复睿微电子植根于创新驱动的文化,通过技术创新改变人们的生活、工作、学习和娱乐方式。公司成立于2022年1月,目标成为世界领先的智能出行时代的大算力方案提供商,致力于为汽车电子、人工智能、通用计算等领域提供以高性能芯片为基础的解决方案。目前主要从事汽车智能座舱、ADS/ADAS芯片研发,以领先的芯片设计能力和人工智能算法,通过底层技术赋能,推动汽车产业的创新发展,提升人们的出行体验。复睿微电子拥有一支业内顶级,能够全流程覆盖芯片的研发设计、解决方案、市场销售、服务支持等完整架构的车规级大算力芯片团队。团队集聚全球顶尖数字芯片人才,核心成员拥有在海内外领先的优秀企业的工作经验。