近日,深圳大学材料学院刘新科研究员团队做出了自支撑GaN衬底上的高性能常关型PGaN栅极HEMT,用AlN截止层和SF6基刻蚀气体做到了自终止刻蚀技术。对比Si基HEMT,GaN on GaN HEMT电流密度更高,低亚阈值摆幅更低,漏电流更低,静态和动态电阻更低,因为同质外延有更低的位错和缺陷。同时,本次工作还测试了175℃高温下Vth的稳定性和均匀性。对比Si基HEMT 507V的击穿电压,GaN on GaN HEMT击穿电压可以达到683V,自支撑GaN衬底上的常关型AlGaN/GaN HEMT在功率器件应用上展示出很大的潜力。

H.-C. Wang et. al., “High performance normally-off operation p-GaN gate HETM on free-standing GaN substrate,”IEEE Transactions on Electron Devices, vol. 69, no. 9, pp.4859-4863, 2022

介绍

实验

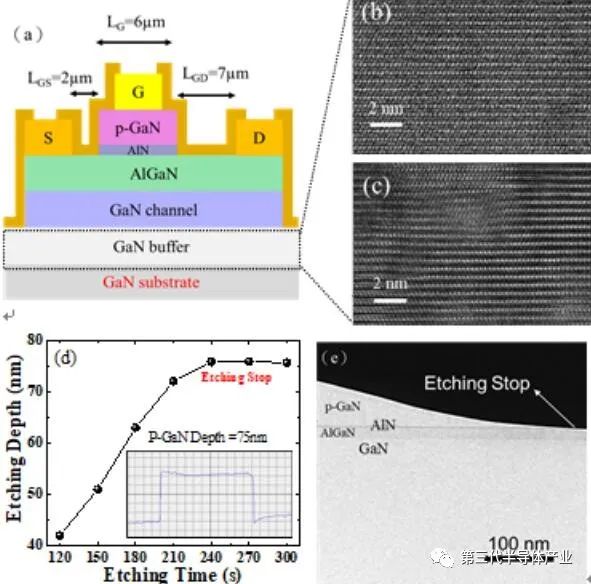

器件结构示意图如图1a所示。采用氢化物气相外延法(HVPE)生长了厚度为350 μ m、取向为(0001)的2英寸半绝缘掺铁独立GaN基板。镓和氮源分别为HCl/金属镓和氨气,N2/H2混合物为载气。生长速率通常在150 μ m/h左右。螺纹错位密度小于106 cm-2由零售商提供。本实验采用化学机械抛光(CMP)后,采用金属有机化学气相沉积(MOCVD)生长法向关闭外延结构。从下到上,外延结构由GaN缓冲层、含有12 nm Al0.23Ga0.77N势垒层和300 nm未掺杂GaN通道层的异质结和75 nm Mg掺杂浓度为2×1019 cm-3的p型GaN层组成,以实现常关工作。同时,将1.5 nm和1 nm的AlN分别作为蚀刻停止层和间隔层插入p-GaN/AlGaN和AlGaN/GaN的界面。外延层生长完成后,在MOCVD室中进行原位Mg活化过程,温度为720℃,在N2环境中持续10分钟。霍尔测量得到孔浓度为1×1018 cm-3。利用透射电子显微镜(TEM)对GaN衬底外延堆的晶体质量进行了表征。由于GaN衬底位错密度较低,缓冲层的晶体质量较好,如图1b所示,这说明GaN-on-GaN比GaN-on- si能获得更高的外延质量(图1c)。

图1所示。器件的截面图(a)和GaN (b)和Si衬底上GaN缓冲层的TEM图像(c)。P-GaN刻蚀深度随刻蚀时间的函数(d)和刻蚀停止食谱的TEM图像(e)。插入件为刻蚀过程后的刻蚀深度。相应的尺寸也有标记。

常规剥离GaN-HEMT的制备基于标准光刻和剥离技术,从电感耦合等离子体(ICP)干法刻蚀的台面隔离开始。然后,使用Cl2/BCl3/SF6混合蚀刻气体,通过ICP干法蚀刻去除接触区p-GaN层。自终止过程发生,这归因于sf6基蚀刻气体与上面的1.5 nm AlN反应形成的AlF3蚀刻停止层[24]。通过延长ICP刻蚀时间,研究了刻蚀停止配方的公差。如图1c所示,在240 s时,刻蚀深度达到75 nm,说明此时p-GaN层被移除。当刻蚀时间达到300 s时,刻蚀深度仍为75 nm,如图1d所示。图1e中去除p-GaN步骤后器件的TEM照片也表明,这种自端技术可以有效地保护AlGaN阻挡层免受过多或较少的蚀刻误差。

经H2SO4:H2O2=4:1 (SPM)和稀释的HCl溶液清洗后,采用电子束蒸发法制备了Ti/Al/Ni/Au (25/120/25/150 nm)金属叠加欧姆电极。欧姆接触是通过在N2环境下,在875℃退火30s获得的。最后,采用Ni/Au (25/120 nm)栅金属层,沉积100 nm的SiO2作为钝化层。GaN-HEMT的器件几何结构由指型栅(Wg为100 μm, Lg为6 μm)、指型栅(Lgs为2 μm, Lgd为7 μm)组成。在长度为6 μm的栅极区域上,栅极金属长度为5 μm。p-GaN的边缘与栅金属边缘之间有0.5 μm的空白。为了进行比较,还提出了具有相同外延层和制作工艺的法向关闭Si-HEMT。GaN和Si-HEMT的片电阻分别为571和628 Ω/□,对应的接触欧姆电阻分别为8.1×10?6和9.6×10?6 Ω·cm2,转移长度法(TLM)提取。

结果与讨论

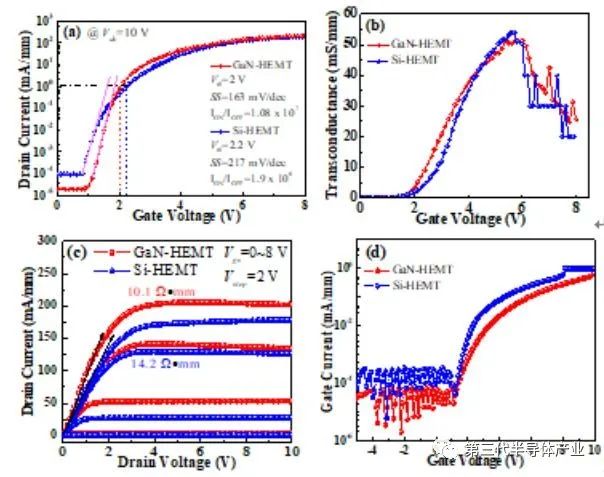

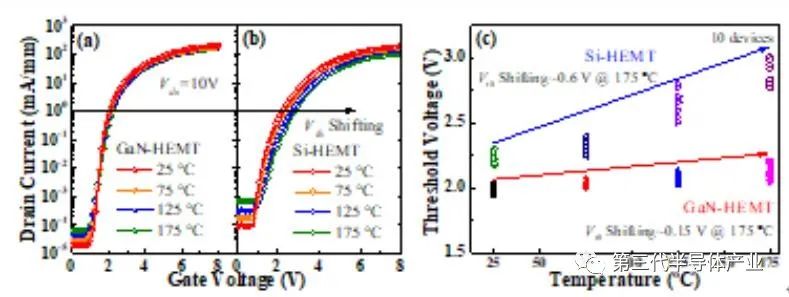

半测井传递特征如图2a所示。GaN-HEMT和Si-HEMT的阈值电压(Vth定义为Id=1 mA/mm)分别为2和2.2 V,其次是163 mV/dec和217 mV/dec的次阈值波动(SS)。与此同时,GaN-HEMT的开/关比为1.08×107,高于Si-HEMT的1.9×106。Si-HEMT较大的Vth可能与低开/关比和高SS有关。Si-HEMT低开/关比是由于位错导致的相对较高的脱态漏漏电流。即使研究了许多技术来提高Si衬底上的外延质量,仍然存在大量的位错,这通常是工作时泄漏电流的路径。因此,推荐在GaN基板上均匀外延生长。

图2所示。GaN和Si-HEMT在Vds为10v时的传输特性(a)、跨导曲线(b)、输出特性(c)和对数坐标(d)下的栅极电流-电压特性的半对数图

此外,两种器件的跨导曲线和最大值相似,如图2b所示。当GaN和Si-HEMT的栅电压(Vg)从0扫至8 V时,器件的输出I-V特性如图2c所示。具有良好的掐断特性,无明显的迟滞现象。GaN和Si-HEMT的最大电流密度在206和185 mA/mm左右,这决定了GaN- hemt的开态电阻值为10.1 Ω?mm,而Si-HEMT的开态电阻值为14.2 Ω?mm。通态电阻由欧姆电极的接触电阻和通道电阻(包括接入区和栅区)组成。因此,由于接触电阻可以忽略,通道电阻贡献了主要部分。此外,两个器件具有相似的二维电子气(2DEG)浓度,这是由相同的外延结构产生的。因此,与Si-HEMT相比,GaN-HEMT的低通态电阻主要是由于均匀外延生长的优势使缺陷密度更小,从而产生了更高的电子迁移率。另一方面,两种hemt的栅漏电流也如图2d所示。结果表明,GaN-HEMT在正向和反向偏置区域均具有较低的栅漏电流,且相对于Si-HEMT具有较大的栅摆幅。对于Si-HEMT,栅极击穿发生在Vg约为8 V时,而GaN-HEMT即使在10 V时也不会击穿。

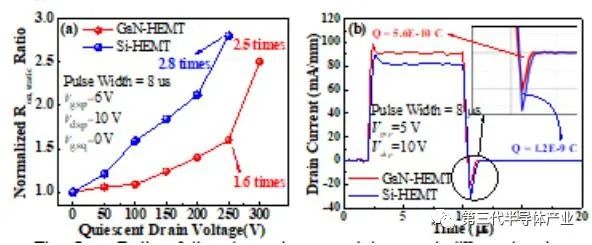

用脉冲Id-Vds测量了两种HEMTs的动态性能,包括动态通阻和反向恢复行为。图3a给出了不同静漏偏置点下快速开关动态通阻与静态通阻之比(Ron,动态/Ron,静态)。实验条件为脉冲电压(Vgsp, Vdsp)为(6,10),静止电压(Vgsq, Vdsq)为(0,0)~(0,300),脉冲宽度为8 μs,周期为200 μs。通常情况下,当在器件上施加高的静止漏极电压时,二维电子气(2DEG)通道中的部分电子会外溢并被位于外延层的缺陷捕获,这是由于外延生长过程中的位错造成的。这可能会导致2℃浓度的降低,从而导致在快速开关开关设备时,高的接通电阻和低的电流密度(电流崩坏现象)。如图3a所示,GaN-HEMT的Ron,动力在100v以下有缓慢的增加,比值曲线的斜率在100v到250v之间有一点上升。然而,GaN-HEMT仍然表现出相当低的Ron的1.6倍,静态相对于Si-HEMT的2.8倍,在250 V的静漏电压下。GaN-HEMT优良的动态通电阻主要是由于缺陷捕获的电子较少,从而抑制了电流塌缩。这说明GaN的同质外延结构可以提高外延质量,同时大幅度降低缺陷捕获电子的大小。但GaN-HEMT的Ron,动态在300v时急剧升高,表明GaN-HEMT的有效钝化和最佳生长条件有待进一步研究。

图3所示。GaN和Si-HEMT在不同静漏偏置点的动态通阻比(a)和动态恢复行为(b)。

另一方面,当脉冲电压(Vgsp, Vdsp)为(5,10),脉宽为8 μs时,动态恢复行为如图3b所示。尽管GaN-HEMT具有较高的漏极电流密度,但反向电流密度较低,恢复时间较短,这是由于GaN-HEMT具有如图3b所示的低存储电荷。储能效应主要由截留载波在关断时刻放电产生,并导致反向恢复电流。由于缓冲层和衬底作为捕获中心的外延缺陷较少,gan - hemt具有较好的反向性能。这也是Si-HEMT反向性能较差的原因。

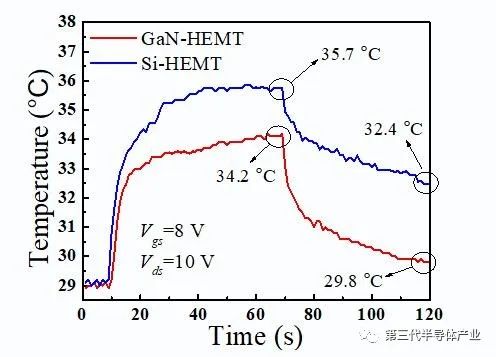

为了研究器件的散热性能,采用微拉曼光谱红外热像仪对器件的温度进行了测量。测量过程是先在8 V Vgs和10 V Vds下工作60 s,然后冷却50 s。热导率随时间变化的曲线如图4所示。当进行该装置时,栅极区域的温度迅速上升到一个较高的水平。随着操作时间的延长,温度继续呈梯度上升。GaN和Si-HEMT的最高温度分别为34.2和35.7℃,其中GaN- hemt的低温度部分归因于低通电阻。冷却50 s后,GaN-HEMT的栅极温度降至29.8℃。相反,Si-HEMT的积热去除缓慢,50 s后达到34.2℃。显然,与Si- hemt相比,GaN- hemt具有更好的散热性能,尽管Si和GaN的导热系数相近[21]。主要原因是两种材料的界面处普遍存在较大的热边界阻力,导致热不能立即传导[25]。因此,GaN基板上的均匀生长有利于GaN电源器件的热管理。

图4所示。热导率曲线随时间变化,设备运行60 s,冷却50 s。

为了研究GaN和Si-HEMT的热稳定性,我们测量了从室温(25℃)到175℃的传递特性,步长为50℃(图5a和b)。对于具有明显v值漂移的Si-HEMT, GaN- hemt的传递曲线几乎重合。为了更通用,在两个晶片中随机选择10个器件进行测量并计算平均第v移值。GaN-HEMT表现出良好的稳定性,第V位移约为0.15 V至175℃,而Si-HEMT的第V位移为0.6 V(图5c和d)。

图5所示。25 ~ 175℃(a)和(b)的传递特性的半对数和Vth稳定性取决于温度(c)。

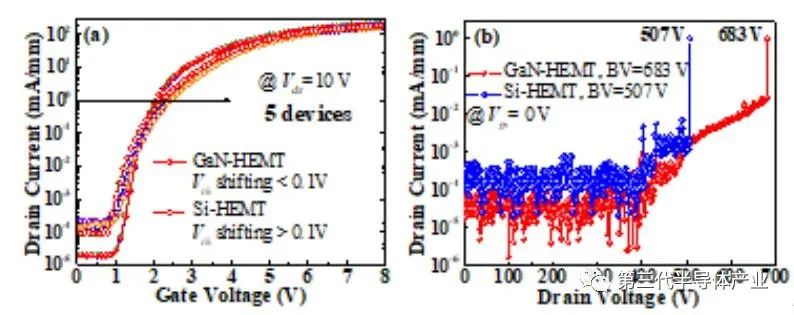

在漏极电压为10 V时,研究了图6a中5个器件的Vth均匀性。GaN-HEMT的离态泄漏电流较低,为10- 5ma /mm,第V次位移小于0.1 V,均优于Si-HEMT。然后,测量脱态击穿电压,Vgs为0v, Vds从0扫至图6b所示的击穿电压。GaN和Si-HEMT的击穿电压分别为683和507 V,这是由漏极电流达到1 mA/mm定义的。同时GaN-HEMT具有较低的漏电流。这说明GaN-HEMT比Si-HEMT具有更好的离态性能。对于动态通阻测量,关闭装置并采用高漏压。该偏压条件与击穿测量的偏压条件相似,但漏极电压远小于器件的击穿电压。对于第二阶段,用相对较小的漏极电压打开器件,以计算通阻。通常,动态电阻问题是由晶体缺陷在阻挡层和缓冲层中的电子俘获效应引起的。当来自2DEG通道的电子在脱态时被缺陷捕获,导通能力降低,导致通阻增加。较高的缺陷密度可能与更严重的动态电阻问题有关。另一方面,这些缺陷也会在器件中提供漏电通路,影响击穿电压。由以上讨论可知,动态导通电阻和击穿电压都与晶体质量有一定的关系。

图6所示。GaN和Si-HEMT的Vth均匀性(a)和脱态击穿电压(b)。

为了进一步提高离态击穿性能,首选采用场板(FP)终端设计。FP作为一种相对简单的边缘终端,广泛应用于gan基器件中,用于缓解漏侧栅边电场拥挤。因此,结合FP终端和独立的GaN衬底,该e型器件的性能将是值得研究的。

总结

综上所述,深圳大学刘新科研究员团队在独立的GaN基板上制备了具有p-GaN栅极的常关AlGaN/GaN高电子迁移率晶体管(HEMT)。为了去除p-GaN,同时减小蚀刻误差,采用sf6基蚀刻气体自端蚀刻技术。GaN- hemt在GaN基板上具有良好的外延性能,表现出比Si-HEMT更先进的电学性能,包括更高的电流密度、更低的亚阈值摆动(SS)、更低的动态通电阻以及更好的Vth稳定性和均匀性。同时,由于同质性GaN-HEMT具有良好的生长、良好的散热和较高的击穿电压(BV),这是由于低的位错和缺陷。因此,GaN-HEMT具有优异的电性能和热性能,在电力应用领域显示出巨大的潜力。

简介

刘新科

深圳大学微电子研究院院长助理

深圳大学材料学院研究员

刘新科博士,深圳大学微电子研究院院长助理、材料学院研究员,新加坡国立大学访问教授,广东省杰出青年基金项目获得者。长期从事宽禁带氮化镓以及氮化镓异质结的半导体器件研究,在Adv. Mater., Adv.Funct.Mater., Adv. Electron. Mater. IEEE EDL, IEEE TED,APL等知名期刊发表第一或通信作者SCI收录论文93篇,申请专利50项,授权专利12项(含3项PCT和1项美国专利), 科研成果被Semiconductor Today,MaterialsviewChina多次报道,科研成果被Photonic Research 和Advanced Electronic Materials选为封面文章。目前承担国家科技部重点研发计划课题和任务各一项、国家自然科学青年和面上科学基金各一项、广东省科技计划项目一项、广东省重点研发计划课题三项,深圳市基础研究布局一项、深圳市技术攻关一项等10多项科研项目。

来源:第三代半导体产业网

后台留言:【获取原文:High performance normally-off operation p-GaN gate HETM on free-standing GaN substrate】

加速芯片国产化的进程刻不容缓!基于此,2022年11月15-17日,由DT新材料主办的第六届国际碳材料大会暨产业展览会,针对半导体产业链设置了碳化硅半导体论坛、金刚石前沿论坛、极端制造与超精密加工论坛,围绕半导体晶体材料制备、晶圆衬底加工、外延、封装热管理等技术以及高功率器件、量子技术等前沿话题展开话题讨论,探索第三代半导体应用的无限可能,加速推进芯片国产化!

碳化硅半导体论坛 |

金刚石前沿论坛 极端制造与超精密加工论坛 |

部分展商风采

免责声明 | 部分素材源自网络,版权归原作者所有。如涉侵权,请联系我们处理