在全球范围内,FPGA行业的主要市场份额常年被赛灵思(已被AMD收购)和英特尔两家公司牢牢掌握。随着时间的积累,这两家公司逐渐构建起一道由上万件核心技术专利组成的“护城河”,而这条护城河也成功阻止了很多FPGA公司进一步发展的脚步。一些存活下来的公司,比如Lattice和Microsemi,往往只能靠剑走偏锋,专攻低功耗、航空航天等特殊的应用领域。

然而,在三年前,一家名为Achronix的公司发布了一款名为Speedster7t的7纳米工艺的FPGA系列产品,引起了很多业内人士及开发者的注意。该款FPGA主打高速网络传输、机器学习加速等领域。

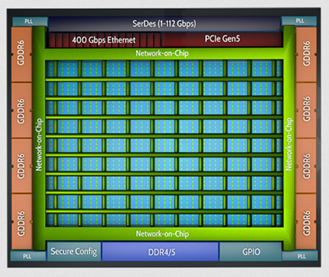

Speedster7t FPGA是第一个也是当前唯一支持GDDR6高带宽存储器的FPGA。它基于台积电7nm FinFET工艺,具有革命性的新型二维片上网络(2D NoC)和大量的超高带宽接口,包括400G以太网端口,PCIe5 以及业界内最灵活,低成本,高带宽存储的GDDR6控制器。

Speedster7t FPGA 直播课推荐(免费)

为了让大家更好地了解Speedster7t ,以及该款FPGA在超高带宽上的优势,9月22日,EETOP联合Achronix将为为大家做一期精彩FPGA直播。本期培训课程,我们将重点分享和探讨以下知识点:

Speedster7t FPGA 架构

2D NoC的架构以及2D NoC给FPGA设计所带来的优势

400G以太网在FPGA上的实现

正文

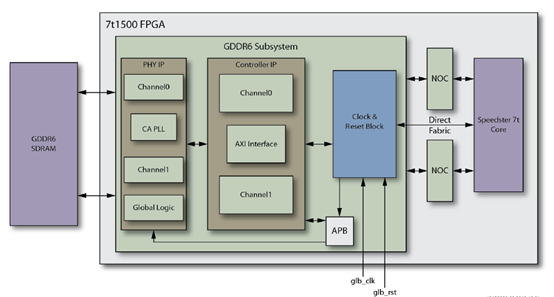

Achronix Speedster7t GDDR6子系统包括GDDR6 PHY和GDDR6控制器,全部采用了硬核设计。整个子系统包括GDDR6 PHY IP、GDDR6控制器IP、时钟和复位模块,APB接口和AXI4用户接口可以连接到二维片上网络(2D NoC)或者内部编程逻辑,如图2所示。

图2 Speedster7t GDDR6子系统框图

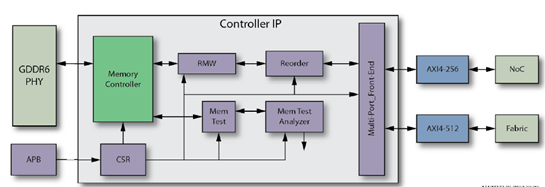

GDDR6控制器IP支持两个通道,每个通道为16bit位宽。两个通道独立访问不同的GDDR6空间。控制器的用户接口为标准的AXI协议,可以连接到二维片上网络上或者直接连到内部的可编程逻辑。在另外一边,控制器和PHY的接口为DFI4.0接口。

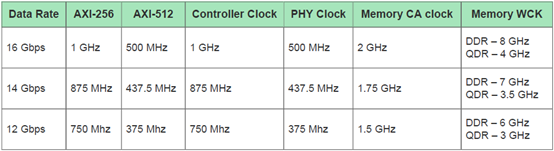

表1 GDDR6支持的时钟频率模式

PHY IP用来连接器件外围的高速GDDR6颗粒,它会像其他DRAM PHY一样产生PRECHARGE、ACTIVE和REFRESH等命令。

APB全称Advanced Peripheral Bus,字面上是先进外围总线的意思,该总线协议是ARM公司提出的AMBA总线结构之一,已成为一种标准的片上总线结构。APB总线接口工作在250MHz,用来配置GDDR6子系统的寄存器,Speedster7t FPGA的配置电路FCU可以在启动的时候通过APB总线接口配置GDDR6子系统的寄存器,用户逻辑模块也可以在FPGA运行的时候通过APB总线接口动态配置GDDR6子系统的寄存器。

MPFE模块是前端多端口模块,Speedster7t上的GDDR6控制器为每个通道提供了两个MPFE端口,它们支持AXI4协议,每个端口能够提供最大256Gbps的带宽;其中一个AXI端口用于连接到二维片上网络上,位宽为256位,时钟是1GHz。另一个AXI端口用于直接连接到FPGA内部的可编程逻辑资源,位宽为512位,时钟是500MHz。

图3 Speedster7t GDDR6控制器框图

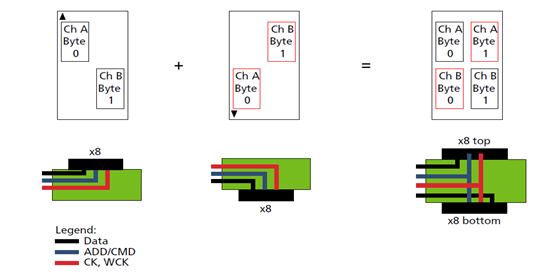

GDDR6控制器支持两种模式,正常x16模式和Clamshell x8模式。在x16模式下,控制器提供了每通道16位的双通道接口,可以连接一个GDDR6颗粒。在Clamshell x8模式下,如图4所示,控制器提供了每通道8位的双通道接口,可以连接两个GDDR6颗粒。Clamshell模式提供了一种在不改变控制器带宽的情况下,通过在两个GDDR6颗粒间share地址和命令总线将容量加倍的一种方法。

图4 GDDR6 Clamshell模式

1、Micron 8Gb/16Gb GDDR6 Product Brief

2、Achronix网站:www.achronix.com

作者:黄仑,Achronix资深应用工程师