本文对雷达及其硬件系统组成发展趋势进行了概述,阐述微组装技术是高集成度射频前端研制的关键技术,详细论述了微组装技术类型和微组装工序,最后对射频前端微组装的发展趋势进行了展望。

随着半导体制造技术的快速发展,以及后摩尔定律的芯片制造工艺的出现,以片上系统(SoC)和系统级封装(SiP)等技术为基础的电子系统正朝着高密集成、高功率密度、高使用频带、多功能等方向快速发展。作为复杂电子系统的雷达,体制、系统架构等方面也随着技术发展和作战需求的变化,向着二维有源相控阵方向发展。

01

微组装技术类型

射频组件微组装技术(Microcircuit

Packaging Technology,MPT)是将MMIC、HMIC、ASIC等集成电路裸芯片、薄/厚膜混合电路、微小型表面贴装元器件等进行高密度地安装和互连,构成高密度、高速度/高频率、高可靠性、小型化、多功能模块化电子产品。目前高密度射频前端的装配均采用了微组装技术。微组装技术根据装配维度可分为平面微组装技术和3D微组装技术。

1.1平面微组装技术

平面微组装技术多用于对散热量大、需控制成本的小型化射频前端设计制造。平面微组装是指利用微组装技术在二维平面进行装配,将多个裸芯片,电阻、电容等元器件高密度地安装并互连在多层布线PCB、厚膜多层陶瓷基板或薄膜多层基板上,整体封装起来。

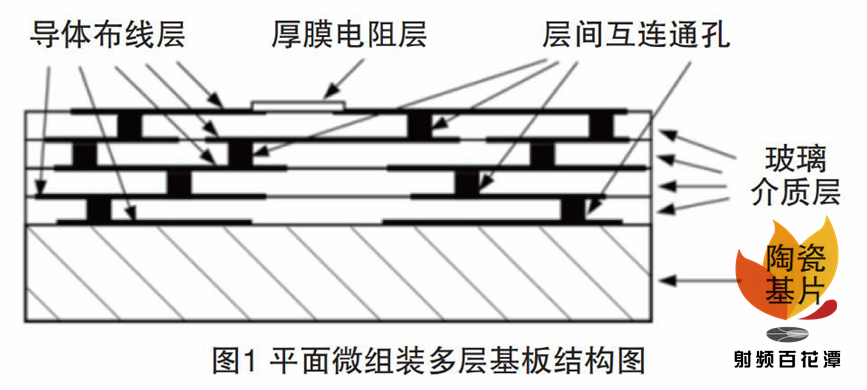

平面微组装其特点是基板内部无元器件各类元器件均安装于基板表面,多层基板内部印刷或刻蚀用于互连的连线通过通孔与表面元器件相连以实现元器件的连接,其结构如图1所示。

1.2 3D微组装技术

3D微组装技术多用于对体积要求较为苛刻的射频前端设计制造。3D微组装技术相对于平面微组装技术,其在Z轴进行元器件或基板的堆叠装配,从而具有更高的装配密度。典型的3D微组装形式有埋置型、有源基板型和堆叠型三种类型。

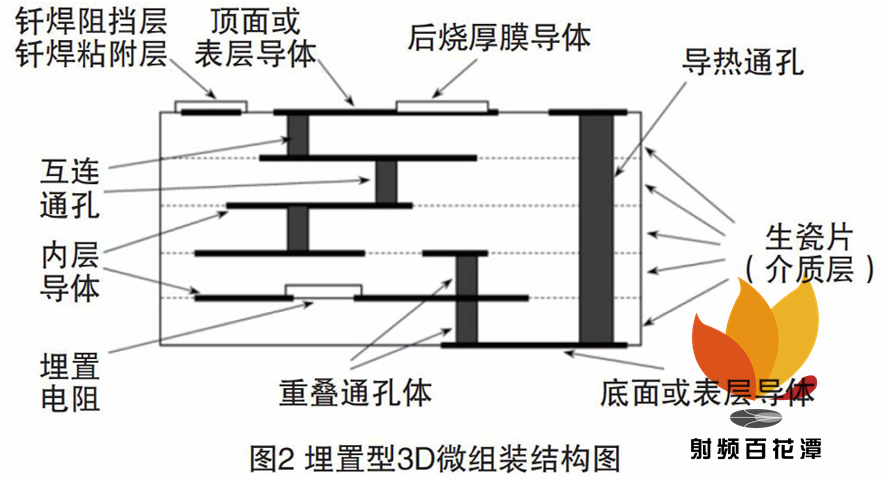

埋置型3D结构作为后布线的芯片互连技术,减少焊点,提高电子产品可靠性的电子封装技术。其可分为基板开槽埋置型和多层布线介质埋置型,在混合集成电路的多层布线中埋置R、C元件已经普遍,其结构如图2所示。

在有源Si基板再多层布线,上面再安装多芯片,就可形成有源基板型3D微组装,从而以立体封装形式达到了WSI(Wafer Scale Integration晶圆规模集成)所能实现的功能。它的主要优点,一是工艺与一般半导体IC工艺相同,从而可实现大规模工业化生产;二是Si基板与其上面安装的芯片能达到应力完全匹配,从而使电子产品有更高的可靠性。

堆叠型3D,是将芯片、MCM或WSI无间隙的层层叠装而成。最常见的裸芯片堆叠3D封装是先将生长好凸点的芯片倒扣焊接在薄膜载体上,这种薄膜载体的材质为陶瓷或环氧玻璃,上面有导体布线,内部互连焊点,两侧有外部互连焊点,再把多个薄膜载体叠装互连。图3为典型堆叠型3D微组装结构图,POP的两层器件之间通过焊接方式连接,省去了中间的引线,实现整体封装体积不变的情况下增加封装密度。

02

微组装工序

2.1前道工序

前道工序主要为材料制备和基板制造,其中基板制造的技术主要分为厚膜技术(丝网印刷、烧结等)和薄膜技术(镀膜、光刻、刻蚀等),根据相应技术制作出的基板分别称为厚膜基板、薄膜基板和混合基板,低温共烧陶瓷(LTCC)基板是近年来在高集成度射频前端中大量应用的基板。

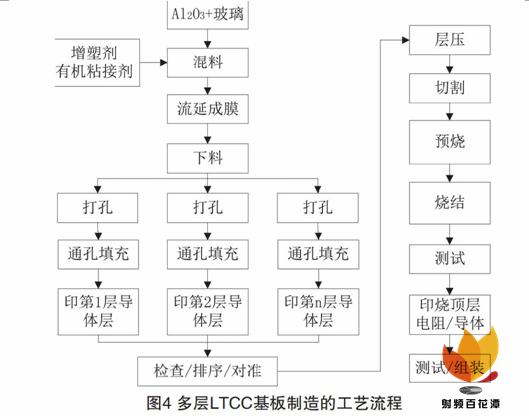

LTCC基板是利用陶瓷材料和厚膜集成工艺制成的基板,在多层LTCC基板内部可埋置无源元件、控制信号线、电源线等,图4是多层LTCC基板制造的工艺流程,主要有流延、单板处理、层压、烧结等。

2.2后道工序

后道工序主要进行元器件与基板等的电气互连与装备,包括元器件焊接、清洗、壳体密封等工艺。典型微组装后道工序工艺流程图如图5所示,微组装工艺按照温度从高逐步到低进行操作,对不同元器件根据要求不同需采用不同装配工艺,如散热要求高的芯片进行焊接时采用共晶焊接,散热要求低的采用导电胶进行粘结,一般按照共晶焊、粘结、键合、密封的次序,当进行共晶焊等有助焊剂或残留物等工艺处理后应进行清洗,每一种工艺完成后应进行相应的检验。

03

结语

射频前端是雷达整机企业生存的支撑点,相控阵雷达射频前端通道数量多,二维相控阵雷达射频前端的通道数量少则数千,多则上万甚至數十万,在雷达研制的成本中占比达到50%以上。目前大部分高集成度射频前端还是采用的平面微组装技术,随着3D微组装技术的日渐成熟,高密度组装散热技术难点的突破,射频前端的体积会更进一步缩小。

作者:涂中华 程浩然 王伟

声明:

投稿/招聘/推广/宣传 请加微信:15989459034