01.

02.

03.

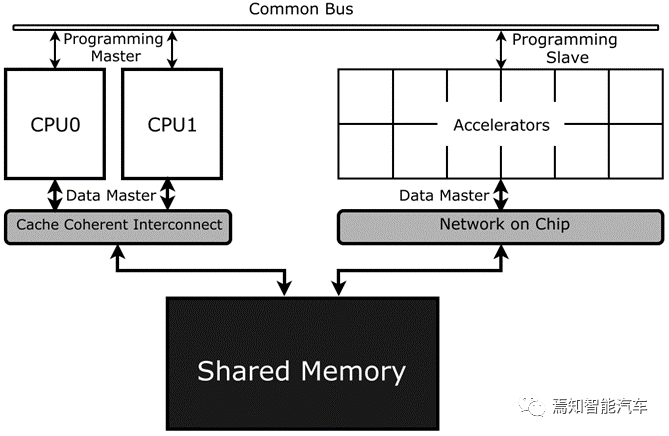

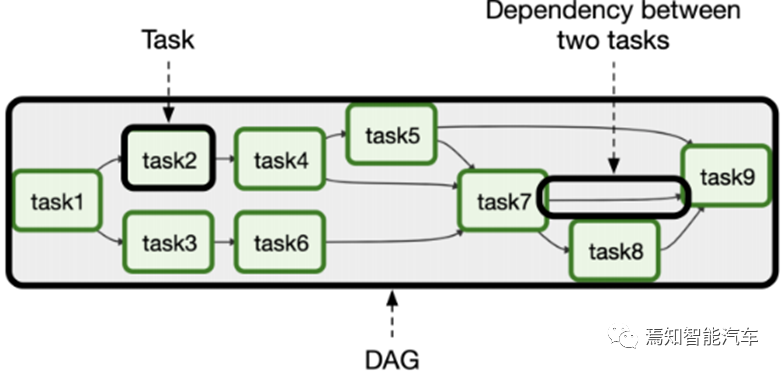

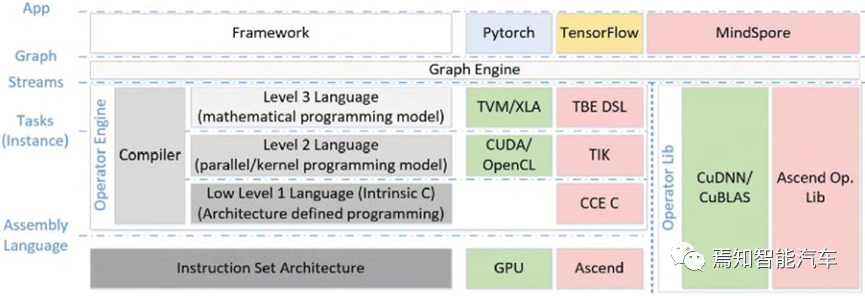

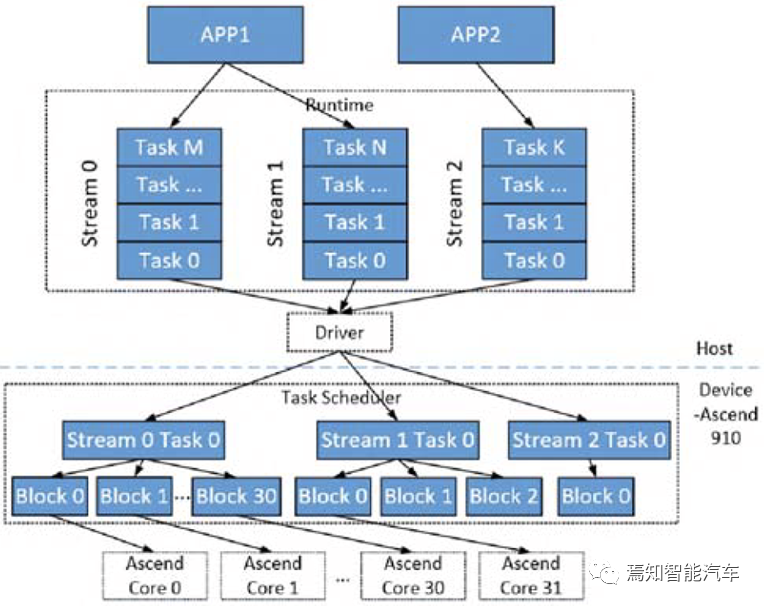

Figure 14. Ascend调度层级

1.ZERO, IN PURSUIT OF VISION. "Euro NCAP 2025 Roadmap." (2017).

2.Yamada, Yutaka, et al. "A 20.5 tops multicore soc with dnn accelerator and image signal processor for automotive applications." IEEE Journal of Solid-State Circuits55.1 (2019): 120-132.

3.Krizhevsky, Alex, Ilya Sutskever, and Geoffrey E. Hinton. "Imagenet classification with deep convolutional neural networks." Advances in neural information processing systems 25 (2012).

4.Simonyan, Karen, and Andrew Zisserman. "Very deep convolutional networks for large-scale image recognition." arXiv preprint arXiv:1409.1556 (2014).

5.Girshick, Ross, et al. "Rich feature hierarchies for accurate object detection and semantic segmentation." Proceedings of the IEEE conference on computer vision and pattern recognition. 2014.

6.Long, Jonathan, Evan Shelhamer, and Trevor Darrell. "Fully convolutional networks for semantic segmentation." Proceedings of the IEEE conference on computer vision and pattern recognition. 2015.

7.He, Kaiming, et al. "Deep residual learning for image recognition."Proceedings of the IEEE conference on computer vision and pattern recognition. 2016.

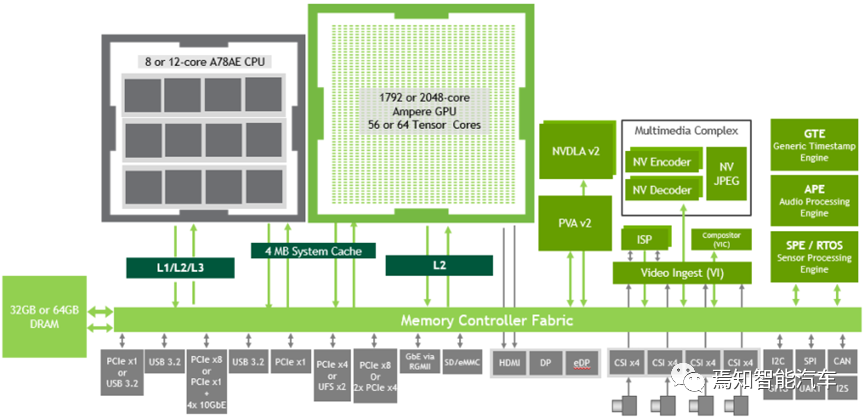

8.NVIDIA Jetson AGX Orin Series Technical Brief, 2022.

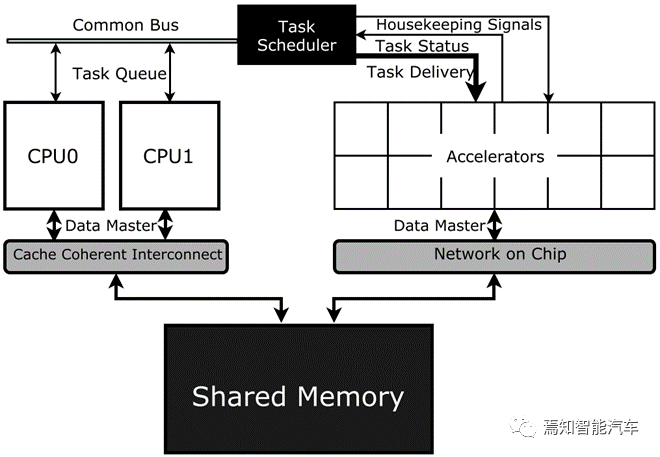

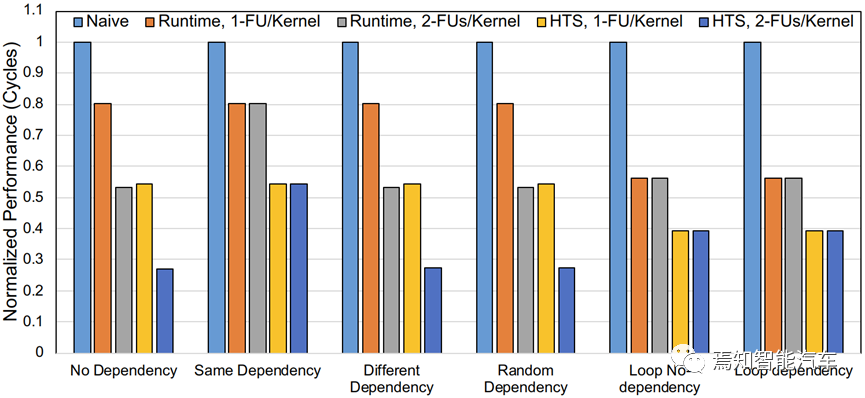

9.Hegde, Kartik, Abhishek Srivastava, and Rohit Agrawal. "HTS: A hardware task scheduler for heterogeneous systems." arXiv preprint arXiv:1907.00271 (2019).

10.Thoman, Peter, et al. "A taxonomy of task-based parallel programming technologies for high-performance computing." The Journal of Supercomputing 74.4 (2018): 1422-1434.

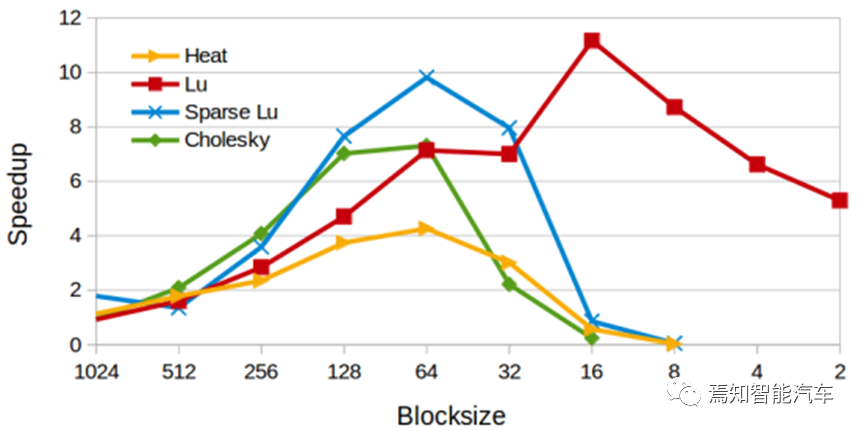

11.Tan, Xubin, et al. "Performance analysis of a hardware accelerator of dependence management for task-based dataflow programming models." 2016 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE, 2016.

12.Liao, Heng, et al. "Ascend: a scalable and unified architecture for ubiquitous deep neural network computing: Industry track paper." 2021 IEEE International Symposium on High-Performance Computer Architecture (HPCA). IEEE, 2021.

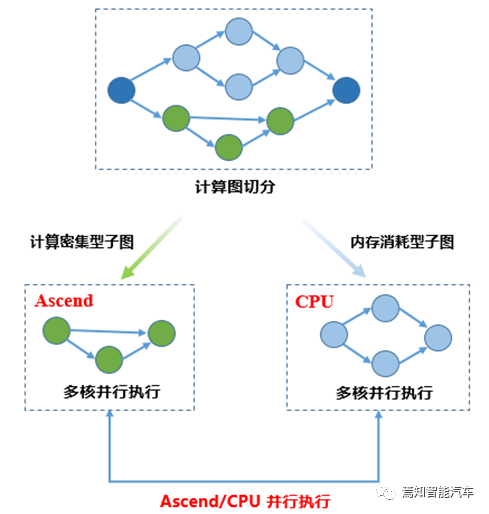

13.https://www.mindspore.cn/docs/zh-CN/r1.8/design/heterogeneous_training.html

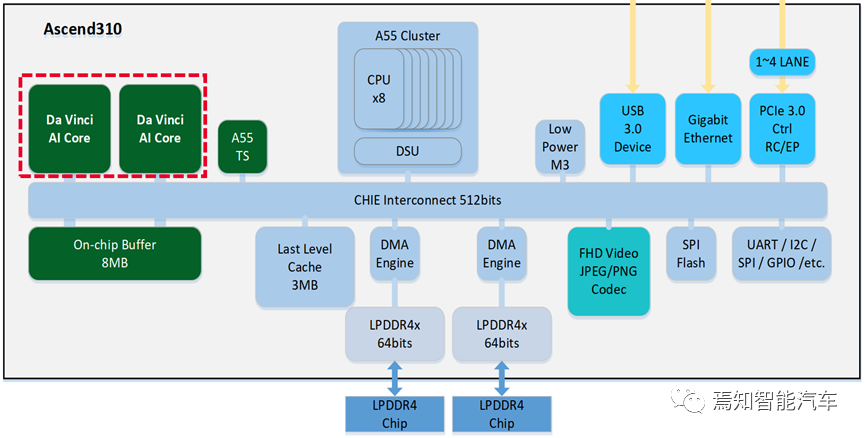

14.Liao, Heng, et al. "DaVinci: A Scalable Architecture for Neural Network Computing." Hot Chips Symposium. 2019.

上下滑动,可阅读更多

深度分析整车控制域现状与发展

分享不易,恳请点个【👍】和【在看】