时序分析时FPGA设计中永恒的话题,也是FPGA开发人员设计进阶的必由之路。慢慢来,先介绍时序分析中的一些基本概念。

时钟的时序特性主要分为抖动(Jitter)、偏移(Skew)、占空比失真(Duty Cycle Distortion)3点。对于低速设计,基本不用考虑这些特征;对于高速设计,由于时钟本身的原因造成的时序问题很普遍,因此必须关注。

理想的时钟信号应该是理想的方波,但是现实中的时钟的边沿变化不可能是瞬变的,它有个 从低到高 / 从高到低 的变化过程,如图1所示。

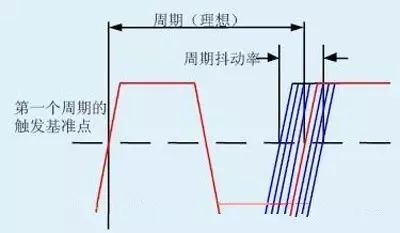

周期抖动(Period Jitter):

周期抖动率(Period Jitter)测量时钟输出传输偏离其理想位置的最大偏离。Period Jitter代表周期差抖动的上下边界。

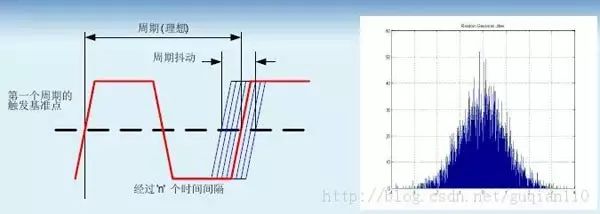

周期差抖动(cycle-to-cycle Jitter):

周期差抖动率(cycle-to-cycle jitter)是两个相邻周期的时间偏差。它总是小于周期抖动(period jitter)

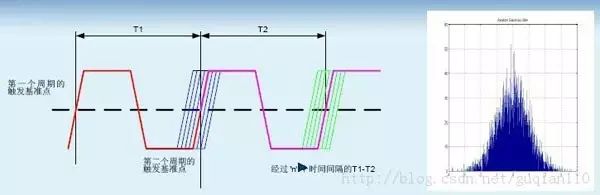

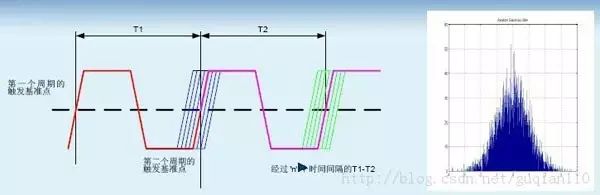

长期抖动(Long-term Jitter):

长期抖动率如下图(Long-Term Jitter)定义为一个时钟沿相对于基准周期时钟沿经过一段时间的延时之后,与其理想位置的偏离。此测量可以捕获锁相环低频周期变化(缓慢的,频率很低的)。长期抖动对图形、串行连接通讯系统、打印机和任何光栅扫描操作非常重要。

时钟抖动的原因就是噪声。时钟抖动是永远存在的,当其大到可以和时钟周期相比拟的时候,会影响到设计,这样的抖动是不可接受的。

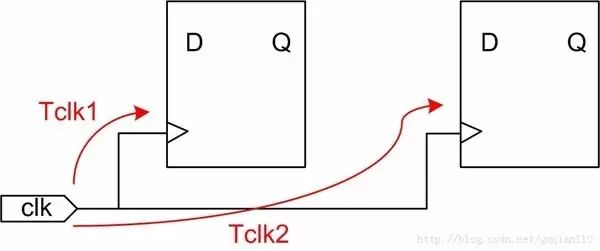

时钟信号要提供给整个电路的时序单元,所以时钟信号线非常长,并构成分布式的RC网路。它的延时与时钟线的长度、时序单元的负载电容、个数有关,所以产生所谓的时钟偏移。时钟偏移是指同一个时钟信号到达两个不同的寄存器之间的时间差值,根据差值可以分为正偏移和负偏移。

时钟偏移的计算公式:Tskew = Tclk2 - Tclk1

时钟偏移是永远存在的,当其大到一定程度会影响电路的时序。解决方法就是在FPGA的设计中让主要的时钟信号走全局时钟网络。该网络采用全铜工艺和树状结构,并设计了专用时钟缓冲和驱动网络,到所有的IO单元、CLB和块RAM的偏移非常小,可以忽略不计。

即时钟不对称,时钟的脉冲宽度发生了变化。DCD会吞噬大量的时序裕量,造成数字信号的失真,使过零区间偏离理想的位置。DCD通常是由信号的上升沿和下降沿之间时序不同而造成的。

The number of circuits that can be fed input signals from an output device. 扇出,输出可从输出设备输入信号的电路的数量。

扇出(fan-out)是定义单个逻辑门能够驱动的数字信号输入最大量的术语。大多数TTL逻辑门能够为10个其他数字门或驱动器提供信号。因而,一个典型的TTL逻辑门有10个扇出信号。

在一些数字系统中,必须有一个单一的TTL逻辑门来驱动10个以上的其他门或驱动器。这种情况下,被称为缓冲器(buf)的驱动器可以用在TTL逻辑门与它必须驱动的多重驱动器之间。这种类型的缓冲器有25至30个扇出信号。逻辑反向器(也被称为非门)在大多数数字电路中能够辅助这一功能。

模块的扇出是指模块的直属下层模块的个数。一般认为,设计得好的系统平均扇出是3或4。一个模块的扇出数过大或过小都不理想,过大比过小更严重。一般认为扇出的上限不超过7。扇出过大意味着管理模块过于复杂,需要控制和协调过多的下级。解决的办法是适当增加中间层次。一个模块的扇入是指有多少个上级模块调用它。扇人越大,表示该模块被更多的上级模块共享。这当然是我们所希望的。但是不能为了获得高扇人而不惜代价,例如把彼此无关的功能凑在一起构成一个模块,虽然扇人数高了,但这样的模块内聚程度必然低。这是我们应避免的。

设计得好的系统,上层模块有较高的扇出,下层模块有较高的扇人。其结构图像清真寺的塔,上面尖,中间宽,下面小。

时序分析起点(launch edge):第一级寄存器数据变化的时钟边沿,也是静态时序分析的起点。

时序分析终点(latch edge):数据锁存的时钟边沿,也是静态时序分析的终点。

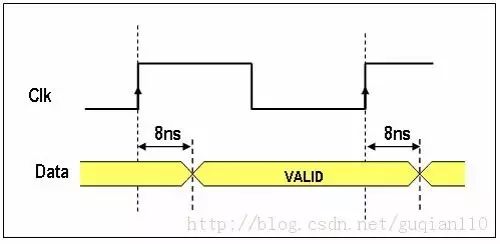

数据输出延时(Tco):这个时间指的是当时钟有效沿变化后,数据从输入端到输出端的最小时间间隔。

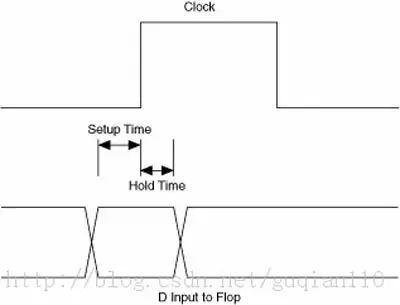

建立时间(setup time)是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T 时间到达芯片,这个T 就是建立时间Setup time。简而言之,时钟边沿触发前,要求数据必须存在一段时间,这就是器件需要的建立时间。如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。

保持时间(hold time)是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。简而言之,时钟边沿触发后,数据也必须保持一段时间,以便能够稳定读取,这就是器件需要的保持时间。如果hold time 不够,数据同样不能被打入触发器。

如果不满足建立和保持时间的话,那么DFF(D type flip-flop/D类型触发器) 将不能正确地采样到数据,将会出现亚稳态(metastability )的情况。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

输入数据在有效时钟沿后到达所需要的时间。主要分为三部分:时钟到达寄存器时间(Tclk1),寄存器输出延时(Tco)和数据传输延时(Tdata)

Data Arrival Time = Launch edge + Tclk1 +Tco + Tdata

时钟从latch边沿到达锁存寄存器时钟输入端所消耗的时间为时钟到达时间。

Clock Arrival Time = Lacth edge + Tclk2

当数据需求时间大于数据到达时间时,就说时间有余量,Slack是表示设计是否满足时序的一个称谓。

Setup slack = Data Required Time - Data Arrival Time

正的slack表示数据需求时间大于数据到达时间,满足时序(时序的余量),负的slack表示数据需求时间小于数据到达时间,不满足时序(时序的欠缺量)。

Recovery time is the minimum length of time an asynchronous control signal, for example, and preset, must be stable before the next active clock edge. The recovery slack time calculation is similar to the clock setup slack time calculation, but it applies asynchronous control signals.

Removal time is the minimum length of time an asynchronous control signal must be stable after the active clock edge. The TimeQuest analyzer removal time slack calculation is similar to the clock hold slack calculation, but it applies asynchronous control signals.

recovery time specifies the time the inactive edge of the asynchronous signal has to arrive before the closing edge of the clock.

Removal time specifies the length of time the active phase of the asynchronous signal has to be held after the closing edge of the clock.

也就是说Recovery / Removal time类似于Setup / Hold Time,不过是用于异步信号,比如set,reset信号。他们检查异步型号的边沿,释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放。注意异步复位亚稳态问题!

时钟最小周期:系统时钟能运行的最高频率。

(1)当数据需求时间大于数据到达时间时,时钟具有余量;

(2)当数据需求时间小于数据到达时间时,不满足时序要求,寄存器经历亚稳态或者不能正确获得数据;

(3)当数据需求时间等于数据到达时间时,这是最小时钟运行频率,刚好满足时序。

最小时钟周期为数据到达时间等于数据需求时间。

分析第9节的图,数据传播的路径从上一级触发器到下一级触发器建立经过的数据时延总和为:Tclk1 + Tco + Tdata + Tsetup-slack + Tsu

在两级寄存器之间,时钟间隔为:Tclk + Tclk2

根据建立时间要求(在下一个时钟上升沿到来的时候,数据必须稳定,且保持一定的时间Tsu)可以列一个不等式:数据时延 < 时钟间隔,即

Tclk1 + Tco + Tdata + Tsetup-slack + Tsu <= Tclk + Tclk2

同理,根据保持时间要求(时钟上升沿到来后,寄存器锁存数据的时候,数据要保持一定的稳定时间Th)可以列一个不等式:

Tco + Tdata <= Th

随着系统时钟 fclk 变大时,Tclk变小,则要求 Tco + Tdata 也变小,当 Tco + Tdata 不满足第一个不等式时,不满足建立时间要求;但是,Tco + Tdata 也不是越小越好,当其太小时,不满足第二个不等式时,触发器不能正常锁存数据,即不满足保持时间要求。从某种意义上说,Th限制了数据传输速率。

对于设计者来说最大的目的是提高时序的裕量,这样即使信号完整性上出现一点问题,或者外界环境发生一定的变化,系统仍然能正常工作,这就是一个设计优良的系统应该体现出的超强的稳定性。

本文转自:CSDN

-END-

#推荐阅读#

了解这3个特性,再也不担心传输线问题了!

104条!PCB线路设计术语大全,用得上!

【非常经典】开关电源各种保护电路实例

阅读英文数据手册总是很难?五招轻松搞定!

出色的硬件工程师必备的几项“硬”实力

菜鸟与老手搭的电路板,一对比吓一跳!

8个维修电路板的狠招

这样来看电路,真是绝了!

Altium Design PCB拼板完整教程,这样讲就明白了!

-5V、-3V这负压是怎么产生的?

为什么会有0欧电阻这种东西?

▼ 点击阅读原文,下载《电子元器件及手工焊接》