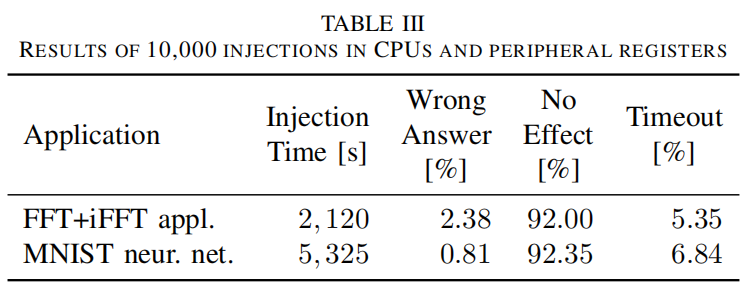

确保将最高质量的产品运往市场,并保证它们在其生命周期内持续工作,是汽车芯片制造商的首要目标。的确,我们需要大力改进和加强制造测试程序,以使整个芯片种群中的潜在故障少之又少。然而,高质量的生产必须遵循现场可靠性;制定战略和活动来面对前方生命周期的关键问题也具有非常高的优先地位。本文的贡献包括以下几个方面的描述和结果:(1)一种非常精确的方法来评估FLASH制造测试的功耗;(2)一种有效的多核基于软件的自检生成策略,面向人工智能的计算机体系结构;(3)一个高水平和非常快速的系统级芯片的架构仿真器,用于原型设计辐照实验和预测运动结果,对处理器和外围核心的单一事件设置具有良好的准确等级。

第五节得出了一些结论,并强调了汽车主题的合理看法。

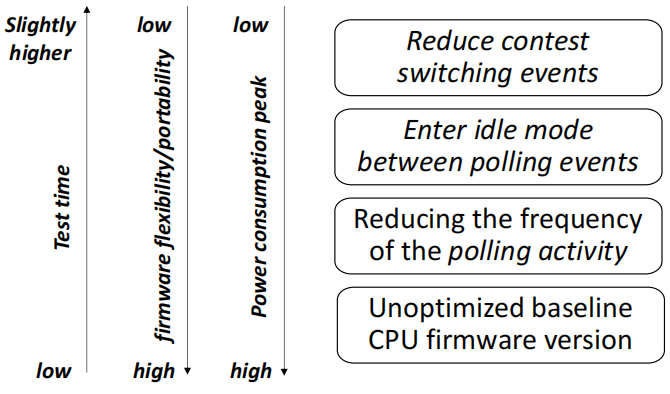

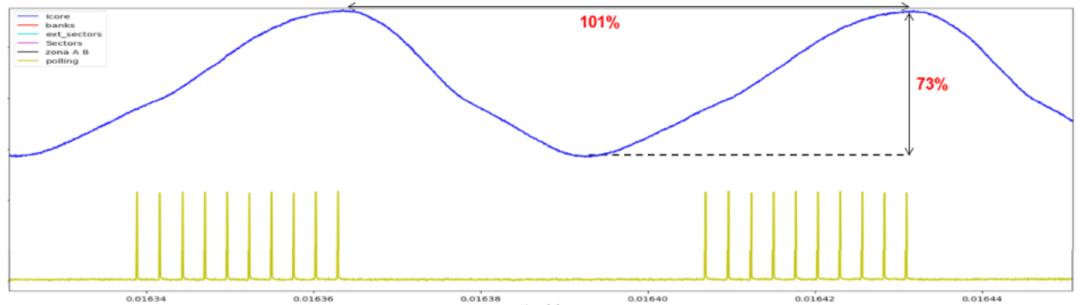

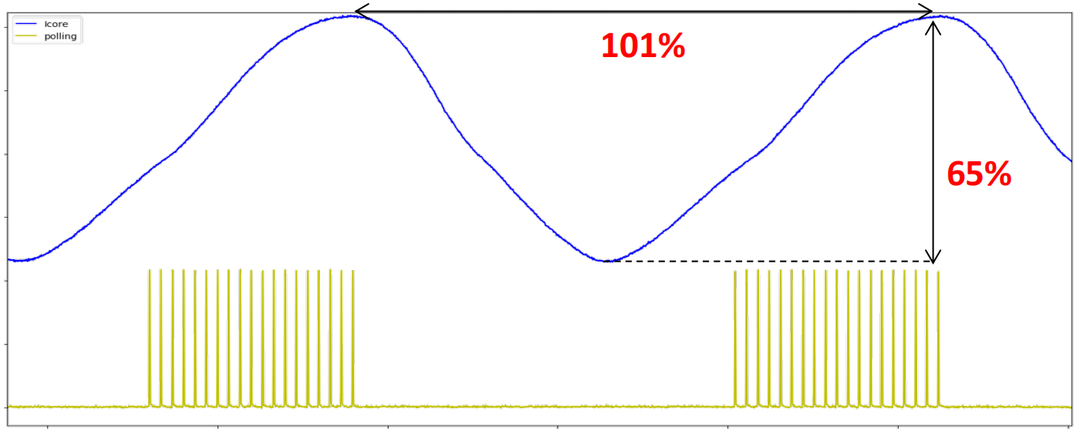

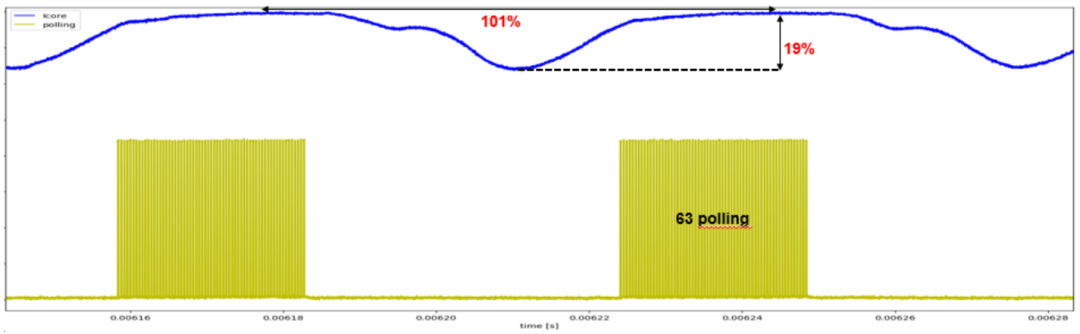

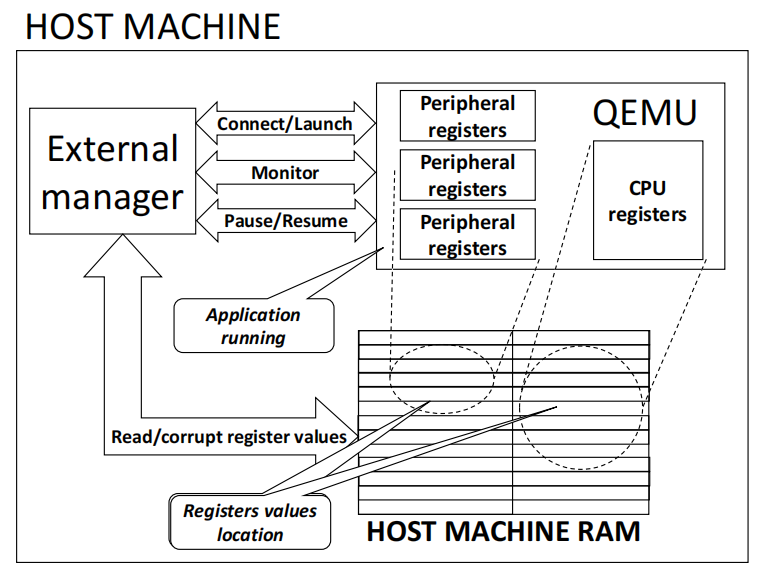

图2 固件级别探索及其利弊

图2 固件级别探索及其利弊

另外,基于空转的方法可以节省较少但显著的电流输入,并且对测试时间影响有限。

整个STL在16个CPU核心上同步运行的测试应用间在100MHz下约为8ms,大小约为20KB,这验证了在实时系统的现场测试中采用这种测试技术的可能性。

IV.用于汽车应用可靠性评估

的高级故障注入

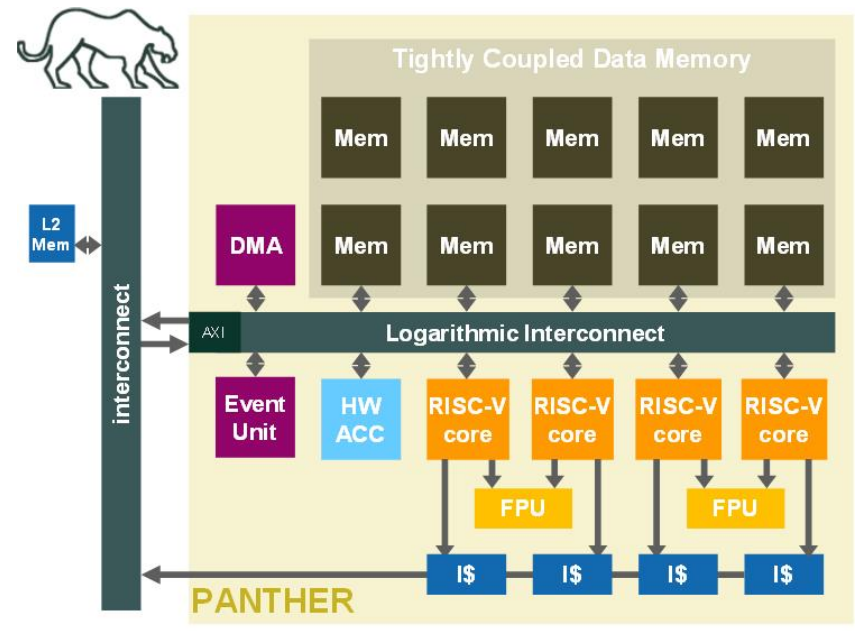

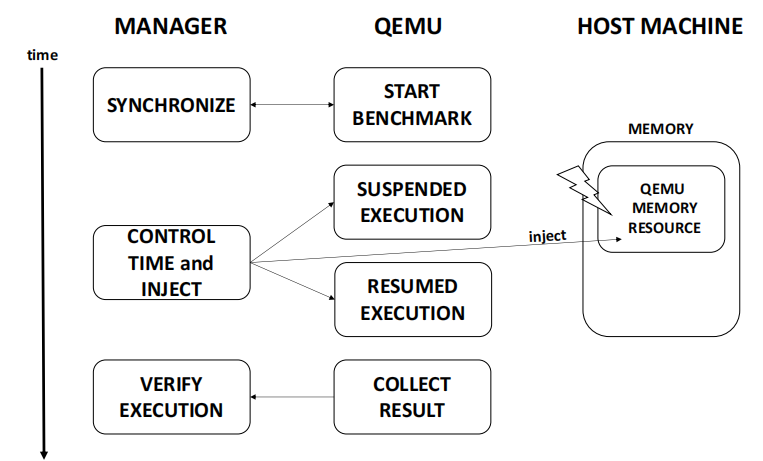

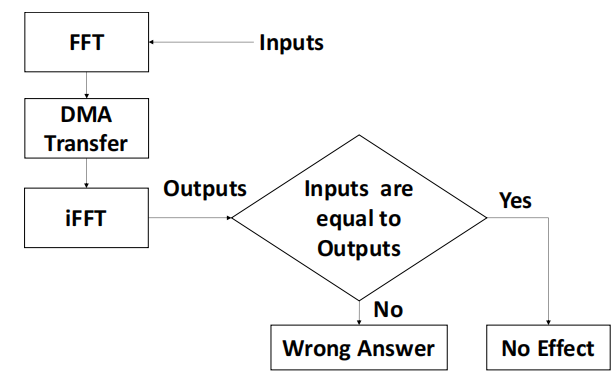

值得注意的是,这种方法不需要芯片的网表,因此既可以被芯片供应商采用,以提前表述其设计,也可以被终端用户采用,后者可以快速运行其应用程序,并在辐照芯片之前获得近似的结果进行分析。

作为一个经验教训,对最合适的测试程序进行准确的评估和规划,可以使高质量的汽车产品符合半导体生产商以及更高层次的期望。

参考文献:

[1] H.-G. Stratigopoulos, F. Su, A. Coyette, C. He, E. Faehn, and D. Tille, “Panel: “New automotive design methodologies for catching latent defects and detecting anomalies online”,” in 1st Automotive Reliability and Test in Europe (ARTe 2021), 2021.

[2] A. Ciarci, D. Tille, and P. Bernardi, “Towards an Automated Flow for Implementation of Dedicated LBIST Scan Chains for Functional Safety,” in 33rd GI / GMM / ITG-Workshop Test Methods and Reliability of Circuits and Systems, 2021.

[3] S. Ravi, “Power-aware test: Challenges and solutions,” in 2007 IEEE International Test Conference, 2007, pp. 1– 10.

[4] N. Mamikonyan, N. Melikyan, and R. Musayelyan, “IR Drop Estimation and Optimization on DRAM Memory using Machine Learning Algo- rithms,” in 2020 IEEE East-West Design Test Symposium (EWDTS), 2020, pp. 1–4.

[5] A. Manzini, P. Inglese, L. Caldi, R. Cantoro, G. Carnevale, M. Coppetta, M. Giltrelli, N. Mautone, F. Irrera, R. Ullmann, and P. Bernardi, “A Machine Learning-based Approach to Optimize Repair and Increase Yield of Embedded Flash Memories in Automotive Systems-on-Chip,” in 2019 IEEE European Test Symposium (ETS), 2019, pp. 1–6.

[6] ISO, “Road vehicles – Functional safety,” 2011.

[7] P. Bernardi, M. Grosso, E. Sanchez, and O. Ballan, “Fault grading of software-based self-test procedures for dependable automotive applica- tions,” in 2011 Design, Automation Test in Europe, 2011, pp. 1–2.

[8] A. Garofalo, M. Rusci, F. Conti, D. Rossi, and L. Benini, “PULP- NN: accelerating quantized neural networks on parallel ultra-low-power RISC-V processors,” Philosophical Transactions of the Royal Society A, vol. 378, 2019.

[9] P. Bernardi, R. Cantoro, S. De Luca, E. Snchez, and A. Sansonetti, “Development Flow for On-Line Core Self-Test of Automotive Micro- controllers,” IEEE Transactions on Computers, vol. 65, no. 3, pp. 744– 754, 2016.

[10] F. Wang and V. D. Agrawal, “Single Event Upset: An Embedded Tutorial,” in 21st International Conference on VLSI Design (VLSID 2008), 2008, pp. 429–434.

[11] L. Cassano, H. Guzman-Miranda, and M. A. Aguirre, “Early assessment of SEU sensitivity through untestable fault identification,” in 2014 IEEE 20th International On-Line Testing Symposium (IOLTS), 2014, pp. 186– 189.

[12] E. Jenn, J. Arlat, M. Rimen, J. Ohlsson, and J. Karlsson, “Fault injection into VHDL models: the MEFISTO tool,” in Proceedings of IEEE 24th International Symposium on Fault- Tolerant Computing, 1994, pp. 66– 75.

[13] O. Ballan, P. Maillard, J. Arver, C. Smith, R. Petersson, A. Griessing, and F. Venini, “Evaluation of ISO 26262 and IEC 61508 metrics for transient faults of a multi-processor system-on-chip through radiation testing,” Microelectronics Reliability, vol. 107, p. 113601, 2020.

分享不易,恳请点个【👍】和【在看】