功能简述

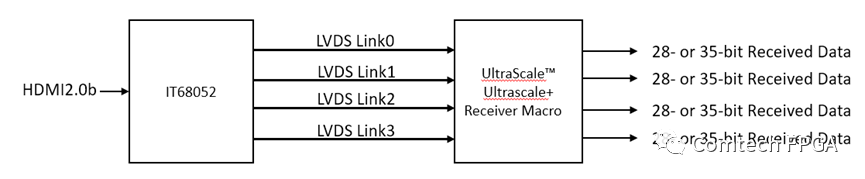

图 1: 1:7 接收端模块

数据接收实现介绍

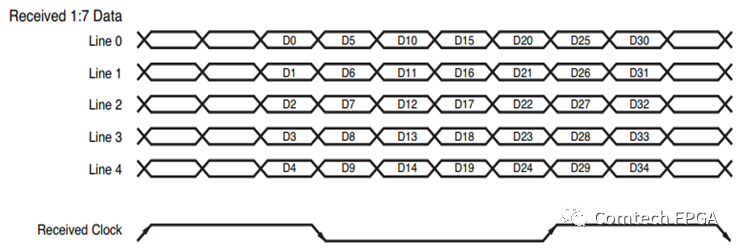

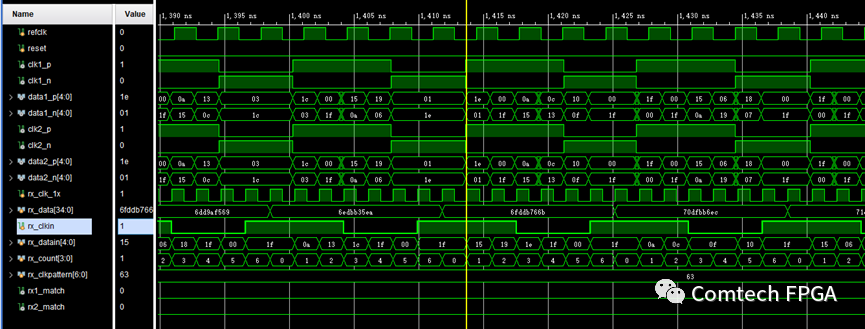

图 2: 1:7 接收数据

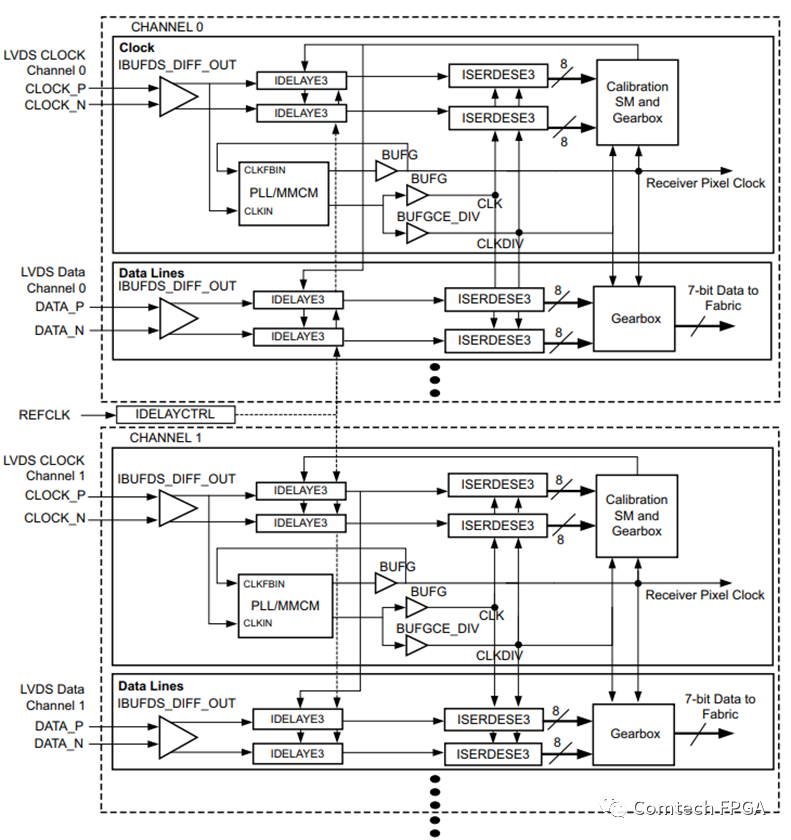

由于接收的数据流是输入时钟速率的7倍,时钟信号被用作接收数据的信号。在一个时钟周期内,数据线有7个状态变化。接收器使用1:8 DDR模式的ISERDESE3和基于8:7 Distributed RAM 的gearbox(如图3所示)来bit拼接调整和对齐输入数据流。

首先LVDS clock输入处理变成三个时钟域,一个1/2速率的采样时钟(rx_clkdiv2),一个1/8速率的反序列化数据时钟(rx_clkdiv8),以及一个1/7的像素时钟(px_clk),这相当于原始接收器源时钟。

接收器源时钟在MMCM或PLL中乘以7或14以满足VCO的频率范围,然后除以2以产生1/2速率的采样时钟(rx_clkdiv2),再除以7以产生接收像素时钟(px_clk)。1/8速率的反序列化数据时钟 (rx_clkdiv8)由1/2速率采样时钟MMCM或PLL输出产生,使用BUFGCE_DIV,以尽量减少ISERDESE3 CLK和CLKDIV输入之间的时钟偏移。

图 3:数据接收

图 4:数据接收1:7仿真

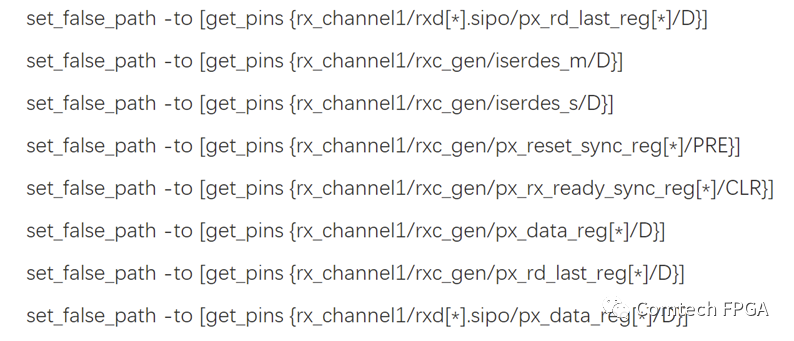

接收端设计的考虑因素

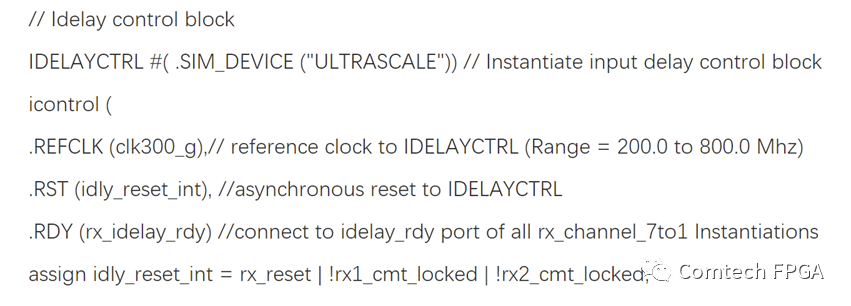

复位顺序要求

按照下面复位顺序:

A. 先对rx_channel_1-7复位清零;

B. 等待MMCM/PLL锁定置位;

C. IDELAYCTRL复位清零;

D. 当px_ready清零时,px_data输出总线有效;

如果您在LVDS高速传输数据方面有问题,欢迎联系

simonyang@comtech.cn

charlesxu@comtech.cn