可编程数据平面从根本上改变网络元素的构建和管理方式,也在一定程度上平衡了灵活性和性能之间的矛盾,这种平衡行为的关键是对数据包处理的良好抽象。数据包处理的常见抽象是匹配动作流水线,最早由OpenFlow提出。通过匹配动作抽象,可以将包处理器建模为一系列匹配和动作流水线阶段。每个流水线阶段对流经的数据包执行不同的操作。这种抽象可以映射到FPGA和下一代ASIC。在这种情况下,与平台和体系结构无关的P4 语言应运而生。为支持P4语言,可编程数据平面大都采用可重配置匹配动作表(Reconfigurable Match Tables,RMT)抽象转发模型,定义了可编程解析、可编程匹配与可编程动作等数据包处理行为,而使用 P4 编程语言,可以快速简便地对数据包处理行为进行描述。因此,在人们的印象中,提到P4语言,大脑中就自动出现解析器、逆解析器和多级流表的架构,想到了Barefoot的Tofino芯片。认为解析器、逆解析器加多级Match Action流表的架构就是P4语言唯一硬件架构。然而,实际上,除了这种架构外,还有好几种其它的实现架构。比如在今年8月下旬即将召开的SIGCOMM会议上,MIT和Juniper的研究人员联合发表了一篇介绍Trio芯片架构的文章,Trio 芯片就不是采用流水线架构来实现对P4语言支持的。文章主要面向新的应用场景与传统的PISA流水线架构的交换芯片的性能进行对比,现将该文章部分译文奉上,以飨读者。感兴趣的读者也可以提前阅读扎神的文章《Trio 6, Express 5 and Silicon One》以更全面了解相关内容和背景。

01

引言

尽管可编程交换机一直是这种新模式的重要推动者,但独立于协议的交换机架构(PISA)[2, 20, 22, 58]往往不适合新兴的网内应用,从而限制了进一步发展,阻碍了网内计算应用的广泛采用[35, 37, 67]。

本文介绍了Trio的网络内计算可编程架构。Trio是瞻博网络的可编程芯片组,拥有数十亿美元的预存客户群。它已被部署在全球核心、边缘和数据中心环境中的数十万台路由器和交换机中。Trio芯片组在生产设备中使用已超过十年。

Trio建立在一套定制的处理器内核上,其指令集针对网络应用进行了优化。因此,该芯片组具有传统ASIC的性能,同时享有完全可编程处理器的灵活性,允许通过软件安装新功能。Trio的灵活架构使其能够支持在芯片组发布后很长时间内开发的功能和协议。Trio处理器内核可以访问一个高性能的大内存系统,以存储与系统配置和数据包有关的数据和状态。该内存系统对具有大内存足迹的新兴应用的可扩展性至关重要。

Trio的结构与Tofino的结构有根本的不同。Trio有一个非流水线结构,因此不同的数据包不一定流经芯片上的相同物理路径。Trio中的入站数据包是使用成千上万的并行线程独立处理的(详情见2)。这些线程使用运行-完成模型[12, 70],其中一个线程将执行所需的指令,以完成它目前正在处理的数据包的处理。Trio有专门的逻辑,以确保同一流量的数据包按顺序交付,但不同流量的数据包可以不按顺序处理,使其能够有效地处理混合的并发应用。

因此,Trio可以优雅地处理不同的数据包处理率:它可以为需要丰富的每包处理的应用提供低于线速的支持,同时为具有简单的每包处理需求的应用保持线速。相比之下,基于PISA的交换机在处理数据包时,处于同一流水线的数据包需要遍历流水线的各个阶段,无论P4程序是怎样的;P4程序[19]的部署只有完全成功和完全失败两个结果,基于PISA的交换机无法支持灵活的数据包处理速率,以可编程性为代价,换取数据包的线速处理能力。

在本文中,我们首先描述了Trio芯片组的基本构件,包括其数据包处理引擎和周围的内存系统的细节(2)。接下来,我们描述了Trio的编程语言,称为Microcode(3)。然后,我们以机器学习训练的网络内聚合作为第一个用例,解释Trio灵活的Microcode设计(4)。我们将网络中的串扰缓解作为第二个用例,以证明Trio在启动高效的基于定时器的线程方面的独特能力(5)。我们证明了在Trio中实现滞留者缓解是直接的,而据我们所知,在基于PISA的设备中实现高效的滞留者缓解是具有挑战性的,甚至是不可能的。

我们在一个带有Juniper MX480设备[10]、一个64个100Gbps Tofino交换机和六个华硕ESC4000AE10服务器的测试平台上实现这两个用例,每个服务器都有一个A100 Nvidia GPU[11]和一个100Gbps Mellanox ConnectX5网卡。我们训练三个DNN模型(ResNet50[41]、DenseNet161[42]和VGG11[68]),以证明Trio在执行网内聚合的同时减轻散兵线的能力。我们的评估表明,当集群中出现散工时,Trio比最先进的网内聚合平台SwitchML[63]的性能高出1.8倍。

瞻博网络将继续发展Trio芯片组,为现有和新兴应用提供更高的带宽、更低的功耗和更多的功能,同时还将开发软件基础架构以支持更多的使用案例。我们邀请网络界确定能够利用Trio可编程架构的新用例。

02

自2009年推出以来,Trio芯片组已经经历了六代[16],具有各种性能点和架构。本节详细介绍了Trio的最新架构。首先,我们对基于Trio的路由器1中的数据包转发和处理做了一个高层次的概述。然后,我们转向Trio的数据包处理引擎的细节。最后,我们解释Trio的各种内存类型和读-改-写操作。

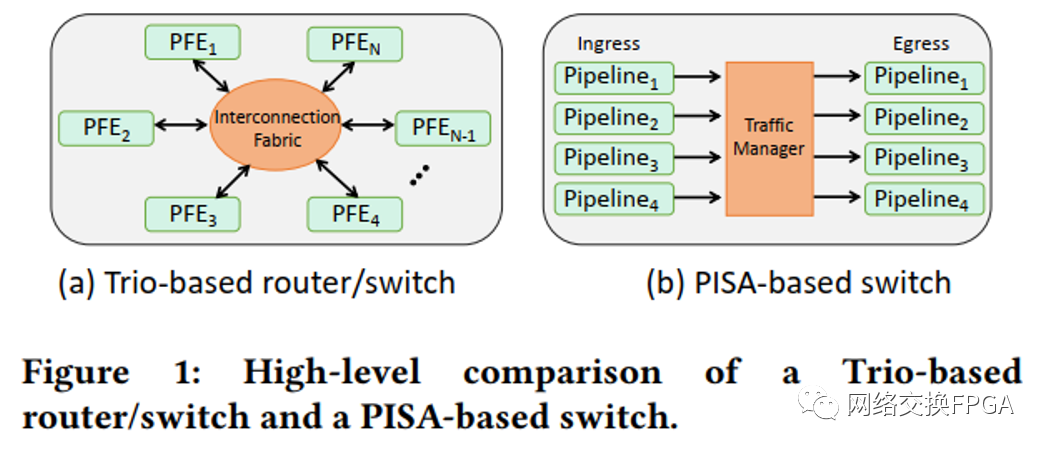

图1说明了基于Trio的路由器(或交换机)与基于PISA的交换机之间的高层区别。每个基于Trio的设备都有两个重要的组成部分:(i)包转发引擎和(ii)包处理引擎,下面将介绍。

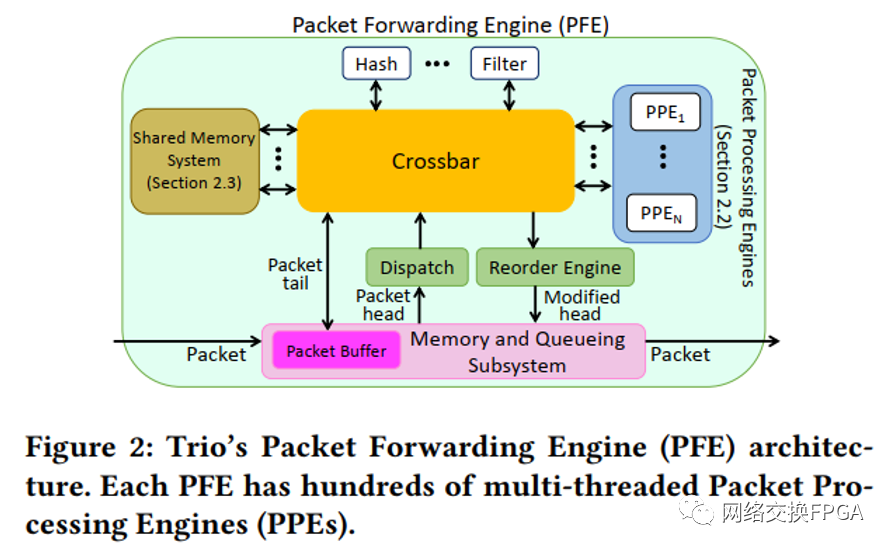

数据包转发引擎(PFE)。PFE是Trio转发平面的中心处理元素,用于系统地将数据包移入和移出设备。一个基于Trio的设备由一个或多个PFE组成。根据不同的年代,每个Trio芯片组支持不同的数据包处理带宽。Trio的第一代PFE用多个芯片支持40Gbps的网络带宽。今天,Trio的第六代PFE在单个芯片中支持1.6 Tbps。小型路由器可能只有一个PFE,而大型路由器则有多个PFE,通过互连结构连接,如图1(a)所示。通过在PFE之间提供any-to-any的全互连连接,互连结构扩大了设备的带宽,远远超过了单个芯片所能支持的范围。每个PPE在入口和出口方向上都处理数据包。数据包通过一个入口PFE到达系统,并通过一个出口PFE离开。

包处理引擎(PPE)。每个PFE都有数百个多线程的包处理引擎(PPE),如图2所示。每个PPE支持几十个线程同时处理不同的数据包。与Tofino的架构不同,流水线不能访问对方的寄存器,一个PFE中的PPE线程可以通过共享内存有效地共享状态。第2.2节更详细地解释了PPE的基于线程的设计。

平行数据包处理。PFE的硬件逻辑自动将每个进入的数据包分为头和尾部分(类似于PISA的头和有效载荷)。数据包头是数据包的第一部分,通常大到足以容纳处理数据包所需的所有数据包头(每一代Trio设备的数据包头大小不同,但通常约为200字节)。尾部由数据包的剩余字节组成(如果有的话)。当一个新的数据包到达时,PFE内部的一个硬件模块,称为调度模块,根据可用性将数据包头发送到PPE进行处理,PPE为这个数据包头生成一个新线程。数据包尾部被保存在PFE的内存和队列子系统中的数据包缓冲区,以避免在PPE线程中存储大量的字节。默认情况下,每个线程在一个数据包上工作。许多PPE线程并行工作以提供所需的处理带宽。

重新排序引擎。当数据包处理完成后,修改后的数据包头被发送到重新排序引擎。重排引擎保留更新的包头,直到同一流程中所有较早到达的数据包都被处理,以确保按顺序交付。然后,Reorder Engine将修改后的数据包头发送到内存和排队子系统,以便排队传输。

Trio的PPE提供了固定处理流水线或现有专门处理单元难以或无法实现的功能。每个PPE都是一个VLIW(超长指令字)多线程的微码引擎核心。每个微指令都控制着多个ALU、操作数和结果选择,以及复杂的多路分支。执行一个微指令所需工作的复杂性意味着每个指令需要多个时钟周期。因为每个PFE通常同时为许多数据包提供服务,所以一个PPE不需要高的单线程性能。Trio中的每个线程一次只有一条数据通路指令。Trio不会将同一线程上的指令与前一条指令分派到PPE流水线中,直到后者退出流水线。因此,不需要在同一线程的指令之间传递数据,因为在数据回写完成之前,后续指令不依赖于前一指令的结果。

PPE线程。一个PPE线程通常在数据包头到达PPE时启动,并在该PPE对该数据包的处理完成后销毁。线程的销毁由芯片中的硬件逻辑自动处理,尽管程序员可以控制何时放弃线程的执行。线程也可以响应某些内部事件而启动,包括统计收集和定时器(更多细节见5)。外部事件有能力通过类似的机制来催生新线程的执行。入口和出口PFE中的PPE共同处理处理数据包所需的所有功能(例如,数据包解析、路由查找、数据包重写)。

每线程本地存储。每个PPE有两种主要的内部存储形式。首先,每个线程有一个专用的本地存储器池(1.25 KBytes)。本地存储器可以在任何字节边界访问,使用指针寄存器或微指令中包含的地址。在一个PPE线程启动之前,数据包头被加载到该线程的本地存储器中。当发送数据包时,修改后的数据包头会从线程的本地存储器中卸载。指针寄存器的使用允许对包头以及其他类型的数据结构进行有效的访问。其次,每个线程都有32个64位的通用寄存器,这些寄存器对它是私有的。本地存储(内存和寄存器)持有正在处理的数据包的特定信息。跨包的共享状态被保存在所有PPE都可以访问的共享内存系统中。

ALU类型。有两种ALU类型:(i)条件ALU和(ii)移动ALU。条件ALU用于算术或逻辑运算,产生32位数据结果和/或用于比较运算,产生1位条件结果。移动ALU产生32位的结果,可以写进寄存器或本地存储器。来自条件ALU的结果可以作为移动ALU的输入。这种ALU组织允许每个指令的资源在排序控制(接下来描述)和生成逻辑/算术结果之间灵活分配,以存储在寄存器/存储器中。重要的是,每个ALU操作数和每个移动ALU结果可以是一个任意长度的位域(最多32位)和一个任意的位偏移。这有两个主要的好处。首先,它提高了访问包头中不同大小的字段的效率。第二,它提高了内存和寄存器容量的利用率,使每块数据只使用它所需要的比特。Trio在PPE和共享内存系统中都有ALU。前者用于对寄存器和本地存储器的操作,而后者则用于对存储在共享存储器系统中的数据进行操作。通过将数据包尾部的部分移动到PPE线程的本地存储器,也支持对数据包尾部的操作。

排序逻辑。一个或多个条件ALU的条件结果可以被排序逻辑单元用来选择下一个要执行的微指令。每个微指令包括一个至八个微指令的目标块的地址。任何或所有的条件结果都可以被忽略,所使用的条件结果的组合也非常灵活。数据包处理中的许多工作涉及代码中复杂的条件分支,特别是在解析期间。Trio在一条指令中执行复杂的多路分支的能力与数据包处理应用的需求非常匹配。PPE支持对子程序的调用-返回机制,子程序可以嵌套到八层深处。

高效的哈希计算。高效的负载平衡是所有路由器/交换机的一个重要要求。在一个基于Trio的系统中,一个Microcode程序负责指定哪些数据包字段被包括在哈希计算中。这使得哪些数据包字段有助于负载平衡的决定具有完全的灵活性,包括从协议尚未发明的数据包头中选择字段的能力。Trio中的哈希函数是一个使用专用逻辑实现的高质量哈希函数。因此,哈希函数的实现比用软件实现的类似哈希函数更有效。可编程字段选择和硬接线哈希函数的结合,使PPE在灵活性和效率方面达到了前所未有的平衡。

灵活的编程。对PPE可处理的报头数量或类型没有固定限制。因此,PPE可以使用Trio的微码程序(3)轻松创建新的报头或消耗/删除数据包中的现有报头。随着新协议的开发,Trio数据包处理架构可以通过增强运行在PPE上的软件来适应。由于PPE的多线程结构,PPE还可以创建或消耗数据包来完成任务,如保持功能,其速度远远高于控制平面CPU所能支持的速度。重要的是,处理周期在不同的应用之间是可以互换的,从而能够优雅地处理不同应用的数据包处理要求。因此,基于Trio的系统可以为数据包处理较丰富的应用提供较低的数据包速率,为数据包处理较简单的应用提供较高的数据包速率,或两者混合使用。

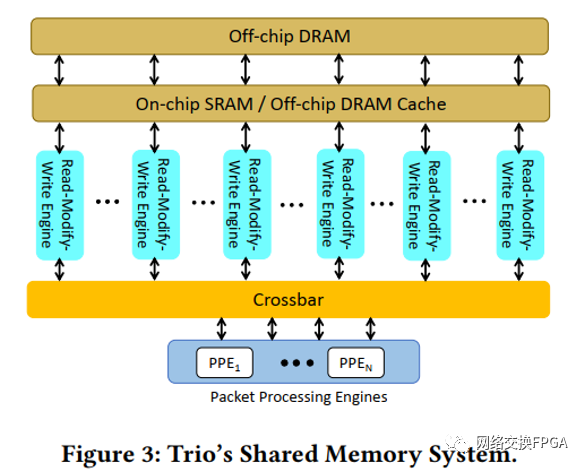

最近的Trio芯片组在每个PFE中支持几个GBytes的内存。本节对Trio的共享内存系统进行了概述。

共享内存的优点。对于交换机和路由器来说,一些数据结构,如计数器和(流量)管制器,需要以很高的速度修改。为了支持数百个PPE线程对这些数据结构的有效访问,Trio的共享内存系统成为所有线程访问和修改数据的地方。所有对共享内存系统的数据访问(读、写和读-修改-写)都由位于共享内存系统附近的读-修改-写引擎处理。当多个线程在同一时间访问同一内存位置时,不需要将数据从一个线程移到另一个线程。相反,数据修改发生在读-修改-写引擎内部。这允许在内存附近高速更新数据,很好地满足了数据包处理应用的需要。相比之下,传统处理器使用的基于缓存线的一致性模型需要在访问过程中把数据移到线程中;当多个线程试图修改同一内存位置时,这会造成较长的延迟。虽然这种模型可以支持对数据进行更复杂和更普遍的操作,但对于可以被数百个线程访问的数据结构来说,它的表现很差。

内存类型。Trio存储器系统经过优化,为相对较小(8字节)的请求提供了较高的访问速率。为了实现所需的带宽、延迟和容量的组合,存储器系统使用两种类型的存储器,如图3所示:(i)高带宽的片上存储器,从PPE的访问延迟约为70ns;(ii)基于DRAM的大型高带宽片外存储器,从PPE的访问延迟约为300 ns至400 ns。片上存储器是由一个严重的多槽SRAM实现的,通常用于频繁访问的数据结构。片外存储器有一个几百万字节的片上缓存,它与片上SRAM类似,并且是大量的多Bank,以提供高吞吐量。片上SRAM和片外DRAM缓存的大小是可以软件配置的(通常分别为2-8 MBytes和8-24 MBytes)。片外DRAM是几GB字节。片内和片外存储器在结构上是等同的,存在于一个统一的地址空间的不同范围内。它们只在容量、延迟和可用带宽上有所不同。这使得数据结构可以被放置在最符合其容量和带宽要求的存储器类型中。

内存交易。内存系统支持不同大小的读写操作,从8字节到64字节(以8字节为增量)。Trio可以用8字节的访问来支持全部的内存系统带宽。此外,还支持丰富的读-改-写操作,包括数据包/字节计数器、Policers、逻辑获取和操作(And/Or/Xor/Clear)、获取和交换、屏蔽式写入和32位添加。读-修改-写操作由读-修改-写引擎启用,具体规定如下。

读-修改-写引擎。数据包处理需要极其高速的读-修改-写操作。处理一个数据包可能涉及到对多个计数器的更新,对一个或多个策略器的操作,以及应用程序需要的其他操作。处理读-改-写操作的天真方法是,在操作进行时,让一个线程拥有一个内存位置的所有权。但这种方法不能满足数据包处理的高效率要求。相比之下,Trio将读-改-写操作卸载到它的内存系统中,由一个读-改-写引擎来处理一系列的内存位置。如果对同一内存位置的多个请求在同一时间到达,该引擎将依次处理这些请求,以保证更新的一致性。在混合读、写和读-修改-写操作时,不需要向内存中的某个位置发出明确的一致性命令。每个读-改-写引擎以每个时钟周期8字节的速度处理内存请求。因此,整个共享内存系统的单个读-修改-写引擎不能提供足够高的速率处理数据包所需的内存带宽。为了应对这一挑战,Trio支持几组SRAM和片外缓存,并有自己的读-修改-写引擎,使读-修改-写处理带宽能够与原始内存带宽一起扩展。

Crossbar和共享内存性能。Trio的Crossbar被设计为支持所有的读-修改-写引擎,因此Crossbar本身不会限制内存性能。如果提供给某个读-改-写引擎的负载超过了每周期8字节的吞吐量,就会通过Crossbar产生背压。瞻博网络在每一代Trio芯片中都增加了读-改-写引擎的数量,以便内存带宽随着数据包处理带宽的增加而增加。

03

本节对Trio的编程环境进行了概述。第1节描述了Trio的编程语言和基于Trio设备的编程工具链。第2节提供了一个用Trio微代码编程的数据包过滤例子。

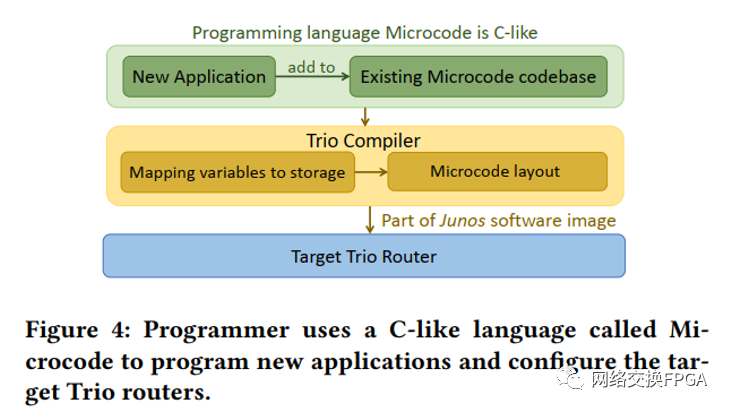

基于Trio的设备的编程语言是一种叫做Microcode的类C语言。程序员在Microcode中实现所有的数据包处理操作,包括数据包解析、路由查找、数据包重写和网络内计算(如果有)。图4显示了在Trio上为新的应用程序编程所需的工具。要在Trio上编程一个新的应用程序,程序员使用Microcode语言来编写新的应用程序,并将新的Microcode程序添加到现有的代码库中。然后,程序员使用Trio的编译器生成软件图像并配置目标设备。

表达式语法。Microcode支持C风格的表达式。支持的变量类型包括标量(label, bool, 和不同大小的整数)和复合(struct 和union)。Microcode还支持指针和数组,条件,函数调用和Gotos,以及switch语句。

指令边界。一个Microcode程序有多个指令。一条Microcode指令可以执行有限的操作,程序员需要明确指定指令的边界。通常情况下,一条Microcode指令可以执行四个寄存器或两个本地存储器的读取,以及两个寄存器或两个本地存储器的写入。

变量存储类。当在Microcode中定义一个新的变量时,程序员需要指定存储该变量的位置。有三种类型的变量存储类:内存(PPE的本地内存和寄存器),总线(表示变量作为ALU的输入),和虚拟(表示常量值)。对存储在共享内存系统中的数据的访问,如转发表,是通过下面规定的外部事务实现的。

外部交易。PPE可以通过Crossbar向其他模块发出外部事务(XTXN),如共享内存系统、哈希查找/插入/删除、高性能过滤器和计数器/警戒器块。这些XTXN可以是同步的或异步的。在同步XTXN中,PPE线程被暂停,直到收到XTXN回复;在异步XTXN中,PPE线程继续正常运行。PPE也可以通过XTXNs从数据包尾部获取数据。在这种情况下,数据包尾巴从内存和队列子系统发出,通过Crossbar,然后到达PPE的本地内存。一个XTXN由PPE向目标发出的请求和目标向PPE发回的回复组成。XTXN的格式取决于目标块。例如,发送到共享内存系统的读取请求以内存地址为参数,数据在XTXN响应寄存器中返回。

编译器。为了编译Microcode程序,程序员使用一个叫做Trio Compiler(TC)的工具。TC将指令的源代码映射到指令可以控制的各种资源,包括将变量映射到它们的底层存储,并将指令分配到PPE内的Microcode内存。TC同时具有编译器和汇编器的特点。在编译器方面,TC支持将高级C风格的表达式翻译成硬件指令。在汇编器方面,TC的源代码必须包含指令的划分,即程序员标记代表一条指令的代码块的开始和结束。如果指定给一条指令的代码不合适,TC的编译就会失败,因为它不能在多条指令中实现要求的动作。TC没有一个单独的编译和连接阶段。它需要完整的源代码而不是单个模块来生成二进制文件。这个二进制文件包含初始化PPE资源的数据,如Microcode内存和本地内存。它还定义了所需的符号,如本地内存中数据包头开始的地址。该二进制文件是Trio的ASIC驱动程序用于设备初始化的Junos2软件镜像的一部分。

vMX虚拟路由器。瞻博网络正在共同努力,使第三方能够访问基于Trio的设备编程。作为第三方访问Trio功能的第一步,瞻博网络开发了vMX虚拟路由器[5]。vMX是一个虚拟化的通用路由平台,由一个虚拟控制平面(VCP)和一个虚拟转发平面(VFP)组成。VCP由Junos操作系统驱动,VFP运行为x86环境优化的Microcode引擎。vMX可作为授权软件,部署在基于x86的服务器和云服务上,如亚马逊网络服务。

高级转发接口。在Trio中,数据包转发是一个由PFE执行的操作序列。每个操作都可以用潜在包转发操作图上的一个节点表示。PFE根据单个数据包的类型/字段,为其执行一系列操作。瞻博网络高级转发接口(AFI)[3]提供了部分可编程性,允许第三方开发者通过一个称为沙盒的小型虚拟容器控制和管理这个转发路径图的一部分。该沙盒使开发者能够添加、删除和改变特定数据包的操作顺序。

04

Trio用于网络内遥测。大多数网络运营商需要遥测或深入了解其网络中的流量,以便进行容量规划、服务级协议监测、安全缓解和其他用途。目前的网络设备通常依靠数据包采样,使用设备中嵌入的内部处理器或外部监测设备进行进一步处理。由于通过设备的流量很大,而可用于监测的处理和带宽有限,只有一小部分数据包(几万分之一或更少)被选中进行监测,而且采样数据包的决定往往是盲目的,基于一个简单的时间间隔[62]。Trio的数据包处理的灵活性和操作资源的可用性使其适合网络内遥测。例如,服务提供商可以利用Trio的大内存来跟踪传入的数据包,以保持足够的信息用于遥测。此外,Trio的定时器线程适用于定期监测和异常分析。为了给网络运营商提供更智能的遥测,可以根据Trio已经提取的用于路由的数据包字段,对每个数据包执行基于机器学习的分类技术。最后,数据结构可以更有效地存储,从而减少外部监测设备的传输带宽和处理周期。

Trio用于网络内安全。为了减轻DDoS攻击,基于Trio的MX系统支持识别和丢弃恶意数据包的功能,充分利用了芯片组的高性能和灵活的数据包过滤机制。Trio还在SRX安全平台上充当基于安全流的快速转发路径[1]。Trio能够对传入的数据包进行额外的复杂的网络内安全处理,通过聚合特征或对服务提供商安装的ML模型进行推理,以识别和缓解流量中的异常情况。与基于设备的解决方案不同,Trio在网络数据通路上进行异常检测的可编程架构可实现低延迟的威胁缓解。

Trio-ML中的数据包丢失。运行各种不同应用的数据中心可能会出现瞬时流量高峰,而这又可能导致聚合数据包丢失。一个实用的网络内聚合系统需要一定程度的弹性,使长期运行的工作能够在这种突发事件中生存下来。SwitchML[63]建议如何实现这种弹性。Trio-ML的实现有支持这种解决方案的规定,尽管它不是当前代码的一部分,我们把它留给未来的工作。

未来的开放源码计划。我们正在考虑几个未来开源的想法。首先,我们计划为Trio增加对P4编程的全面支持。Juniper工程公司已经为实现这一目标做出了初步努力[6],但最近对P4核心规范的修改和增强,应该可以让更多的灵活性和更多的功能通过P4接口公开。其次,我们计划创建一种特定领域的语言,让第三方开发者能够使用Trio芯片组的全部转发路径功能。瞻博网络正在探索这一领域的发展,并欢迎社区提供反馈。

05

使用可编程交换机的网络内计算。之前的几篇论文通过利用网络内部的某种形式的可编程性提出了网络内计算。这些方法分为两类:(1)使用基于PISAb的架构进行线速计算[18, 48, 63];(2)使用片上FPGA进行亚线速计算[21]。我们的网络内ML聚合用例与Sharp[18]、SwitchML[63]、ATP[48]、PANAMA[36]和Flare[29]密切相关。Sharp[18]是Mellanox针对专用ML训练集群的专有设计;它假定网络带宽可以被完全保留。相比之下,我们考虑的是多个用户和应用共享链接的网络。SwitchML[63]和ATP[48]使用市面上的Tofino交换机来执行梯度聚合。尽管Tofino交换机可以进行线速数据包处理,但其流水线结构的可编程性较为有限,这使得网络内的散兵游勇缓解极具挑战性。我们使用SwitchML作为Trio-ML的基线比较。对于我们的用例来说,SwitchML是一个苹果对苹果的比较,使其成为比ATP更合适的基线。更具体地说,ATP的性能改进受到网络内聚合和额外的参数服务器的影响,而SwitchML和Trio-ML更相似,因为这两种方法只使用交换机/路由器进行聚合。PANAMA的[36]网内聚合硬件可以支持灵活的数据包处理,但它是基于FPGA充当线内颠簸,使得它在大规模部署中不切实际。然而,本文旨在利用Trio的可编程架构,从头开始设计新的有状态的网络内应用。Trio的几个关键特征使这些新的应用成为可能。首先,Trio的大内存和对数据包尾部数据的快速访问使网络内的高效计算成为可能。其次,Trio的共享内存系统提供了几GB的存储空间;即使在有散兵游勇的情况下,或者在多个应用程序同时运行的情况下,这也足够用于数据存储。最后,Trio对单个数据包的指令数量没有限制,使Microcode程序能够启动大型数据包所需的计算指令。

缓解散工问题。在理解和缓解分布式系统中散工问题的影响方面,之前有大量的工作[13 15, 25, 26, 30, 31, 33, 34, 38, 46, 51, 56, 57, 59, 61, 72, 75, 78, 79] 。特别是,Harlap等人提出了FlexRR,以减轻散工问题对分布式学习工作的影响[38]。FlexRR要求工人之间进行点对点的通信,以检测速度慢的工人并进行工作重新分配。相比之下,我们考虑在网络内部减轻散兵游勇的影响,不需要工人之间的任何消息传递,也不需要参数服务器。Tandon等人[72]和Raviv等人[61]提出了编码理论框架,通过在工人之间重复训练数据来缓解分布式学习中的散兵游勇;然而,Trio-ML不需要数据重复。

替代传统交换机架构。研究界一直在研究替代的交换机架构,以解决基于PISA的架构的一些限制,如缺乏共享内存和浅层流水线深度。最有竞争力的例子是dRMT(Disaggregated Programmable Switching)[24]。dRMT开关架构实现了一个集中的、共享的内存池,所有的匹配动作阶段都可以访问。dRMT不是在一个流水线上执行匹配动作阶段,而是将这些阶段聚集在一个集群中,并以轮流的顺序执行。一个控制逻辑单元对这些阶段进行调度,以便在尊重程序依赖性的前提下最大限度地提高集群的吞吐量。然而,集中式内存池由一个连接各阶段和内存的多路复用器控制,在一个给定的时钟周期内,只有一个阶段可以访问内存。当一个应用程序需要在多个阶段访问内存时,这可能导致程序执行速度减慢。在Trio中,多个线程可以在同一时间向同一内存位置发送内存访问请求,Trio的读-改-写引擎依次处理这些请求,保证了更新的一致性。此外,dRMT通过crossbar的内存访问是在编译时调度的,这降低了增量更新和重新编译应用程序代码的灵活性。横杠调度算法的复杂性会限制该架构扩展到更多数量的匹配行动处理器的能力。相比之下,Trio的crossbar是实时调度的,从而提供对内存的有效访问。这种动态调度机制使Trio能够从第一代的16个PPE扩展到第六代的160个PPE,而且将来还会继续扩大规模。此外,在dRMT中,数据包解析器和分离器位于匹配动作处理器之外。对依赖查找结果的数据包的内部头的任何解析(例如MPLS封装的数据包)都必须重新循环到解析器中进行处理。相比之下,Trio的PPE是完全可编程的处理器,能够以运行完成的方式处理数据包解析/分离,以及其余的数据包查找和处理。Trio的多线程PPE还允许数据包由不同的Microcode程序根据其处理要求进行处理。

06

THE END

翻译:董菁 图文排版:潘伟涛

责任编辑:刘欢 潘伟涛