现有一块ADC连接到FPGA上,需要在FPGA上实现高速数据的读取,那么第一步自然就是完成可靠的硬件连线,其中需要注意的是:

1. 注意信号的完整性,尽可能的避免边沿退化;这两区分两个概念:

i. 高速信号,指的是信号翻转,由高电平到低电平或者反之所耗得时间非常小;可能一个1MHz的TTL信号或者LVDS信号,只要边沿足够陡,那也算是高速信号!

ii. 高频信号,一般指的是周期性信号的周期时间足够小;

iii. 也就是说高速信号不一定是高频的;数字信号一般都是高速信号,所以必须要保证其边沿的完整性,如果边沿发生退化或者变形,那么将相当于加入了额外的时序上的偏差;

2. 保持时钟信号和数据信号路径等长,不管是单端还是差分信号,需要用绕线等形式迫使两类线几乎等长;这个在之前的时序分析中非常重要,如果真的不能够做到等长,甚至差的还挺多的,也必须提前获得该差值,并将则合成时间差,在后面的时序分析中将会有用;

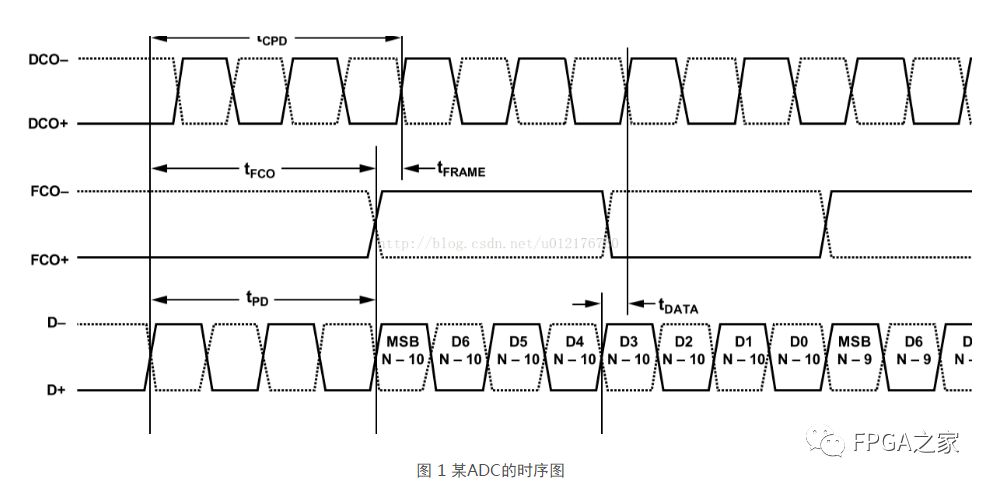

保证以上两点后,就可以着手时序的分析了,那么首先我们会得到目标器件ADC的时序,如下图所示:

图 1 某ADC的时序图

从上图中我们首先得到几个信息:

1. 这是个同步时序,由两类信号组成,时钟信号DCO和数据信号FCO以及D(忽略它们是差分信号,下面的分析会把它画成单端信号,简化好画一点)

2. 这是个DDR信号,DDR指的是数据是同步于时钟信号的上升、下降边沿,所以该类同步信号需要引入虚拟时钟概念,后面继续介绍;

3. 信号是不是边沿对齐,而是偏移了90度!也就是说DCO边沿翻转后,数据信号没有第一时间翻转,而是延后了四分之一个周期,这是高速信号惯用的伎俩,后面会发现,这个延时让时序更好分析;

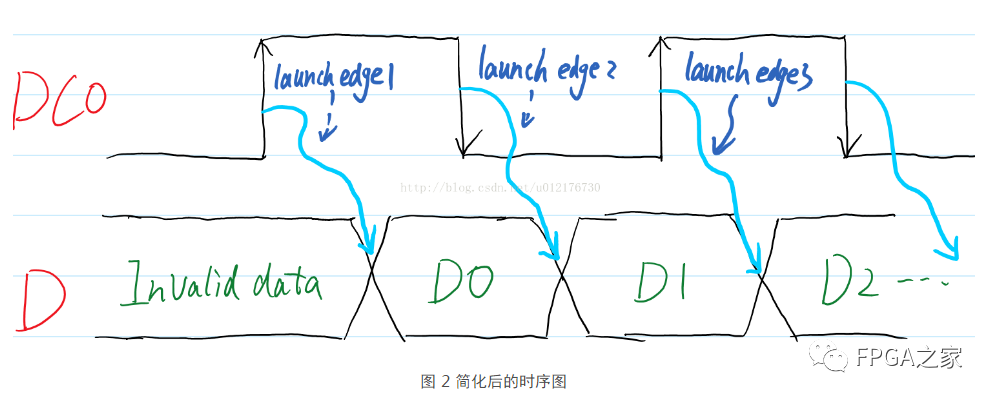

将FCO信号和D信号的实际意义扔一边,在设计者看来,他们都仅仅是数据而已,将上面的时序图简化成下图:

图 2 简化后的时序图

可以看到,实际上所有的数据信号都是同步于DCO的边沿,但是并不是对齐的,而是相差了90度,同时还是个DDR系统(上下边沿都是Launch Edge)

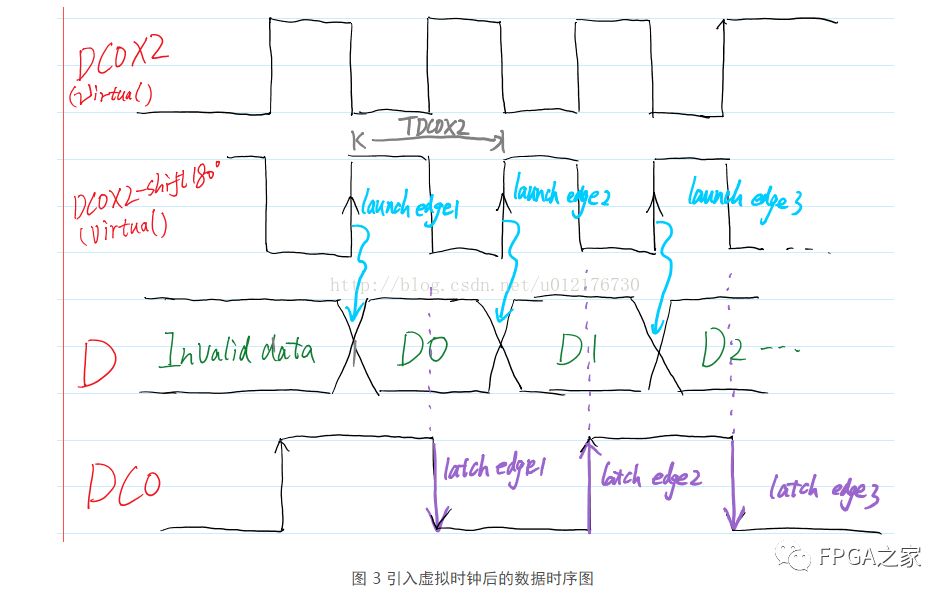

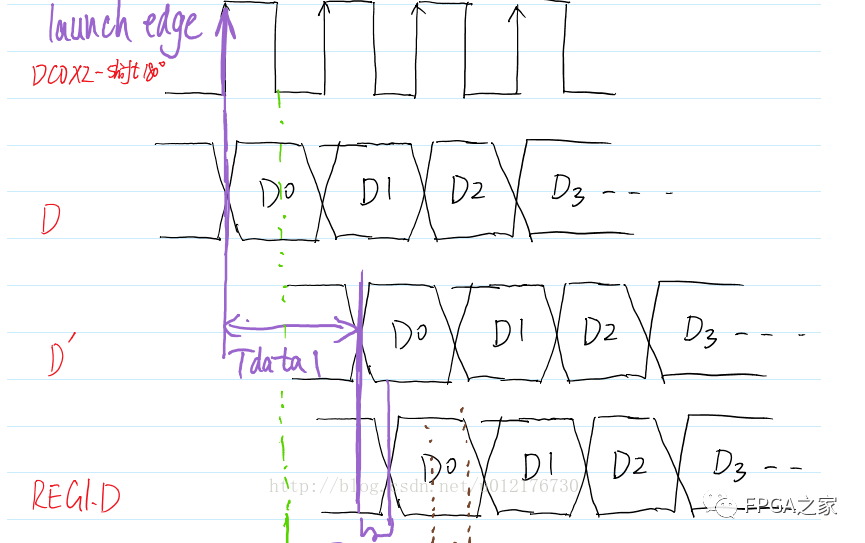

一般来说DDR系统会引入一个虚拟时钟的概念,就是说DCO是实际存在的时钟,设计和虚构出一个2倍频的DCOX2时钟,并将其相移180度以后,我们重新得到了下图:

图 3 引入虚拟时钟后的数据时序图

引入虚拟时钟后,我们重新规划Launch Edge,将其规划到DCOX2-Shift180的上升沿,其所对应的的Latch Edge仍然还是在DCO上。

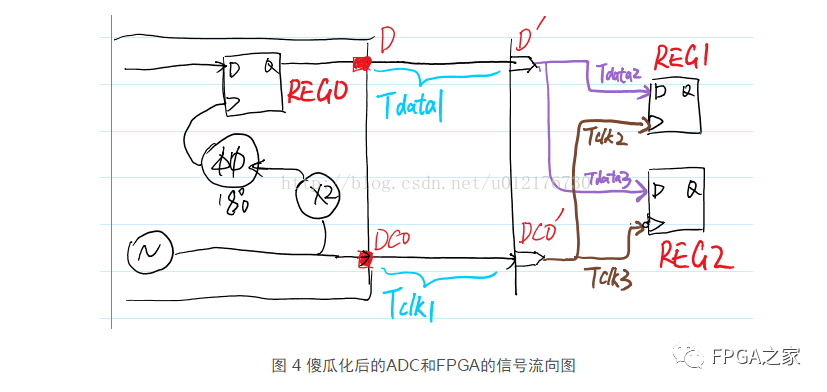

到目前为止,我们已经很清楚的规划了ADC的时钟和数据输出的关系,至于如何用SDC语言描述,见下文;接下来就要考虑到这些信号实际上是各自经过PCB走线后来到FPGA的引脚,从FPGA引脚由进入到FPGA内部,然后又经过各自的FPGA内部走线延时以后来到了他们目标的寄存器,如下图所示:

图 4 傻瓜化后的ADC和FPGA的信号流向图

从上图可以获知:

1. ADC内部看起来有一个源时钟,这个源时钟我们不用管怎么产生,它分成了两路,其中一路经过倍频+移相后触发了ADC上的REG0(就是说其上升沿作为Launch Edge),另一路直接输出到ADC引脚DCO;

2. 数据由REG0产生后输出至ADC引脚D,经过一个延时后来到FPGA的相应输入引脚D`,与此同时,DCO引脚也经由PCB来到了FPGA的输入引脚DCO`;

3. 这两个信号进入FPGA后,都各自分成了两路,分别经过各自的延时来到其目标:

a) DCO`引脚输入后,进过TCLK2,来到了REG1的clk引脚

b) DCO`引脚输入后,进过TCLK3,来到了REG2的clk引脚

c) D`引脚输入后,进过Tdata2,来到了REG1的D引脚

d) D`引脚输入后,进过Tdata3,来到了REG2的D引脚

4. REG1和REG2有所区别,一个是上升沿触发,一个是下降沿触发(clk前加了个小圈圈),这是因为latch edge本来就是上升沿又有下降沿的;后期实际上也可以给DCO`也引入虚拟时钟,这里不表;

5. 不管是REG1还是REG2,想要锁存latch数据就必须满足建立时间和保持时间,这个在下文的图中也有所体现;

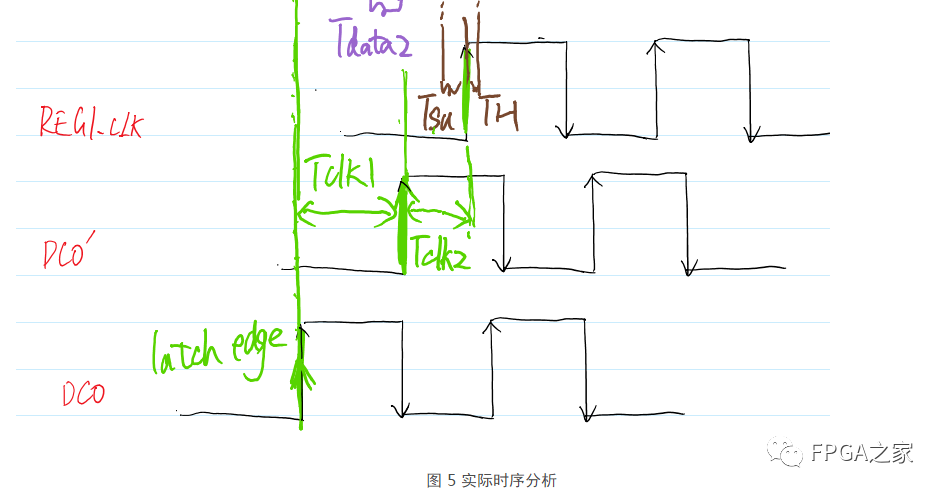

说了那么多,都不如实际的时序图来的实际,下面放图:

图 5 实际时序分析

上图由三个颜色的时序,分别是:

1. 紫色代表DAT,也就是数据到达时间,它由Tco(图中没有体现,可以参考手册)、Tdata1和Tdata2三者构成,是不是和我们的DAT定义不一样?公式是死的,只需要理解其意思就可以。和公式相比少了Tclk(源时钟到REG0的clk的延时),是因为我们不需要考虑这个延时,我们是根据ADC数据手册的时序图反推回里面的结构图,所以所有延时在反推的过程中已经都被体现或者被折合!

2. 绿色伙同棕色线,表达出两个意思DRTsu和DRTh,分别代表数据建立所需时间和数据保持所需时间;

3. 将两者按照定义做减法,就能够得到建立时间裕量和保持时间裕量!

如上图所示,棕色线所划分的时间窗中,REG1.D已经是新的数据,而且在这个时间窗内并没有变化,所以就同时满足了建立时间裕量大于0和保持时间裕量大于0两个关系,这样的时序是稳定的!

但是这个只是图示而已,所有的Tdata1、2、3以及Tclk1、2、3都是我们目前假设的,在实际进行约束时,那些量时需要设计者提前设定,而那些量是自动生成的那?答案是:

1. Tdata1和Tclk1是由PCB实际布线所决定的,如果能够按照等长布线规则,就能够让两者相互抵消;

2. DCO和DCOX2-shift180的时序是由器件决定的;

3. Tdata2、3,Tclk2、3是FPGA在布线时自动产生的!

所以说这里我们只需要告诉FPGA,DCO`和D`之间的时序关系就可以了,要获得这两者之间的时序关系,我们就必须获得DCO和D之间的原始关系,以及他们是如何被布线延时变成DCO`和D`的;如何去描述上面所说的这种关系呢?利用SDC文件!

也就是说SDC文件就是要准确的告诉FPGA,所有输入(输出先不管)信号在进入FPGA时会是个什么样子,然后根据这个信息,FPGA会自动布线,使得REG1和REG2能够获得正确的数据;如果万一SDC文件所描述的时序关系非常的恶劣,将会导致不管FPGA怎么优化布线和布局,都不能够实现正确时时序时,就会输出报错,这个在以后的文章TimeQuest TA中会有详细的分析;那么接下来就开始写SDC文件吧;

#设置各种延时常数

#这里假设ADC片上的延时都为0

set ADC_CLKs_max 0

set ADC_CLKs_min 0

Set ADC_CLKd_max 0

set ADC_CLKd_min 0

# 同时根据ADC手册去设置Launch edge到有效数据之间的延时,这里假设他为X

set ADC_tCO_max X

set ADC_tCO_min X

#这里设置时钟信号和数据信号在PCB板上的延时差,即使是等长布线,我们也要可以给

#定两个值,这样可以给FPGA布线更多的压力,使得后期布线会往一个最理想的方向进行,

#分别是

set ADC_BD_min XX

set ADC_BD_max XX

#设置两个时钟,第一个时钟为DCO,它会从FPGA的DCO引脚输入

#另一个时钟是虚拟时钟,根据设置,它是DCO的两倍频,而且有180度的相移

#这两个时钟之间是同步的,一个是很是存在的,另一个是虚拟的!

create_clock -name DCO-period 5-waveform {1.25 3.75} [get_ports {DCO}]

create_clock -name DCO_virtual-period 2.5 -waveform {0 1.25}

#最后将所有的数据引脚同步到DCO_virtual的上升沿,根据上面的延时常数设置输入延时和

#输出延时,这条语句非常关键,它告诉FPGA所有的输入信号,在进入FPGA之前,相对于

#时钟存在怎么样的关系!

set_input_delay -clock DCO_virtual -max [expr $ADC_CLKs_max + $ADC_tCO_max + $ADC_BD_max - $ADC_CLKd_min] [get_ports {D*}]

set_input_delay -clock DCO_virtual -min [expr $ADC_CLKs_min + $ADC_tCO_min + $ADC_BD_min - $ADC_CLKd_max] [get_ports {}D*}]

SDC文件解释

1. 蓝色底部分代表定义一些延时参数,这些延时参数都是根据实际的PCB布线或者是ADC的书籍参数来设定的

2. 绿色底部分设定同步时钟,如果有必要的话还要设置虚拟时钟;

3. 紫色底部分将所有的输入信号同步到时钟,在这里这个时钟是虚拟时钟,因为我们假设虚拟时钟的上升沿是launch edge,这里其实可以也可以同步到DCO上,但就要设置下降沿同步,会显得比较麻烦;但是一样都是可以实现的!

通过上面的语句,FPGA就知道了,这些属于信号之间的关系:D和DCO之间的关系,D和DCOX2-shift180(就是DCO_Virtual)之间关系;

推荐阅读

(点击标题可跳转阅读)

嵌入式系统词汇表

【Linux设备驱动】系列汇总,我写了什么?

【24小时学通Linux内核】系列,你想知道的都在这里