概述

JESD204B分层

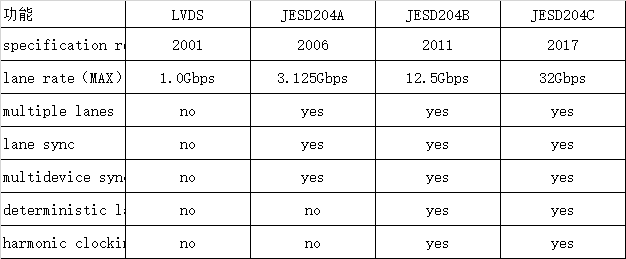

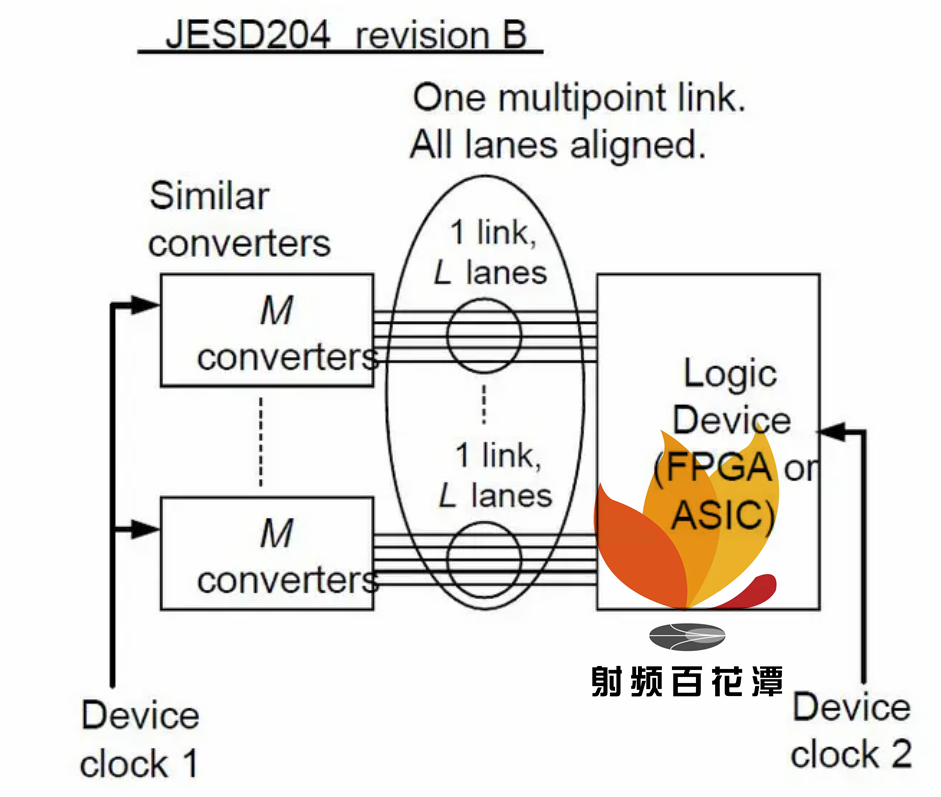

当前应用最普遍的为JESD204B,204B又分为子类0、子类1、子类2 ,这是根据同步方式划分的,比如子类1通过SYSREF进行同步,子类2根据SYNC来同步,目前采用较多的为子类1,并且只有子类1和子类2才支持确定性延时。

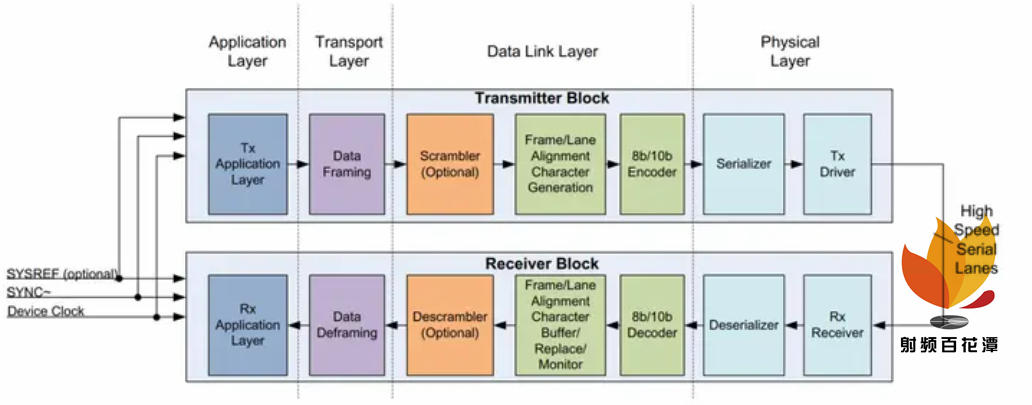

如上图所示,JESD204B分为四层介绍,分别是物理层、数据链路层,传输层和应用层。

//

1、物理层用于以特定速率发送和接收数据;

2、数据链路层用于8B/10B编解码和帧、lane数据对齐;

3、传输层用于数据组帧或解帧;

4、应用层用于链路配置和数据映射。

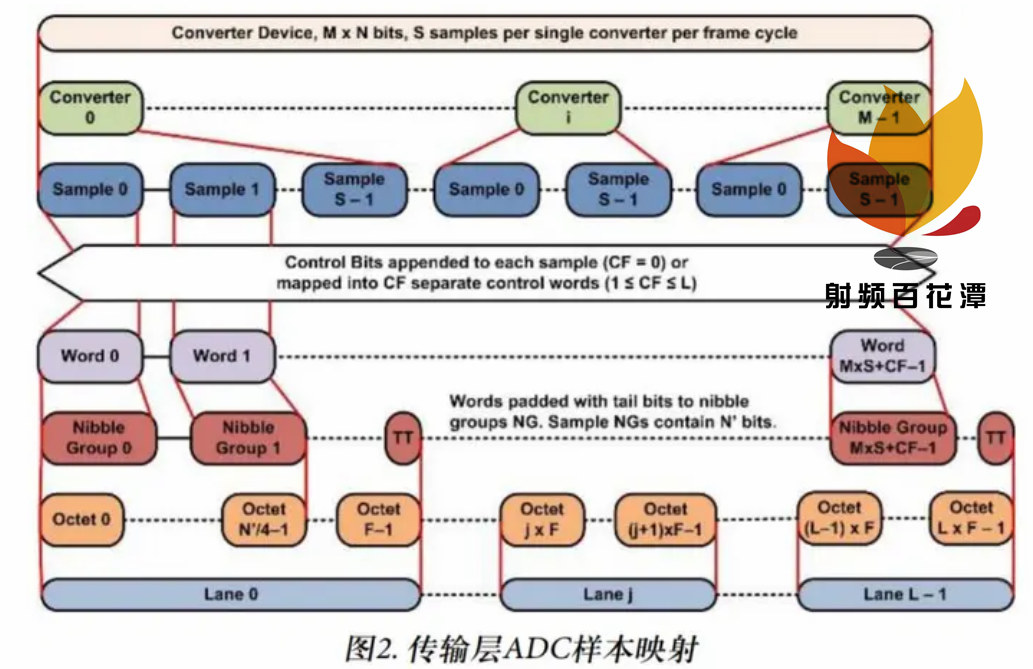

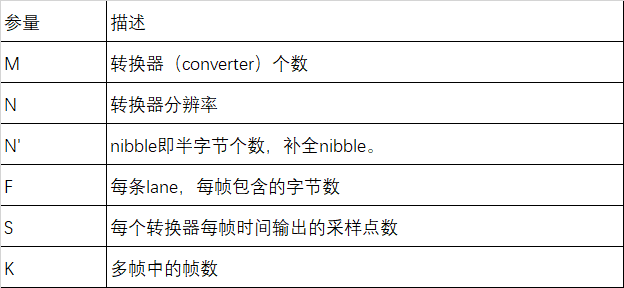

一、传输层

二、数据链路层

//

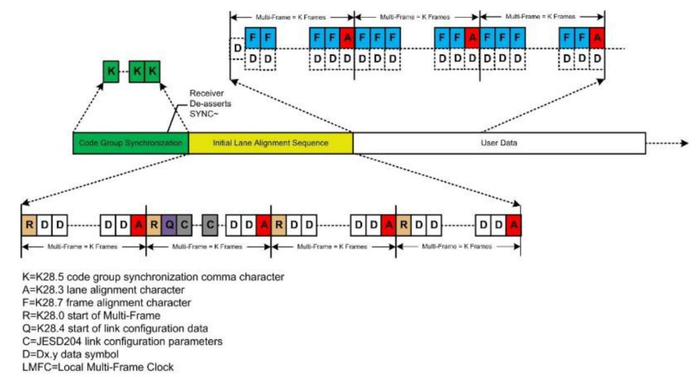

1) 代码组同步(CGS):

在代码组同步(CGS)期间,一旦在所有链路通道上检测到某一数量的连续K28.5字符,FPGA就会送至ADC的SYNC信号。在JESD204B中,ADC捕捉到SYNC信号的变化,就会在下一个本地多帧时钟(LMFC)边界上启动ILAS。

2) 初始通道对齐序列(ILAS)

ILAS的主要作用是对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。ILAS由4个或更多多帧组成。各多帧的最后一个字符是多帧对齐字符/A/。第一、第三和第四个多帧以/R/字符开始,以/A/字符结束。第二个多帧包含/R/和/Q/字符,随后是链路参数。/Q/字符表示之后的数据是链路配置参数。

3) 用户数据

CGS和ILAS阶段完成后,发送器开始送出ADC数据。在这一阶段,用户数据根据ADC中定义并转发到接收器(FPGA)的链路参数,以流形式从发送器传输到接收器。;并且如果需要,通过数据链路中的字符替换可以监视并纠正帧和通道对齐,字符替换在帧和多帧边界处进行。

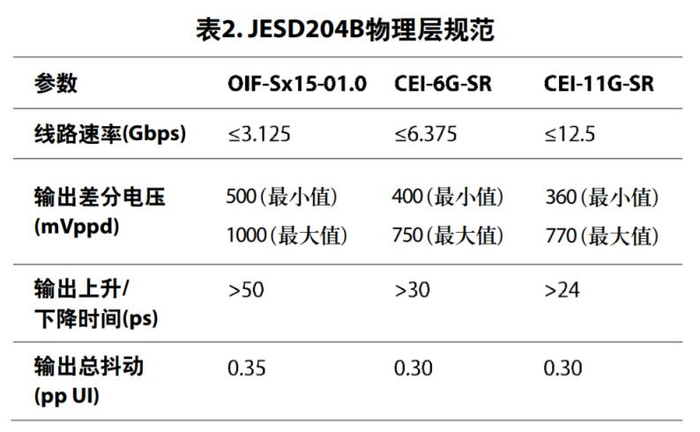

三、物理层

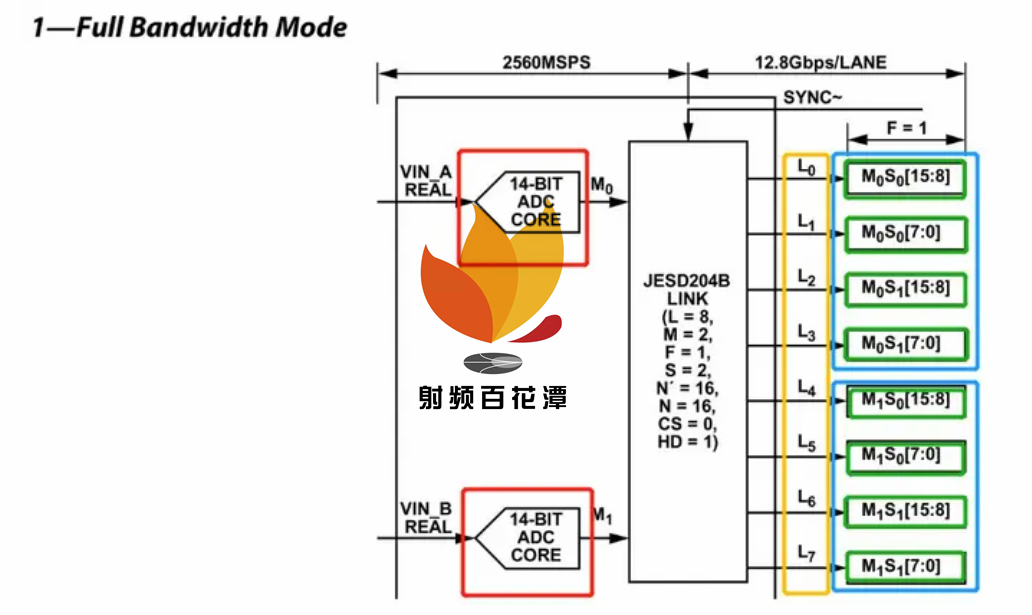

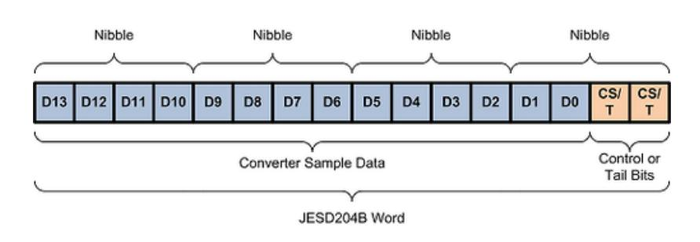

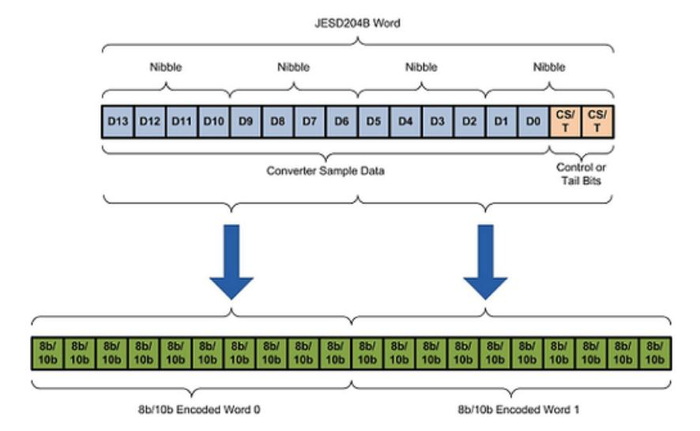

①lane rate=(MxSxN’x10/8xFc)/L;帧时钟:Fc=Fs/S,乘以N’即补齐nibble部分用控制字填充。

乘以10/8即编码部分。

lane rate计算对选择FPGA具有重要意义,JESD204B支持速率高达12.5Gbps,但最终工作在何种速率取决于使用哪种FPGA,FPGA GTH/GTX收发速率有上限,不同FPGA支持速率不同。因此参数决定的lane rate和FPGA选择需要进行权衡对比哦。

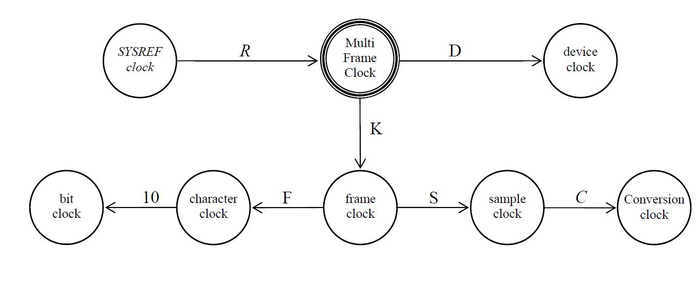

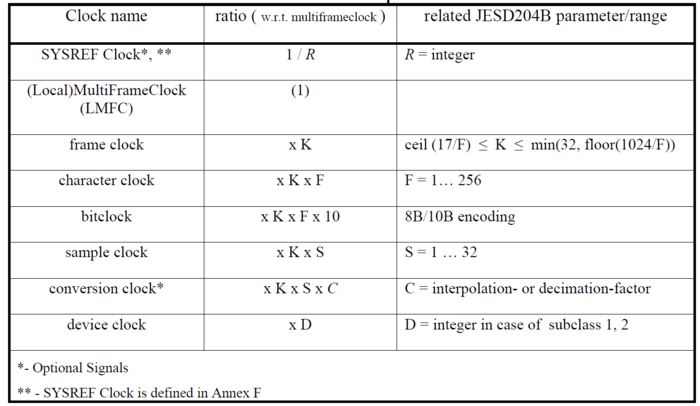

在JESD204B协议中,各个时钟之间的关系如下图所示:

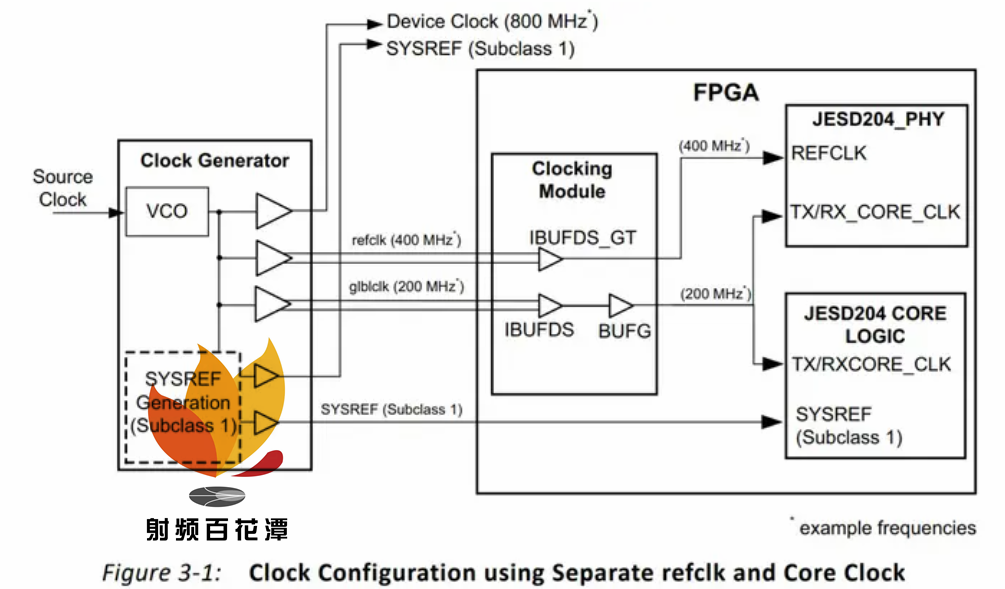

然而在实际应用中,硬件上需要外部提供给ADC和FPGA的时钟如下所示:

//

1、SYSREF:参考时钟,同SYSREF TO ADC;

2、GLBCLK:204B核时钟,Fglbclk=lane rate/40;

3、REFCLK:GTH参考时钟,时钟频率可选;

4、DEVICE CLK:ADC设备时钟;

5、SYSREF:ADC参考时钟;

总结

声明:

投稿/招聘/推广/宣传 请加微信:15989459034