文︱BRIAN BAILEY

来源︱Semiconductor Engineering

编译 | 编辑部

长期以来,IP设计市场日新月异,新兴技术的演进与迭代不断加速,异构集成与Chiplet逐渐成为全新的行业发展方向。与此同时,新技术的出现也为行业带来了全新的挑战。对于企业而言,若想要在这一领域获得市场主导权,就必须更加灵活高效,引入更多潜在标准,并对各种形式的集成深度探索,以满足复杂多变的市场需求。

从市场的角度来看,两大领域分类对技术的要求各不相同。首先,对SoC进行分解,并利用多种制造技术完善功能模块性能。其次,可以将外购的Chiplet集成至一个封装内,而不是将这些功能集成到电路板上。

SoC分解

虽然摩尔定律在技术意义上仍在延续,但其经济意义已经逐渐衰退。鉴于此,业界正全力探索延续摩尔定律的可能性,包括将功能分散到多个芯片上,然后在封装上集成这些芯片。

这可能会让AI加速器架构更具可扩展性,其中处理模组不再受限于标线大小。“为什么要拆分SoC?”Synopsys产品营销总监Mick Posner表示。“或许是裸晶片尺寸达到了理论极限,或许是想要扩展处理器单元或AI单元。这就需要将更成熟的技术应用于部分设计中。所有这些可能性都为全新IP设计带来了巨大的潜在机遇。从根本上说,只需设置额外的接口将其连接起来。”

这些接口将影响功耗和性能。“异构集成允许公司集成标线尺寸不一的设备,但如果可以在单个芯片中做到这一点,那么肯定会获得最高的性能和最低的功耗。”西门子EDA高级封装解决方案总监Tony Mastroianni表示。“但你只能走这么远。一旦你击中了光罩大小,你就击中了它。如果你看看一个AI处理器,那些通常通过有多个芯片连接到电路板来扩展。这些电路板连接需要长距离的SerDes。一个有趣的建筑是有瓷砖。它们可能是光罩大小,您可以构建这些阵列,而不是在电路板上,而是在大型转接板上构建这些阵列。一些有机转接板技术允许更高水平的集成。”

虽然这些图块今天可能安装在转接板上,但将来它们可能是3D图块。“一个广泛的异构集成生态系统将使摩尔定律回到正轨,同时提高灵活性和产量,”Fraunhofer IIS自适应系统工程部高级混合信号自动化集团经理Benjamin Prautsch表示。“从这个意义上说,IP优化和定制并不一定相互矛盾。但重点将更多地转移到封装设计层面,以及接口的标准化。后者可能需要在明确定义的限制内具有灵活性,这将推动新的EDA方法,特别是编程生成器方法,以便快速开发接口IP。”

虽然一些接口标准正在出现,但很明显,还需要更多标准。“许多Chiplet标准、通信协议和围绕这些标准的IP,如UCIe,都是为了从芯片到芯片(D2D)的同质、高带宽速度和馈电,”在Movellus负责技术营销和品牌增长的Aakash Jani表示。“随着时间的推移,我们将开始看到更多的异构设计。并非所有内核都需要从芯片到芯片的高带宽通信。有些可能只需要较低的带宽。我们还必须了解这些通信协议中的开销,因为面积和功率开销的最大贡献者之一是时钟转发协议。随着IP公司开始走上这条道路,我们需要开始消除这些障碍,使D2D通信更节能,更省区域。然后,我们可以开始支持这些低带宽、低功耗、异构的Chiplet通信协议。”

虽然组件在板级的连接方式有限,但这些限制在SoC世界中已经被驳回。“在任何给定的SoC上,甚至在具有多个芯片的异构计算之前,即使对于普通的单片芯片,客户通常也会做许多互连实例,”Arteris IP首席营销官Michal Siwinski表示。“过去的旧概念是1个芯片,1个互连。现在情况已不再如此。即使在划分为多个Chiplet之前,SoC的平均互连也在5到7个互连之间。某些芯片可能有 20 或 30 个互连。因此,任何芯片上都有很多连接。带有Chiplet的异构计算和D2D连接基本上增加了一个额外的连接层。”

Chiplet集成

Chiplet是一种预先设计、预先制造,且可以集成到封装中的裸晶片。“Chiplet在许多不同的应用中已经存在了很多年,但我们正处于一个转折点,”Arm基础设施业务线产品管理高级总监Jeff Defilippi表示。“Chiplet可以通过超出光刻机处理的最小尺寸扩展来提高性能,同时仍然能够管理芯片成本。摩尔定律的放缓已经在业界讨论了一段时间,虽然先进制程节点(5nm及以下)可为逻辑提供优势,但片上系统(SoC)的I/O和内存组件的扩展速度已经明显放缓,这意味着更高的成本和更低的收益。整个行业都在创新和标准化方面持续投资,这些投入都将转化为更高的性能、更低的成本以及更广泛的应用。Arm期待看到一系列定制和标准化的实现,同时也期待利用Chiplet技术创造的全新性能点和独特的SoC产品。”

这就是分歧开始的地方。SoC能否负担得起固定功能部件?“当你有预制的Chiplet时,你会被锁定在这些设计规范中,灵活性就会降低,”Movellus的Jani表示。“你也被迫使用重型接口。垂直整合的公司可能会发现,使用简单的D2D通信协议可以削减大量开销,从而更容易、更节能、更省空间。UCIe的整个想法是为那些将要采购这些预制件,然后将其发送到封装厂将其组装在一起的公司创建这种标准化。”

但它们确实提供了其他形式的灵活性和效率。“随着Chiplet模式被广泛采用,并且价格越来越实惠,它将重振IP业务,”Mixel创始人兼首席执行官Ashraf Takla表示。“Chiplet可更为灵活地为IP选择最佳工艺,而不必将IP移植到最适合客户IC的特定工艺技术。如果单个Chiplet标准成为明显的赢家,作为Chiplet商品化的部分IP技术将逐渐成熟,其中包括桥式Chiplet。”

目前尚不清楚该平衡点将在哪里。“对于客户而言,拥有一个Chiplet市场的梦想并进军,发现一块准备就绪的芯片是有吸引力的,”Synopsys的Posner表示。“它已经过硅验证。这是一个已知的好裸晶片。然后,所需要的只是不同块的封装。阿喀琉斯之踵是Chiplet芯片,它是固定的,它的功能是已被定义好的,但这并不妨碍它需要优化。拥有可用IP市场的梦想将因不通用而陷入困境。”

在某些领域,这些优势相当明显。“有可能将迄今为止不切实际的功能合并到一个独立封装中,”Synopsys的DesignWare IP解决方案营销经理Scott Durrant表示。“像一个芯片上的逻辑和存储器,或者像电气设备一样在同一芯片上的模拟或光子电路,这些都是不切实际的。有了Chiplet概念,将这些东西放在一个独立封装中成为可能,看看行业在哪里抓住这个机会将是很有趣的。我们将能够在一个独立封装中放入一些有趣的解决方案,而这些解决方案在过去无法简明扼要或紧凑地提供。”

对于上市时间至关重要的公司,或者他们需要快速构建具有定义功能的芯片的公司,Chiplet可能正是他们需要的。“引入预先验证的模块的想法确实有助于加快设计速度,”Imperas Software的创始人兼首席执行官Simon Davidmann表示。“一些聪明的人可以制造出非常好的芯片,然后把它们授权给你,当你将其连接在一起时,它们就会起作用。通过这种方式,公司可以获得利益,因为IP业务的一大好处是它经过验证并且有效。您所要做的就是集成测试。”

对于今天作为硬IP块交付的某些块,它们可能没有什么区别。“我确实看到了一个广泛的基础,他们对使用不同组件的独立封装构建系统非常感兴趣,”西门子的Mastroianni表示。“SerDes就是一个很好的例子。可能需要非常高的带宽,128 gig SerDes,但这是一个昂贵的IP,它将决定一个非常昂贵的技术节点。如果需要高速带宽,并且如果Chiplet可用,这将为许多客户打开这种方法的市场。”

毫无疑问,这个行业离今天的完全标准化还有很长的路要走。“必须考虑Chiplet身份验证和潜在的数据路径加密,”Posner表示。“Chiplet必须具有分层可测试性,已知良好的芯片测试和维修,PVT传感器的生命周期管理以及围绕这些的基础设施。然后没有一种类型的包装技术。有先进的转接板和有机底物。您需要的是一个可定制的Chiplet解决方案。”

Mastroianni提出了一种可能性。“也许他们走了一段路。他们没有提供芯片,而是有一个贴出并准备就绪的GDS,他们只会许可该GDS。然后,集成商可以进行制造。这是他们需要做出的决定,而且可能是量驱动的。如果存在大批量零件,他们可能会更倾向于每件型号,而不是前期许可费,或者可能会有版税的运行率。这些商业模式真的会是新的,他们必须仔细考虑这一点。”

模型

然而,功能都是封装并交付的,无论是从第三方供应商还是在公司内部重用,都将需要一组新的模型来封装和抽象Chiplet。“客户正在寻求更好的IP封装和集成工具,”Agnisys创始人兼首席执行官Anupam Bakshi表示。“不幸的是,许多商业IP供应商没有提供足够详细的模型。我们正与国内外IP团队合作,力求开发出更好的设计和封装模型。”

已有标准组织正在研究这个问题。“Chiplet Design Exchange(CDX)是ODSA下的一个工作组,该小组的章程是提出一套标准化模型来支持生态系统以及工作流程,”Mastroianni表示。“CDX定义了与这些Chiplet一起交付的模型,以支持系统集成商。尽管这感觉是合理的,但这需要很多额外的工作。除了进入硅业务外,还必须创建这些模型。这需要着重考虑投资回报率,以确定这是否真正值得去投入。但不管它是不是现成的Chiplet,如果你正在研发异构集成,仍然需要所有这些视图。”

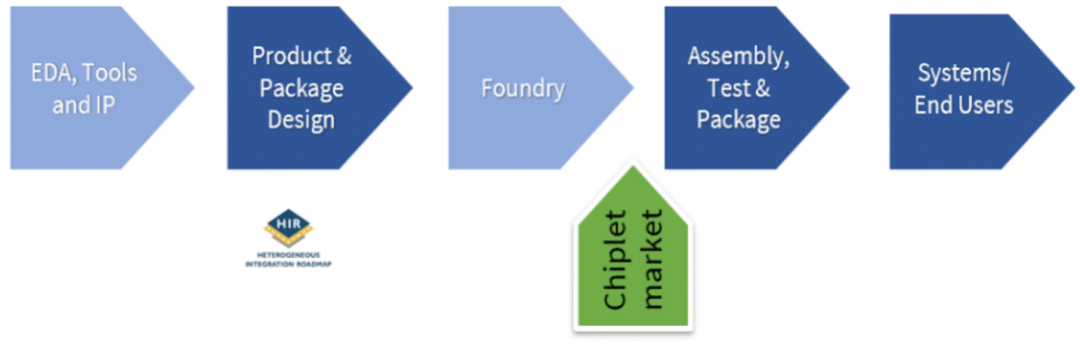

图:Chiplet价值链(图源:ODSA)

UCIe是最新宣布的Chiplet互连标准。“如果你看看UCI在其1.0规范中的内容,就不难发现这是市场上最全面的规范,”Posner指出。“该规范涵盖了大多数设计所需的全部数据速率,为原始流的延迟优化提供了多个协议级别,而且还增加了更高级别的PCIe、CXL,或者位于原始接口之上的任何其他协议。有些主题刚刚被标记为UCIe 2.0。例如,UCI主要面向2.5D中介层和有机基底,不过这并不包括3D。用于认证芯片的安全功能被视为UCI 2.0。我们可以期待该规范的快速发展。”

D2D互连还有许多其他标准。“D2D接口在很大程度上包括这些并行接口以及AIB、BoW和UCIe,”Mastroianni认为。“D2D接口拥有多种协议,HBI是另一种可用的协议。如果我们能够收敛于一个协议,那就太好了,但是对于那些实际上并没有推动性能提升的应用程序,可能需要不太复杂和成本更低的协议。此外,还可以使用可在许多工艺技术中实现的短距离XSR或USR(超短距离或极短距离)SerDes。XSR PHY的成本要低得多,而且不会规定将三到五纳米工艺用于定制设计。”

结论

从标准方面来看,哪一个标准能够发挥最大效果,形成完整完善的产业生态系统,推动芯片设计行业不断发展,仍需要时间来证明。

“也许是UCIe,也许是CXL,也许会出现其他标准,”Arteris的Siwinski表示。“无论哪种标准最终取得胜利,都不是问题的关键。最重要的是能够找到这种正确的标准,让设计人员能够将裸晶片缝合在一起,最终得到一个几乎同质的异构系统。对于从业者而言,对于整体半导体市场而言,这是需要面对的挑战,更是一个发展的机遇。”