来源 | 云脑智库

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢。

第五讲 有源微波电路

1.2 低噪声放大器

1.2.1 低噪声放大器的主要参数

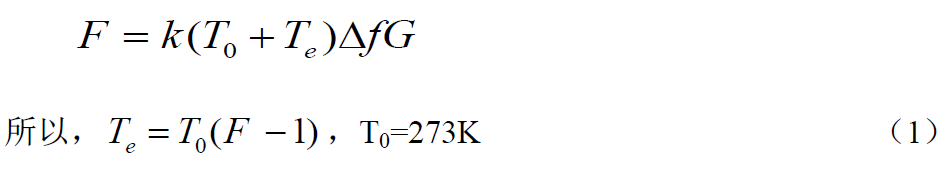

(1)噪声系数与噪声温度

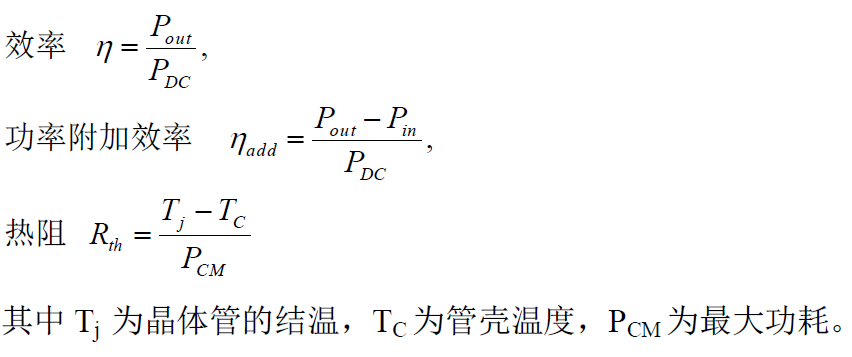

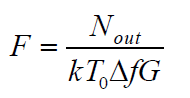

噪声系数定义为输入信噪比和输出信噪比的比值:

其中,Δf是放大器带宽,G是增益,k是玻尔兹曼常数。

如果接收机包含多级放大器,接收机的总噪声系数为

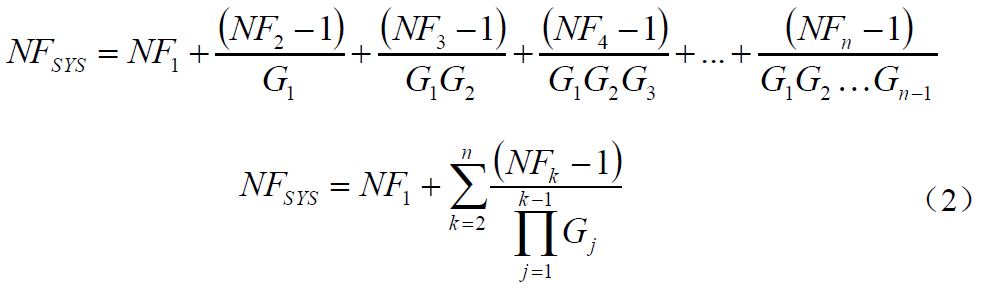

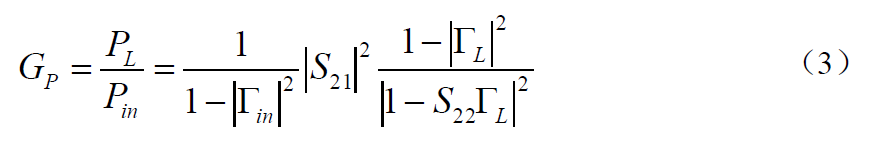

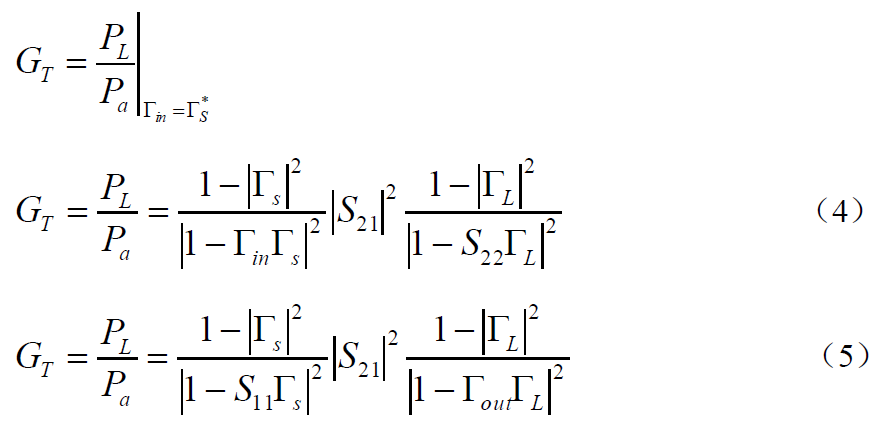

(2)增益

(3)驻波比:输入和输出端口匹配状态。

(4)工作带宽:增益、噪声系数等技术指标满足要求的工作频率范围。

(5)动态范围:最大和最小输入信号功率之比,并用dB 表示。

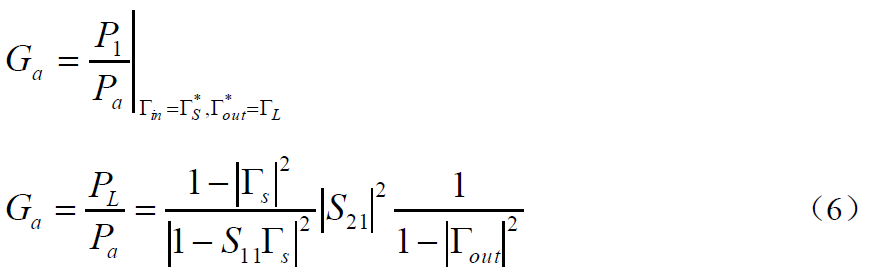

图1 P1dB压缩点和三阶交截点IIP3

1.2.2 低噪声放大器设计

(1)放大器的稳定性设计

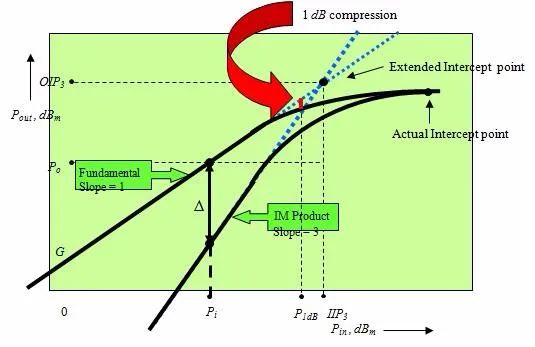

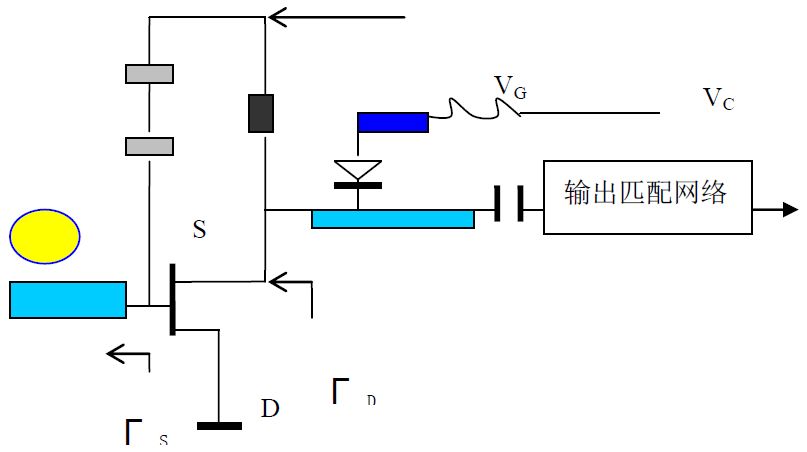

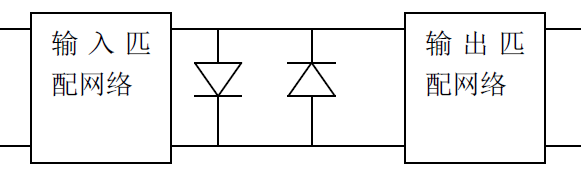

图2 放大器的等效电路

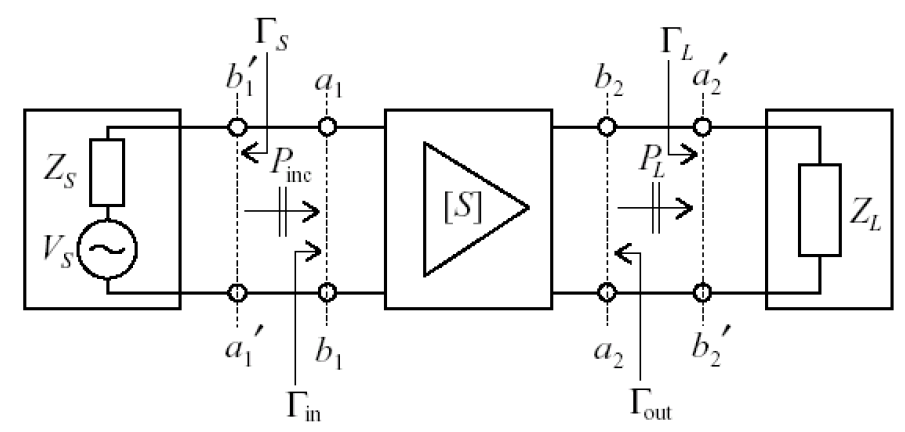

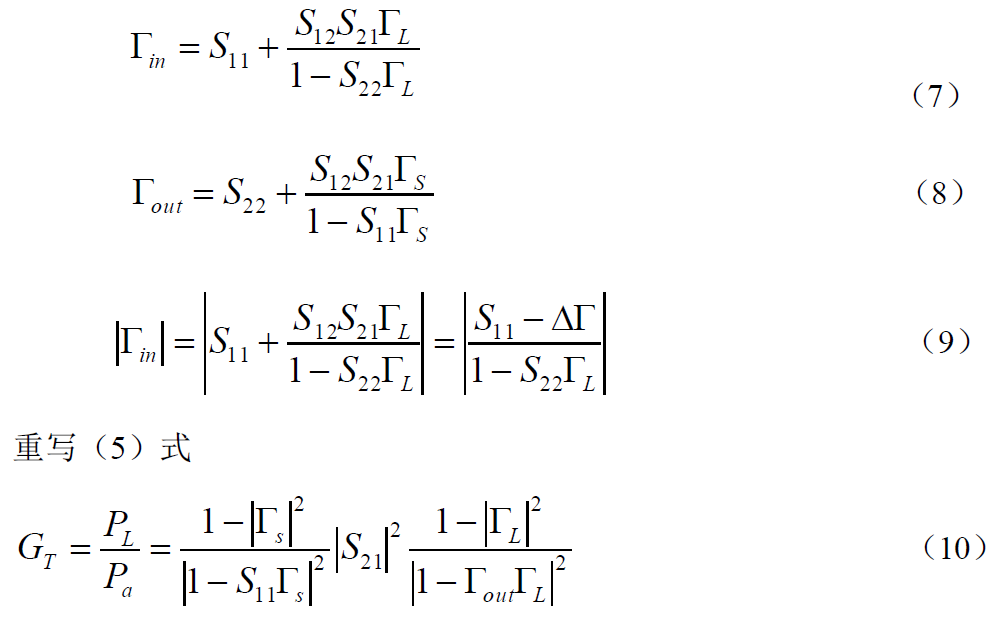

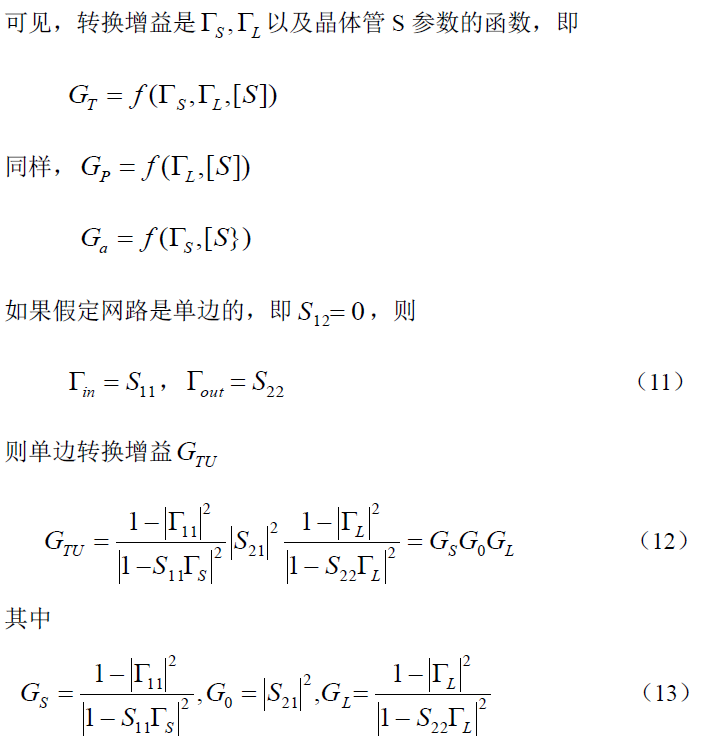

考虑到放大器输入输出匹配电路后的等效电路如图2 所示。其输入输出反射系数用晶体管的S 参数表示。

输入、输出反射系数:

其中,Gs,GL分别表示输入和输出电路的失配损耗。可见,放大器的转换增益通常小于由晶体管S 参数给出的增益。

对于二端口网络,无论是输出端还是输入端呈现负电阻,就可能产生振荡,此时,

对于单边放大器,对应于

也就是说,在给定频率,对于一切可能的源阻抗和负载阻抗的实部均大于零,该二端口网络就是无条件稳定的。对于某些源阻抗和负载阻抗,可能导致其实部小于零,则网络是潜在不稳定的。在给定频率,用反射系数表示的无条件稳定的条件是

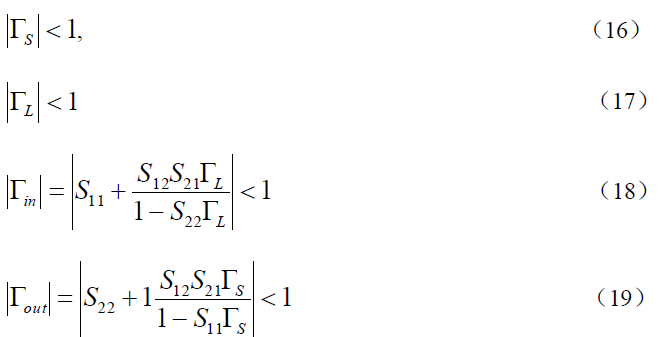

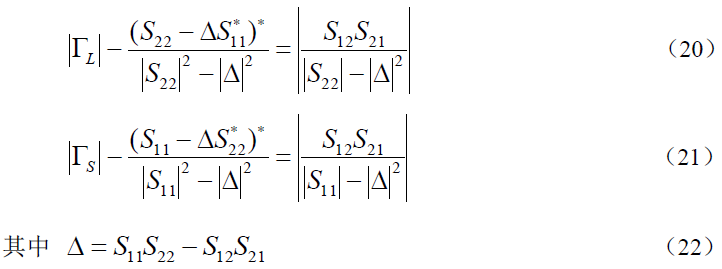

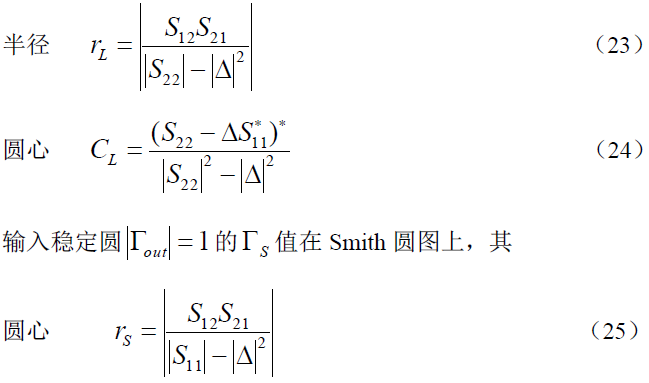

求解(16)-(19)可以得到无条件稳定所要求的条件。

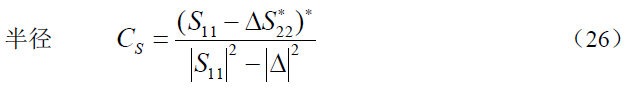

首先确定使|ΓL|=1和|Γs|=1的ΓL和Γs的值。令(18)和(19)式的模为1,解出ΓL和Γs,它们在一个单位圆上,称为稳定性圆。输出和输入圆的方程分别是

由(20)和(21)式可以分别得到ΓL和Γs平面上|Γin|=1和|Γout|=1的圆的半径和圆心。

输出稳定圆|Γin|=1的ΓL值在Smith 圆图上,其

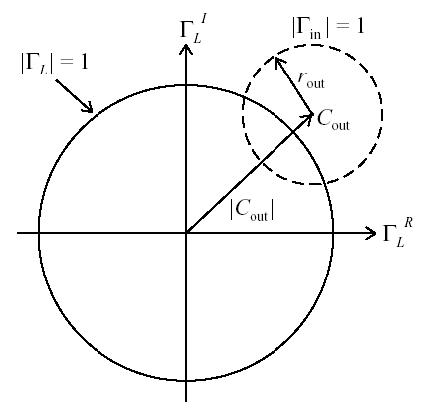

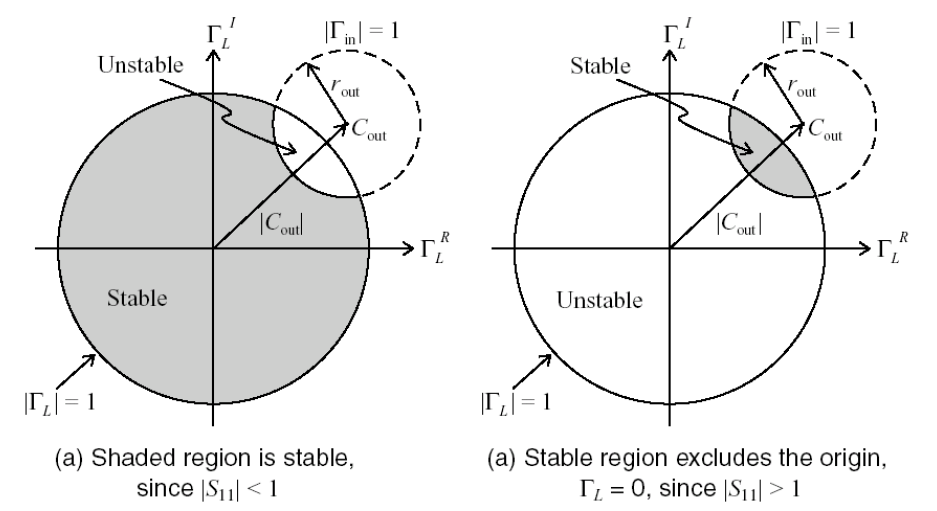

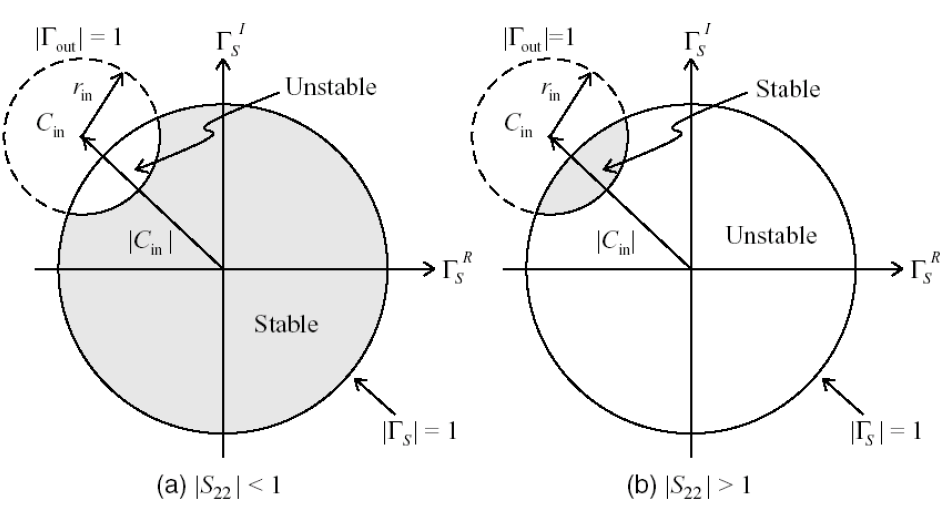

图3 表示当输入反射系数为1 时负载反射系数变化时的输出稳定性圆。|Γin|=1为临界圆,圆内为一个区,圆外为另一个区,前者是稳定的,后者是不稳定的。图5 中阴影区为输出稳定区。

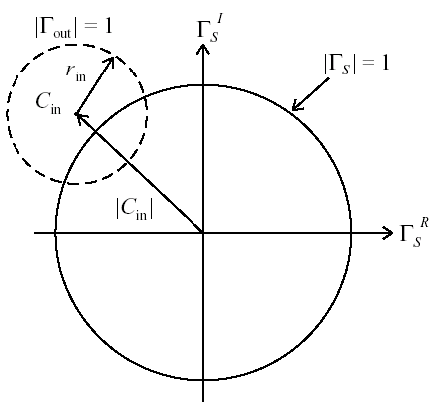

图4 表示输出反射系数为1时源反射系数变化时的输入稳定性圆。同样,|Γs|=1为单位圆,稳定区在单位圆内。|Γout|=1为临界圆,圆内为一个区,圆外为另一个区,一个是稳定区,另一个是不稳定区。图6 中阴影区为输入稳定区。

图3 放大器的输出稳定性圆

图4 放大器的输入稳定性圆

图5 输出稳定区与非稳定区

图6 输入稳定区与非稳定区

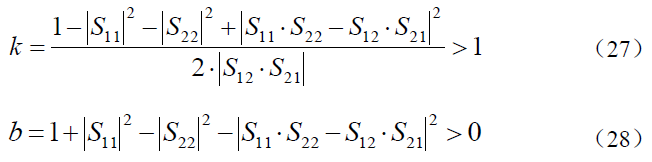

绝对稳定的充分必要条件:

当Rin<0, |Γin|>1, Rout<0, |Γout|>0 将产生振荡,放大器是不稳定的,称潜在不稳定。

当|Γin|<1; |Γout|<1放大器是绝对稳定的,即无论源和负载阻抗如何,网络都是稳定的。

所以,在输出平面上,绝对稳定条件是:

应当指出,所谓绝对稳定,仅仅是对阻抗而言,如果存在空间耦合等因素,放大器仍可能不稳定。

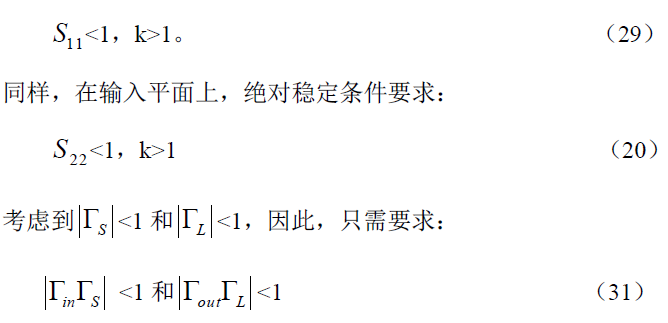

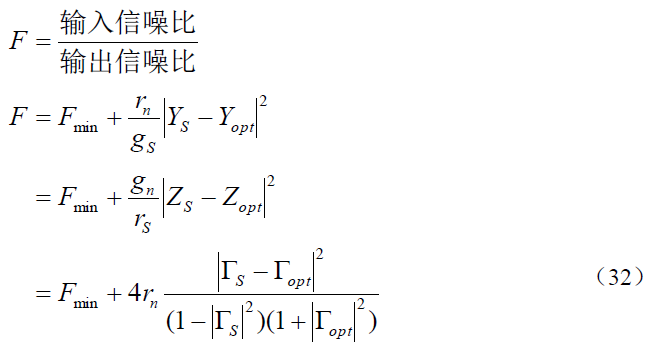

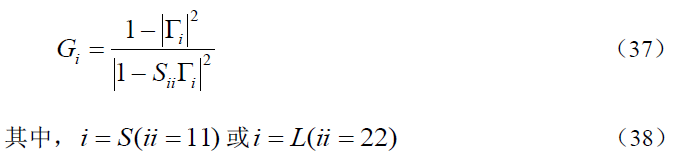

稳定放大器的措施:

可通过外部电路来提高器件稳定性。常用的方法是在输入输出电路中增加电阻,或者引入外部负反馈,例如在源极串联反馈阻抗。不过加电阻和负反馈在增加稳定性同时,会降低增益和增加噪声系数。

图7 输入接电阻稳定放大器

图8 输出端接电阻稳定放大器

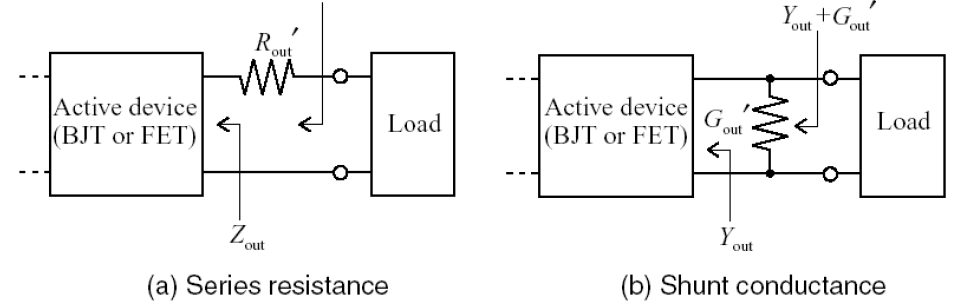

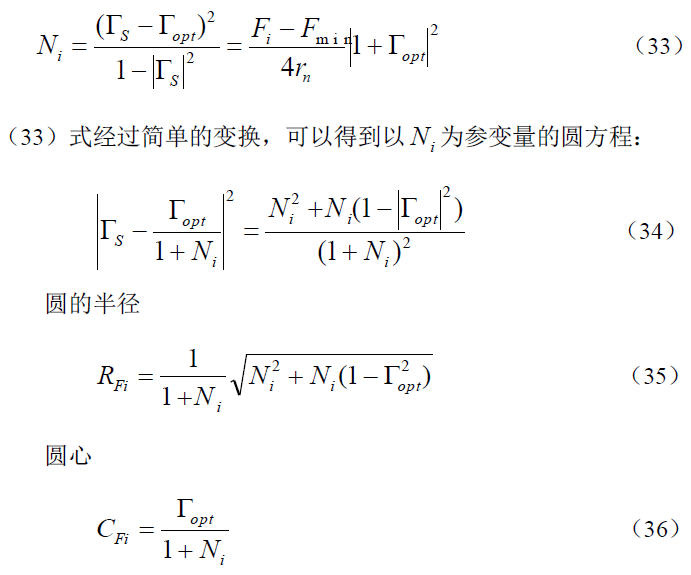

(2)放大器噪声分析

二端口网络噪声系数定义为

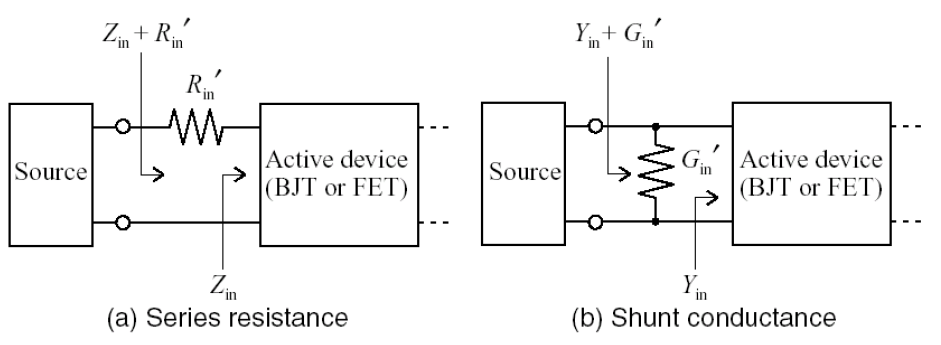

其中,rn是二端口网络等效归一化噪声电阻,Yopt是得到最低噪声系数的归一化源导纳,Yopt=g0+jb0,Ys=gs+jbs是归一化源电纳。rn,Yopt,Fmin称为噪声参数, Fmin是器件工作电流和频率的函数,给定噪声系数,可用(32)式设计Γs 。

对于给定噪声系数Fi ,定义一个噪声参量Ni

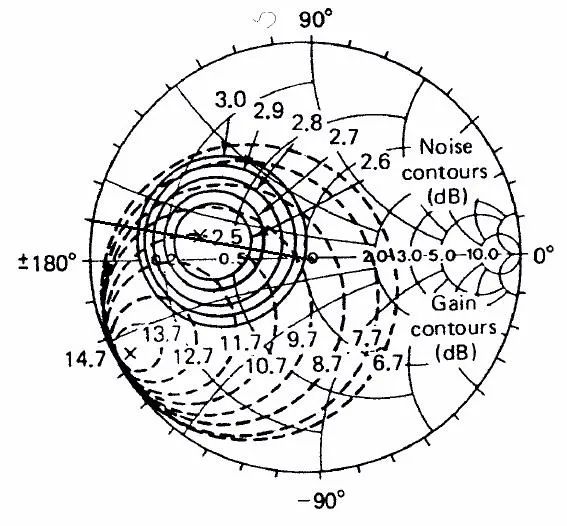

(33)-(36)式表明,当Fi=Fmin ,Ni=0,CFi=Γopt , RFmin=0,也就是说Fmin圆的中心在Γopt,半径为零,其余噪声系数圆的圆心在沿Γopt的矢量上,如图9,图中,Fmin=2.5dB 。

(3)等增益圆——单边情况

以单边放大器为例说明等增益圆的构成。由表示单边转换增益的(12)式的各项(13)式可见,Gs 和GL的形式类似,可以写成一般式:

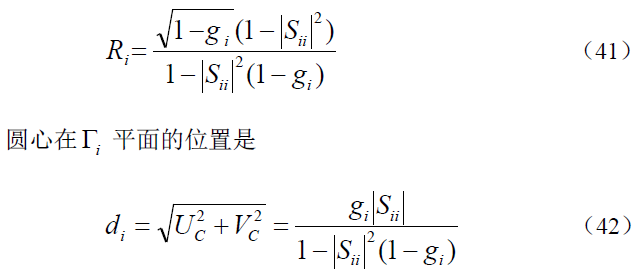

给定增益,可以基于(38)式设计放大器增益。仅讨论无条件稳定( |Sii|<1)情况。

图9 等噪声系数圆

(4)低噪声放大器设计方法可归纳如下:

1)分析稳定性;

2)计算等噪声系数圆;

3)计算等增益圆;

4)选取合适的源反射系数;

5)选取合适的负载反射系数。

图10 Smith 图上的等增益圆

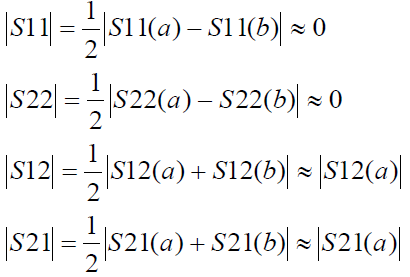

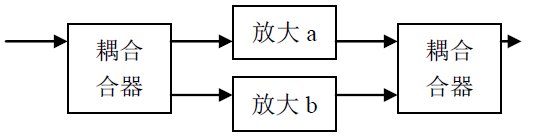

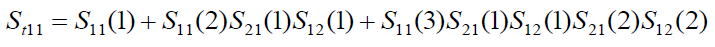

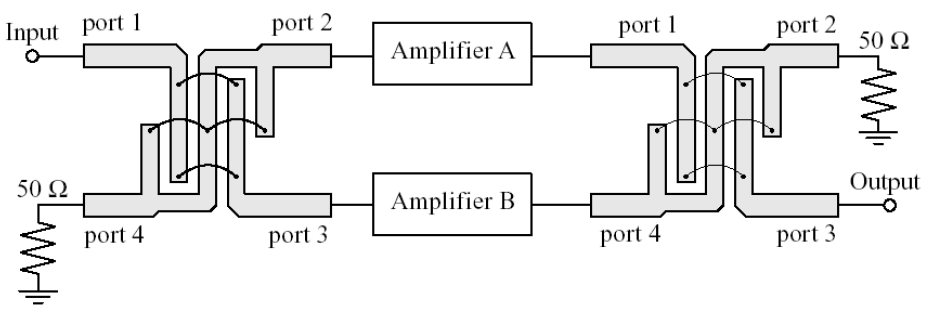

为了增宽放大器频带,常采用平衡式放大器和行波放大器。平衡式放大器由两个相同的晶体管和两个3dB 耦合器组成,其S 参数

图 11 平衡式放大器原理框图

由上式可见,平衡式放大器的输入和输出是匹配的。将多级平衡式放大器级联,可以获得宽带匹配特性。在晶体管非完全对称时,级间失配将使输入失配。以3 级为例:

图 12 平衡式放大器示意图

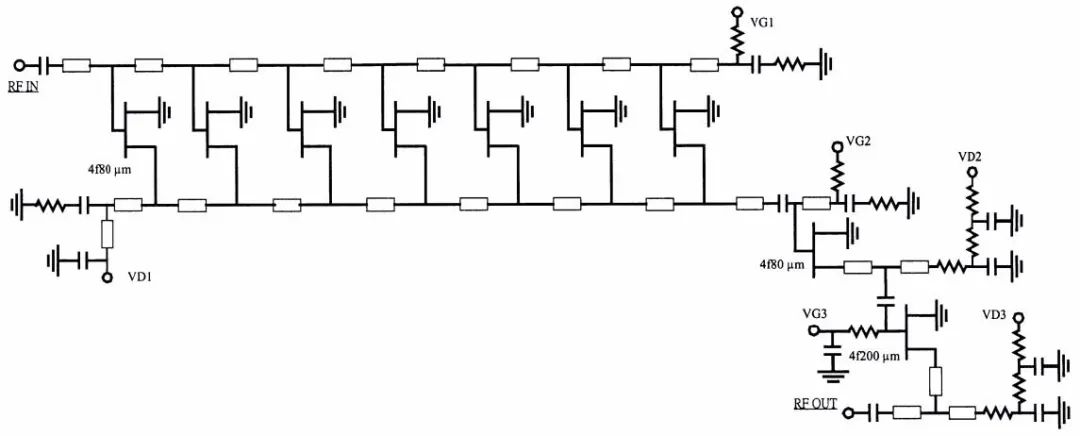

行波放大器又称分布式放大器。原理是,将微波管的输入、输出电容、电阻吸收到输入、输出传输线中,由多条传输线和多只微波管构成分布式有损耗均匀传输线,使微波以行波方式在传输线中传播。合理设计输入和输出传输线的相位,使传输过程中微波被微波管逐次放大,从而构成理论上没有频率限制的宽带放大器。图13 所示基于分布放大概念的宽带放大器电路在0.1 至40GHz 范围内增益22dB±1.5dB。

图13 分布式宽带放大器电路

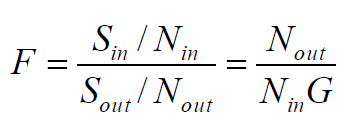

功率放大器的输出功率一般以增益1dB 压缩点输出功率P-1dB 和饱和输出功率Psat 来表示。一般Psat 比P-1dB 高1~2dB。

采用功率合成技术,可输出更高功率。

功率放大器的增益一般用小信号增益和相关增益来表示。小信号增益与一般放大器的增益定义类似。相关增益是达到特定输出功率时的最大增益。

功率放大器的效率十分重要。功放的效率一般用功率附加效率ηadd来表征,其定义为

其中,Pout、Pin和PDC 分别是输出功率、输入功率和直流消耗功率。

(5)交调系数

由于放大器的非线性,当多个频率分量输入放大器进行功率放大时将产生交调分量。奇阶交调分量离所需信号频带接近,会引起较大的干扰,并且难以用滤波器滤除。其中,阶次最低的3 阶交调最强。三阶交调即(2fi-fi+1)和(fi+1-fi)。

功放输出交调失真用交调系数表征,i 阶交调系数定义为:

PIMi 和P1分别是功放输出频谱中i 阶交调分量功率和基波功率。

(6)调幅-调相转换系数

由于功放的非线性,调幅信号输入功放时,其输出信号相移随着输入幅度大小发生变化。

这就是调幅-调相效应。对某些通信系统,调幅-调相效应会导致相位和群时延失真,增加误码率,同时增加了发射杂波电平。

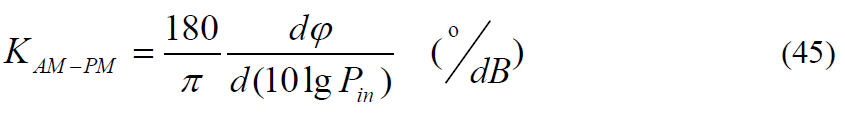

调幅-调相效应用调幅-调相转换系数KAM-PM表示:

其中φ是输出信号相对于输入信号相位,Pin是输入信号功率。

(7)驻波系数

功放输入通常按匹配设计,以达到平坦的增益特性和较高的功率增益。输出匹配一般采用共轭匹配,以获得最大输出功率。

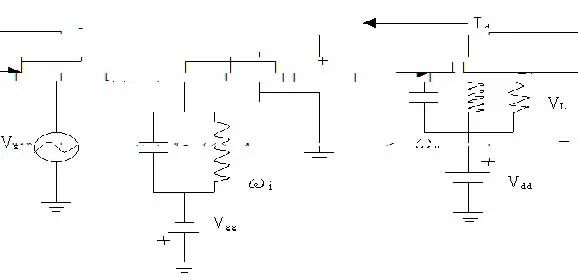

1.3.2 微波晶体管功率放大器设计

微波功率晶体管的S 参数不仅与工作频率和直流工作点有关,而且与微波信号电平有关,必须在特定状态测试其参数。在C 类工作状态,晶体管处于导通的时间比所放大信号的半周期还短,大信号S 参数的测量较困难。目前广泛应用的大信号参数是动态输入阻抗Zin和动态输出阻抗Zout。根据Zin 和Zout设计输入和输出匹配网络。输入匹配网络应使功率管的输入阻抗(通常较低)与源阻抗匹配;输出匹配网络要为负载提供最大的输出功率。

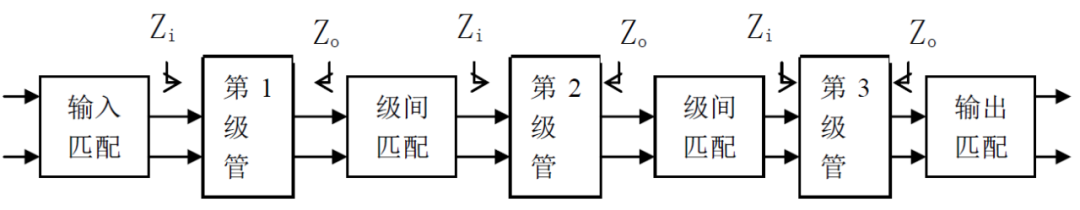

多级放大器设计有两种方法。一是每级设计成各自带输入输出匹配网络的单级放大器,然后级联;另一种方法是级间用匹配网络直接级联。前者设计简单,但结构松散,后者结构紧凑。

严格说来,微波晶体管大信号输入特性随集电极负载变化而变化,输入阻抗和输出阻抗是在特定功率条件下测得的。所以,最好先匹配输出端,然后匹配输入端。然而,在多级放大器级联设计中,并不对每一级单独匹配,只有第一级的输入端和末级的输出端与外电路匹配。在实践中,可假定晶体管的S12=0(单向化设计),先设计第一级输入匹配。

图 14 多级放大器设计过程说明

现以图14 所示3 管组成的放大器为例,设计步骤如下:

1)对第一级放大器输入端独立匹配的优化目标:以Z1in为负载阻抗,单端口输入匹配,满足给定驻波比。

2)第一级与第二级级间匹配:网络的端阻抗分别是Z1out 和Z2in,优化的目标是级间匹配网络的输入和输出驻波比达到要求值。

3)第二级与第三级级间匹配:网络的端阻抗分别是Z2out和Z3in,优化的目标是级间匹配网络的输入和输出驻波比达到要求值。

4)第三级输出独立匹配。

在较低频段,改善微波功率放大器线性性能最常见的办法是采用负反馈。在原理上,要实现负反馈必须使输出信号和输入信号相位完全相同,但在微波频段,放大器件的渡越时间与信号周期相比,不能忽略,使负反馈技术难于直接应用于微波放大器电路。此外,微波功率放大器的增益有限,如果负反馈用于单级,则增益损失太大,用于多级电路,又难于保持稳定。下面介绍改善微波功率放大器线性的几种方法。

(1)功率回退法(Back-0ff)

功率回退法就是限制功率管的实际输出功率。输出功率在1分贝压缩点基础上回退1分贝,三阶交调系数将降低2分贝。

(2)反馈法(Feedback)

反馈法有多种方式,其中直接反馈法(IFB)应用较广。在这种方法中,将放大器的输入和输出信号耦合一部分,检波后的差作为误差信号,通过电控衰减器和移相器控制放大器的增益和相位。

(3)前馈法(Feedforward)

这种方法的基本原理与反馈法类似,也是将放大器的输入和输出信号进行比较,从而得出误差信号,再从输出信号中减去误差信号,得到无非线性失真信号。不同的是,它不是在同一放大器中减掉误差信号,而是用一个辅助放大器在专门的耦合器中去抵消。

(4)预失真法(Predistortion)

预失真法一般是已知信道的非线性失真特性,然后模拟一个失真特性与信道的非线性失真特性恰好相反的网络,将其插入信道中,使它们的特性互相补偿,得到线性较好的信道特性

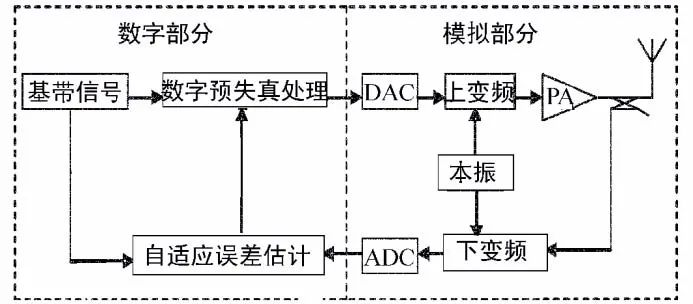

(5)自适应线性化法

自适应线性法能“自动适应”这些变化,它可以看成是将反馈加到预失真法中的校正网络或加到前馈法中的校正网络的一种直接反馈法。

功放自适应预失真线性化原理框图

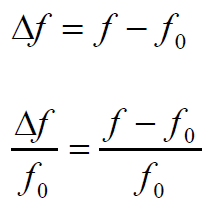

(1) 频率准确度:指振荡器实际工作频率与标称频率之间的误差;

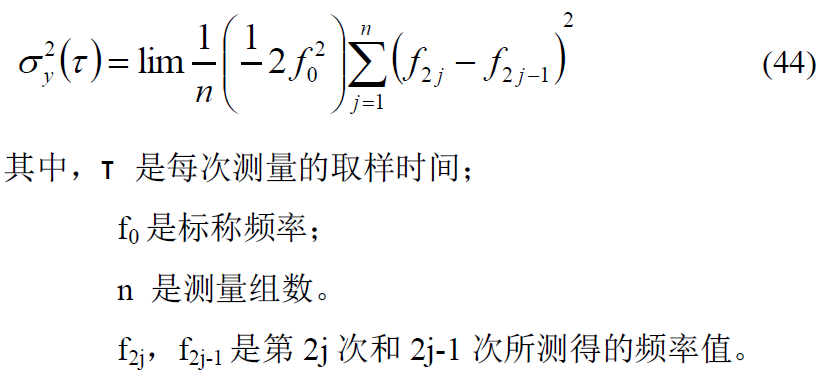

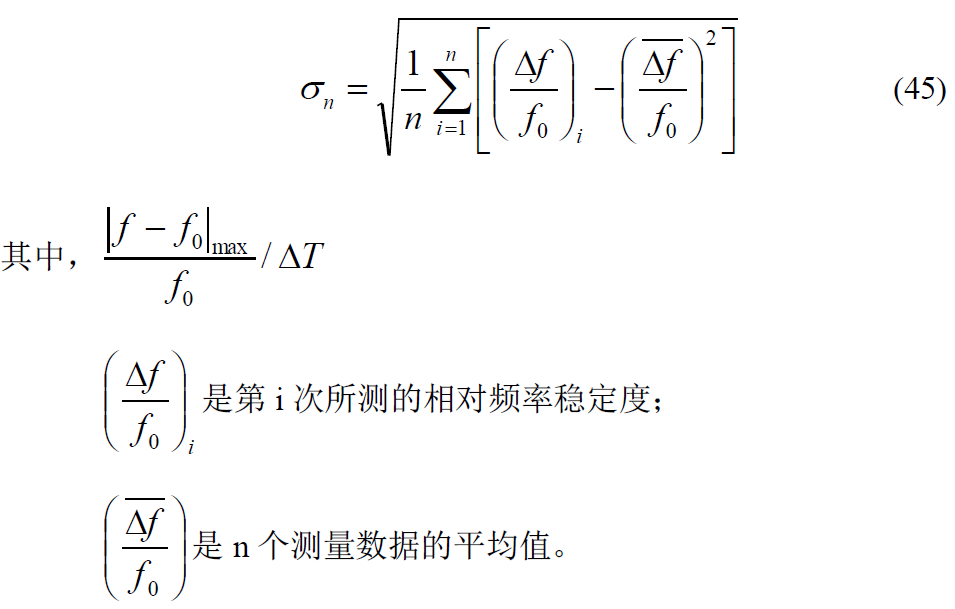

(2)频率稳定度:指一定时间内振荡器频率起伏的均方根值,是振荡器频率起伏的时域表征。一般以中心频率的相对值表示。根据规定时间的长短,可分为长期频率稳定度、短期频率稳定度和瞬时频率稳定度。长期频率稳定度的时间间隔在1 天以上,主要由有源器件的老化特性决定。短期频率稳定度的时间间隔在1 天以内,主要由温度、电压和电路参数变化引起的频率漂移决定。瞬时频率稳定度的时间间隔在1 秒以内,主要由振荡器内部的噪声引起频率随机起伏决定,为便于测量,一般采用阿仑(Alan)方差δ²y表示。

在规定的时间间隔内,频率变化的最大值。

长期频率稳定度:

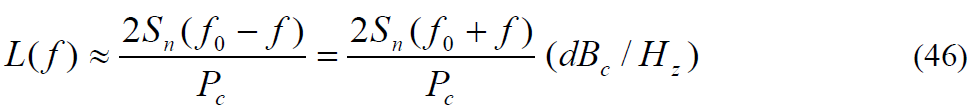

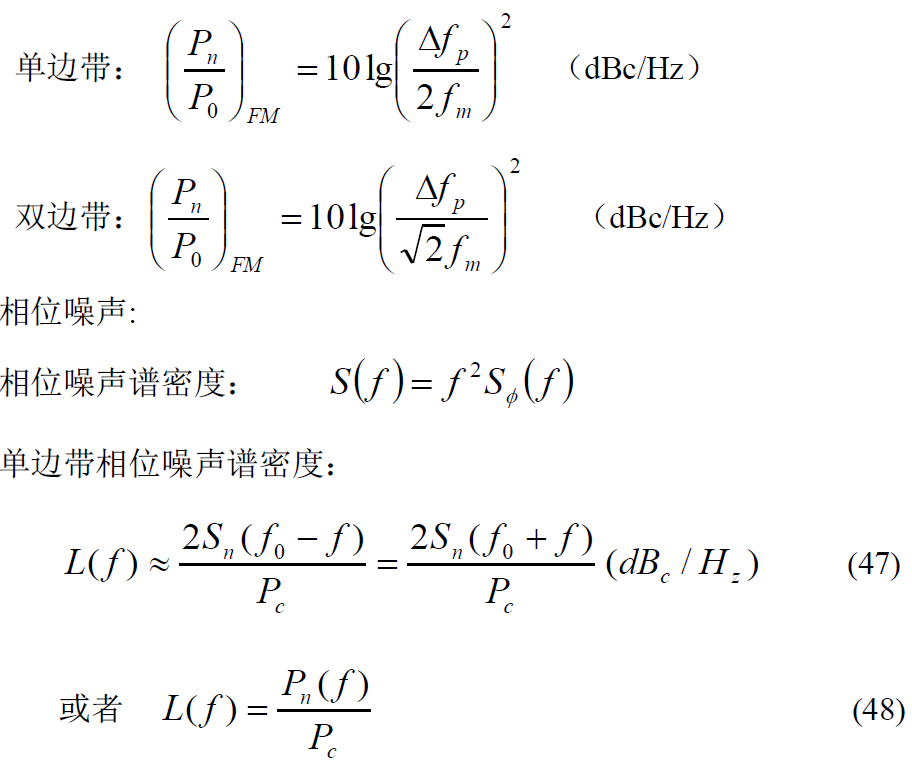

(4) 调频噪声和相位噪声:

是度量振荡器频率(或相位)随机起伏大小的指标,一般采用单边带相位噪声谱密度L(f)表示。L(f)可以用振荡器射频谱上偏离载频f 处的相对噪声功率谱密度的2 倍作为很好的近似:

其中Pc、Sn(f0+f)、Sn(f0-f)分别是载频功率、上、下边带偏离载频f 处的噪声功率谱密度。

调频噪声:用偏离载频f0为fm处的单位频带调频噪声功率Pn与载波功率P0之比表示。

Pn(f) 是偏离载频为f 处的带宽为1Hz 的单边带噪声功率,Pc为载波功率。

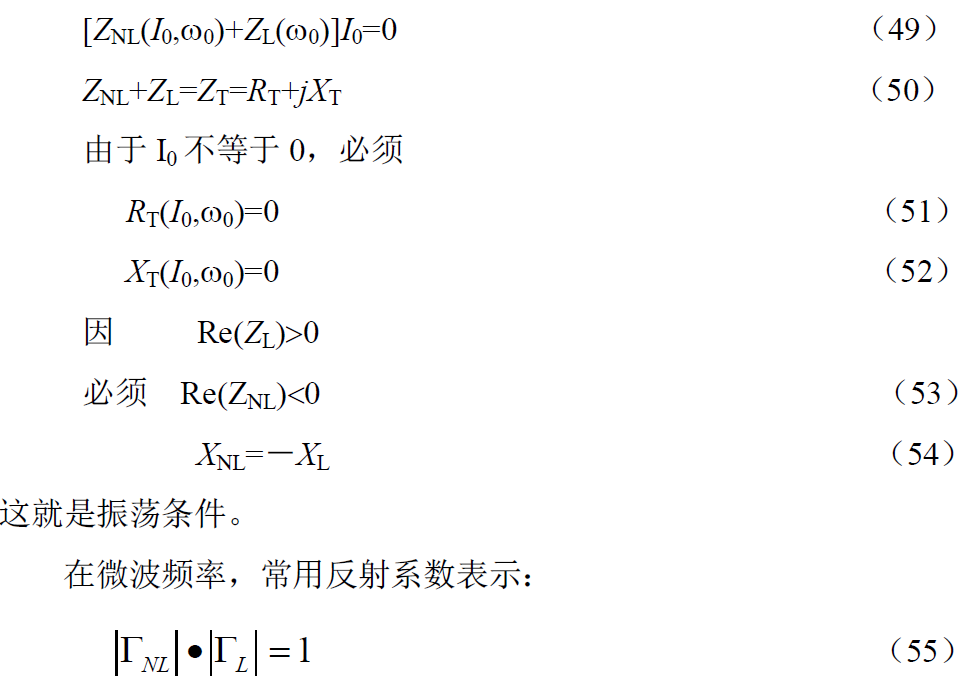

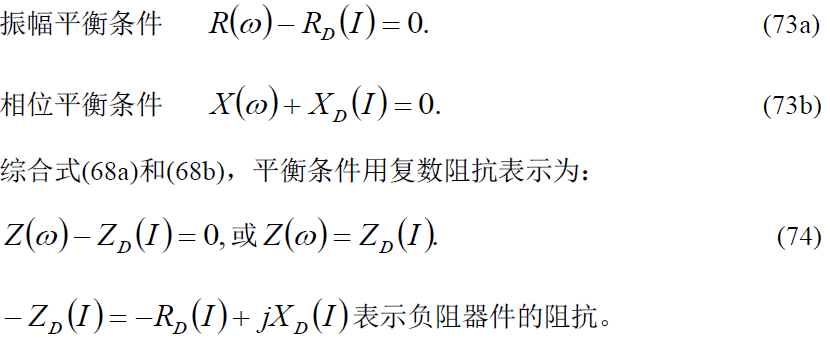

(1) 振荡条件:

振荡器对外呈现实部为负值的阻抗ZNL与一个负载阻抗ZL并联,根据电压定律:

(55)式意味着反射系数ΓNL的模应大于1。

(2)振荡器的稳定性:

如果振荡电路的射频电压或电流在任何一瞬间的任何扰动会自行衰减,使振荡器回到平衡点,则认为振荡器是稳定的。

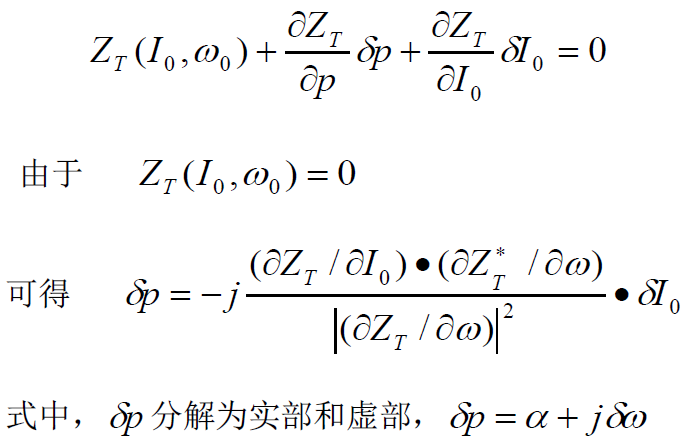

分析振荡器的稳定性时采用准静态法,即在幅度I 上加一个小的扰动。由(50)式,ZT是I0和复平面p(α 和ω )的函数,可将它对I0 和p(即ω0)展开成泰勒级数。由于扰动后电流非零,即在扰动之后振荡继续存在,故应有

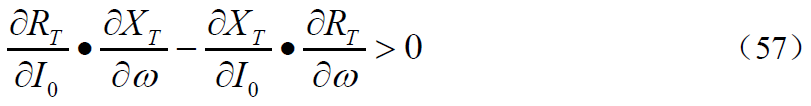

对于电流幅度的一个正向变化,δI > 0,如果复频率变化为负,即如果α为负,表示存在一个衰减波,将返回到它的平衡点I0,则振荡是稳定的。

如果下列条件满足,则δω=0,

于是有稳定条件

这表明,幅度变化不会引起振荡器实频率变化。可以证明,为了达到最高的稳定性,器件阻抗和负载阻抗应在振荡平衡点(I0,ω0)成直角正交。

2.3 振荡器设计

2.3.1 晶体管振荡器电路包括:

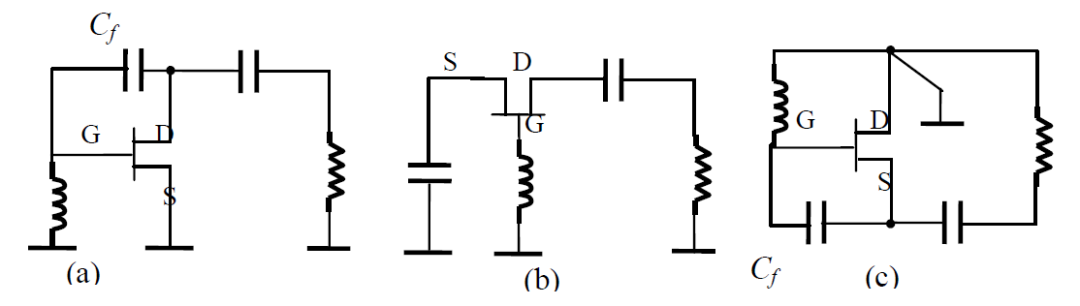

图15 中,(a)是共源并联反馈式,通过反馈电容Cf反馈;(b)是共栅串联反馈,主要通过漏源寄生电阻实现反馈;(c)是共漏并联反馈,也通过反馈电容Cf反馈,但由于栅源寄生电容较大,通常无需外接反馈电容。三种电路中,共栅接法具有最高的振荡频率。

图15 晶体管振荡器典型电路

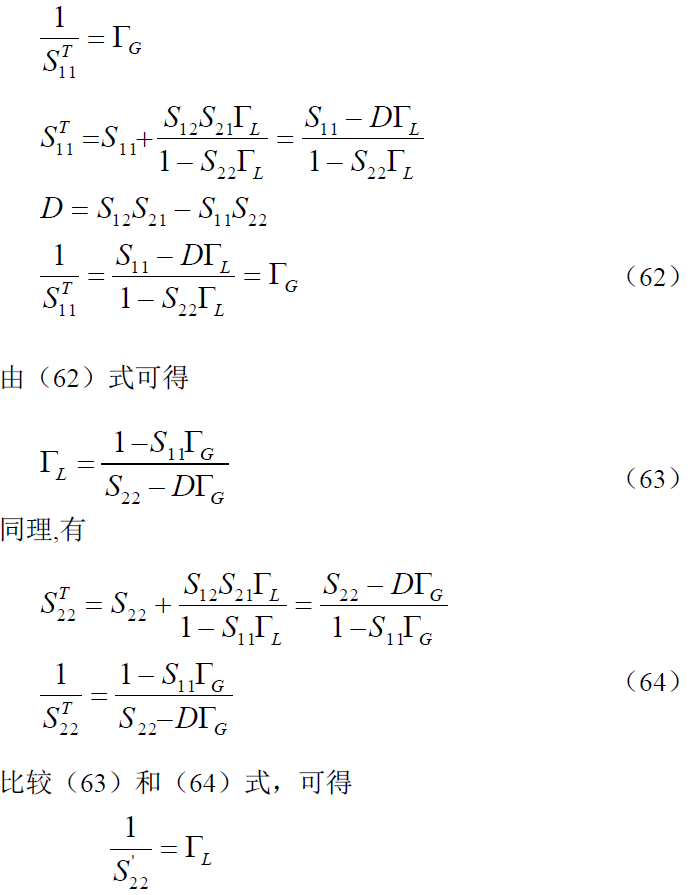

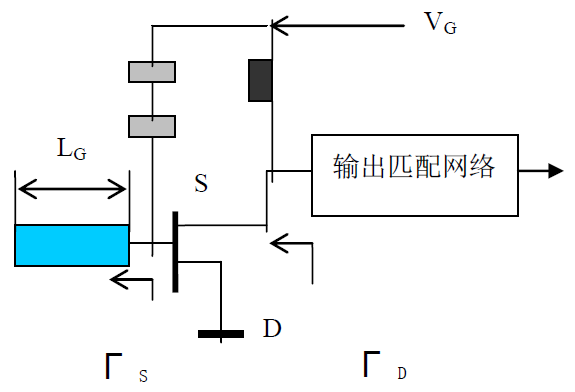

2.3.2 用三端口S 参数设计振荡器

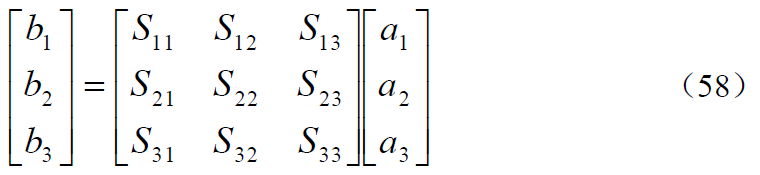

三端口S 参数表示为

其中端口1、2、3 分别代表栅极、漏极和源极,该三端口不定S 矩阵满足下列条件:

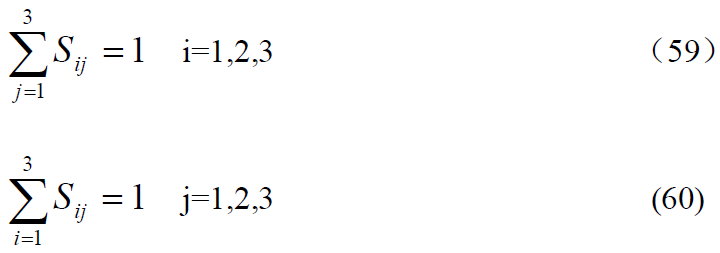

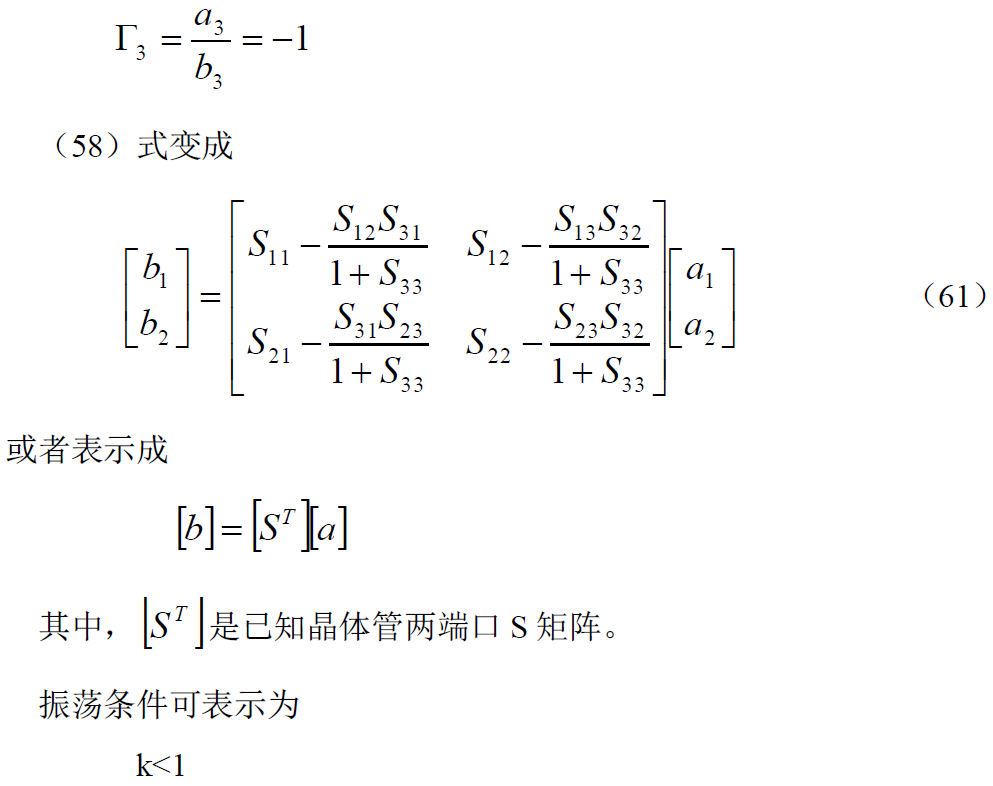

(59)和(60)式表示有9 个参数的6 个方程,利用其中一端接地,可以消去2 个变量,将三端口变成两端口。这样,按二端口放大器的稳定性系数K 设计计算。例如,3 端接地(共源极电路),则

首先保证稳定系数都应该小于1,如果不满足这个条件,则应该改变公共端或加正反馈;其次,必须加无源终端ΓG和ΓL,以便使输入端口和输出端口谐振于振荡频率。由于|ΓG|和|ΓL|均小于1,就意味

假定端口1 满足振荡条件

这就意味着,在端口2 也满足振荡条件。如两端口中任一端口发生振荡,则另一端口必然同样振荡,负载可以出现在两个端口中的任一端口或同时出现在两个端口,但一般负载是在输出终端。以GaAs FET为例说明设计方法。

图16 GaAs FET 反沟道自由振荡器

(1)自由振荡器

图16 表示GaAs FET 反沟道自由振荡器。计算反沟道GaAs FET 的稳定性因子K 可知,这种结构是潜在不稳定的。K<1 意味着,通过适当选择源阻抗和负载阻抗,且在源端不采用串联反馈,可使晶体管产生振荡。

反沟道偏置就是使源极变漏极,漏极变源极,实现共漏电路。由栅-源电容作为反馈电容,不需外加反馈网络,电路简单。

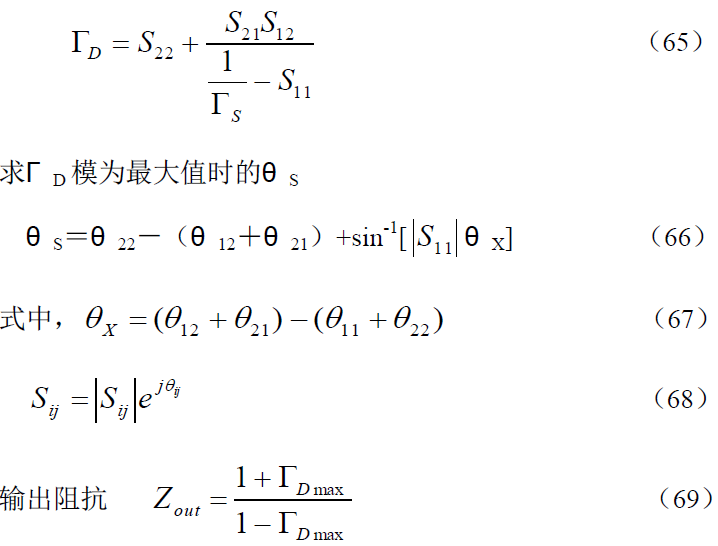

设从栅极向外看的反射系数为Γs,它是一段长LG 的开路微带线,忽略损耗,Γs的幅角arg(Γs)=θs=-arg(4πLG/λg)

从漏极看入的反射系数则为ΓD,

可根据共扼匹配条件设计输出匹配网络。

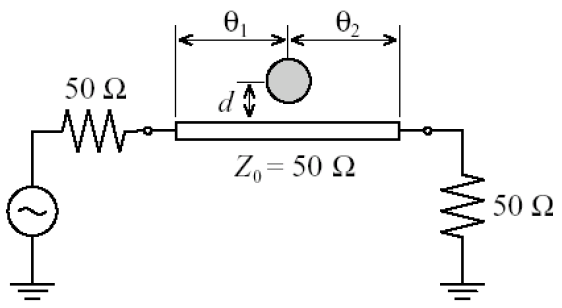

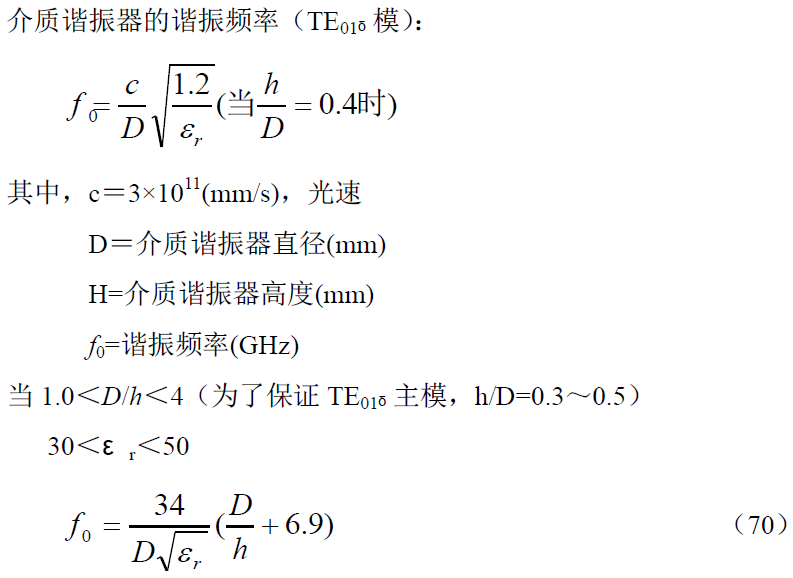

(2)介质谐振器稳频振荡器(DRO)

通过在电路中增加谐振器,可提高三端器件振荡器的频率稳定度。

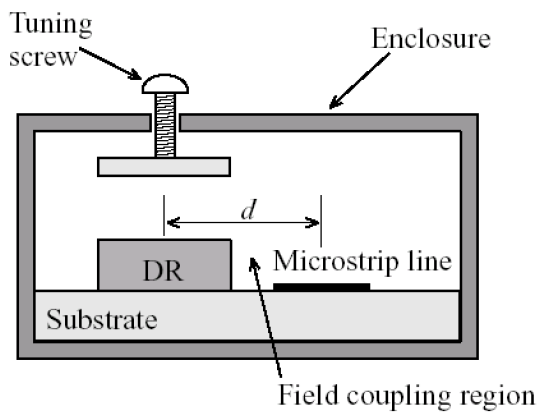

图17a 介质谐振器结构示意图

图17b 介质谐振器振荡器原理电路图

DRO 的温度稳定性可用耦合系数、Q 值和晶体管反射相位随温度的变化率确定。

自由振荡的晶体管振荡器具有负温度系数,需要一个具有正温度系数的介质谐振器

(DR)来补偿频率随温度的漂移。温度系数+9ppm/℃~-9ppmm/℃之间的任一值的DR 都能买到。

此式的精确度2%左右。

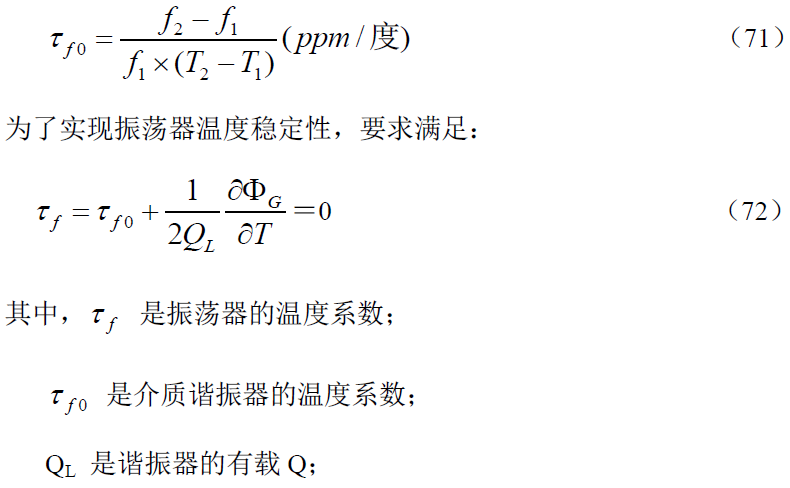

介质谐振器谐振频率温度系数:

对于给定器件, 是固定的,可见,为了使振荡器频率温度稳定,可以选择介质的温度系数,并通过调节DR 与微带之间的耦合,改变QL来实现。

是固定的,可见,为了使振荡器频率温度稳定,可以选择介质的温度系数,并通过调节DR 与微带之间的耦合,改变QL来实现。

(3)DRO 的机械调谐和电调谐

DR 的谐振频率对屏蔽十分敏感,也就是对接地板的靠近程度十分敏感。将调谐螺钉从外壳顶部盖板伸到DR 的正上方,当板与谐振器间距减小时,常用的TE01δ 模频率升高。距离应大于谐振器高度的一半,以免Q 值下降。机械调谐频率范围约±2﹪,而不致影响振荡器的调频噪声、输出功率和频率稳定度的温度特性。

可用不同方法对DRO 的频率电调,如变容管调谐、YIG 调谐、偏置调谐、光调谐等。最常用的是变容管调谐,变容管通过磁耦合与DR 耦合,改变变容管偏压,从而改变谐振频率。

图18 反沟道FET 变容管调谐DR 振荡器

基于半导体P-N 结的雪崩击穿现象,而雪崩管在不同的外电路结构和条件下,以不同的模式工作。目前,最常用的工作模式有两种:IMPATT(Impact Avalanche Transit Time)模式和TRAPATT(Trapped Plasma Avalanche Triggered Transit)模式。

工作于IMPATT 模式的二极管是利用雪崩倍增效应和渡越时间效应相结合而产生负阻的器件。

体效应二极管不同于其它微波二极管,它不包含任何结,而是利用半导体材料体内物理效应(体效应)的固态微波器件。它利用电子在能谷间的转移而产生负阻,又称转移电子器件(TED)。工作频段1~120GHz,噪声低于雪崩二极管,效率低于10﹪。

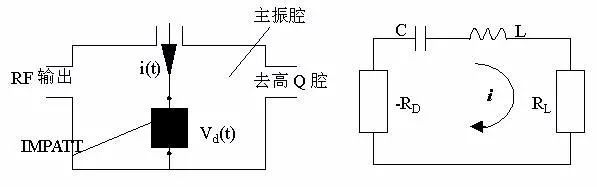

为了阐明振荡器工作的一般原理,我们以图18 和图19 所示的包含雪崩负阻器件的串联振荡回路为出发点分析起振条件。图中,-RD是负阻器件的小信号负阻;RL包含电路损耗电阻及负载电阻;LC 表示外电路的电抗元件及器件的小信号电抗元件。

假定在这电路中存在某种起始的自由振荡,其回路电流为i 。回路电流是一个幅度随时间变化的正弦振荡。当RL>RD时,α>0,振幅随时间而衰减;当RL<RD时,α<0,振幅随时间而增长;当RL=RD时,振幅保持不变。

由此可见,在图20 所示的电路中,为了使起始的振荡得以增长,雪崩器件的小信号负阻的绝对值必须大于回路电阻,即RL<|RD|,这就是起振条件。

通常,回路中的起始振荡起因于某种噪声或电冲击信号,当满足起振条件时,微弱的振荡就会增长为大幅度的振荡。因为如前所述,器件的负阻是振幅的函数,一旦起振以后,振幅无限地增长,而是逐渐趋于某一稳态值。

图19 二极管振荡器结构示意图 图20 二极管振荡器串联振荡回路

根据负阻振荡器的一般等效电路可以导出负阻振荡器在稳态时必须满足的条件。

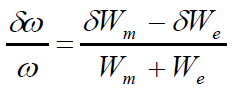

莱斯特微扰定理:

其中,δω/ω是频率的相对变化,Wm和We分别是电路中储存的磁能和电能。

莱斯特微扰定理表明,频率的变化与回路的储能变化成正比,储能越小,频率变化越小;储能变化越大,频率变化越大。二极管振荡器的调谐方法有:

(1) 偏压调谐:改变GUNN 偏置电压,或改变IMPATT 的偏置电流,可改变二极管等效电路参数,从而改变振荡频率;

(2) 变容管调谐:是电调谐,结构简单,调谐速度快;

(3) YIG 调谐:是磁调谐,调谐范围宽,线性好,速度慢,结构复杂;

(4) 机械调谐。

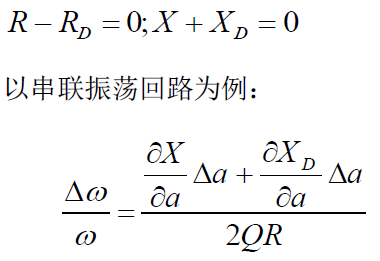

可见,外界因素变化Δa越大,频率变化越大;回路电抗随外界因素的变化越大,频率稳定度越差;回路的Q 值越低,频率稳定度越差。

引起负阻振荡器频率变化的因素:

1)偏置电源不稳;

2)环境温度变化;

3)负载阻抗变化;

4)机械冲击或振动。

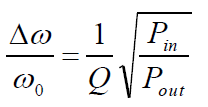

稳频措施:

(1)注入锁定法:

用一个稳定的信号注入锁定,注锁范围:

式中,Pin和Pout分别是注入功率和输出功率,Q 是振荡器的Q 值,Δω是注锁带宽。

(2)温度补偿法:

采用热敏电阻与晶体管组成具有负温度系数的电路来控制偏压。

(3)锁相环法:

(4) 外腔稳频法:用高Q 腔稳频,如图20,有几种稳频方法:

□ 反射式:存在跳频问题。

□ 通过式:插损大。

□ 频带反射式。

图 21 几种外腔稳频方法

频带反射式稳频的特点:

1) 单调谐;

2) 工作频带的中心点就是频率稳定度最高点,也是传输损耗最小点;

3) 随着驻波比增大,振荡范围扩大,传输损耗也减小;

4) 当耦合线长度改变时,工作点偏离频带中心,振荡特性发生畸变,但仍保持单一模式工作。

高 Q 稳频腔的温度补偿:

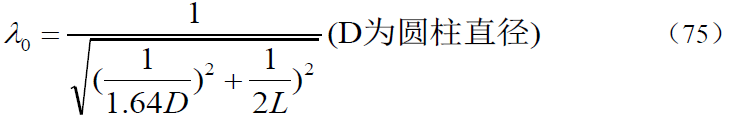

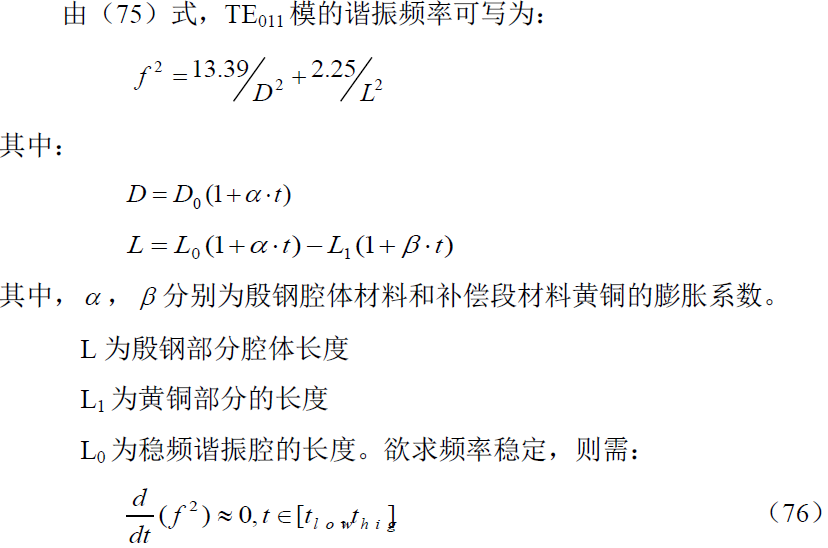

以 TE011模高Q 稳频腔为例,谐振波长可表示为:

利用圆柱谐振腔的波型图,根据谐振在TE011 模的条件选择D/L。

为了使振荡器在外界环境温度变化时保持稳定,应对高Q 腔进行温度补偿设计。

高 Q 腔用热膨胀系数很小的殷钢制成,调谐螺钉用热膨胀系数较大的黄铜作为温度补偿。

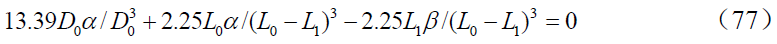

由以上各式可以导出:

将D0,Lo-L1(=L),α(=1×10-6/℃),β(=19×10-6/℃)代入(77)式,可得到温度补偿的长度 L1。

倍频器是指能完成输入信号频率倍增功能的电子组件。图22 是一个理想倍频器的原理示意图。

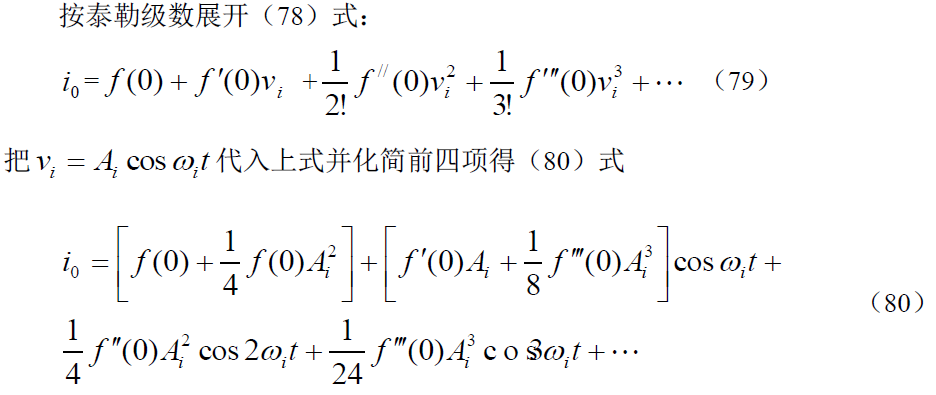

输入信号是Aicosωit,其输入角频率为ωi,通过N 次倍频后输出信号是A0cosNω it,输出角频率为Nωi。N 是倍频次数,且不等于1。

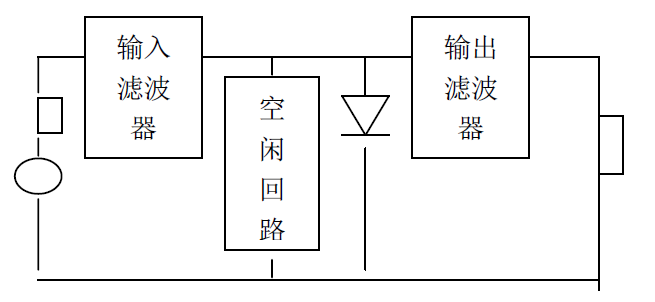

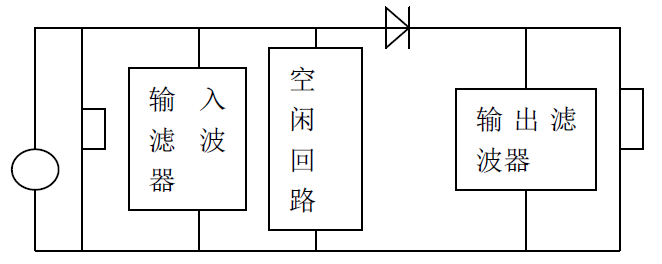

原则上,各种非线性器件都能实现倍频,倍频器的核心是非线性器件,还包括输入、输出匹配电路、空闲回路、偏置等。

为了说明倍频器的基本原理,采用简化倍频过程的处理方法,即忽略所有高阶混合效应,考虑一个二端口非线性元件,其变换特性由(78)式给出

式中,f 为器件的非线性变换函数,它把输入电流i0 与所加输入电压vi 联系起来。

可见,输出电流中除含有基波分量和直流分量外,还含有2 次、3 次等无穷多的谐波分量。设计倍频器的基本目标就是使所需要的输出频率Nω i 分量最大,其余所有频率的输出分量都减小至最小。

由于变换函数同时受到器件和它与电路的相互作用所控制,只有通过正确的电路设计才可实现有效倍频;同时可以看出,杂散是倍频器的一个重要指标。

倍频器在系统应用中具有以下特点:

(1) 在降低主振源频率的同时,可获得与主振源相同频率稳定度的更高频率源;

(2) 输入输出工作频率不同,减少了各级之间的寄生耦合,防止寄生振荡;

(3) 在不增加主振源工作频率范围的前提下,成倍地扩展输出频率范围,增加了工作带宽。

为了在所要求的频率上获得最大功率,倍频器必须满足两个条件:

(1)器件的非线性展开式中必须包含有它所需的频率分量,选择适当的器件和电路,使所

需的频率分量足够大;

(2)所选电路应使不需要的谐波分量功率最小,并使器件与电路的相互作用能把寄生参量

的影响减至最小。

(3)其他要求:工作频段、带宽、频谱纯度、相位噪声恶化程度等。

倍频器种类:

(1)用二极管pn 结的静态非线性V-I 关系,即非线性电阻产生谐波;

(2)用双极晶体管的非线性,即C 类放大器产生谐波;

(3)用GaAs FET 管漏电流饱和或夹断效应;

(4)IMPATT 振荡器被注入锁定在基准频率的N 次谐波上,实现倍频;

(5)用变容二极管的非线性电抗实现参量倍频;

(6)用阶跃恢复二极管产生谐波的高次倍频;

(7)PIN 二极管倍频。

倍频次数较高时,应优先采用阶跃恢复二极管来倍频。晶体三极管及宽带放大器等倍频电路,价格便宜,简单易行,适用于低次倍频。它们一般为变电阻类型,所以电路稳定,温度特性好,而阶跃恢复二极管为参数倍频,一般电路复杂,电路稳定性差,温度特性也差,但可实现高次倍频。

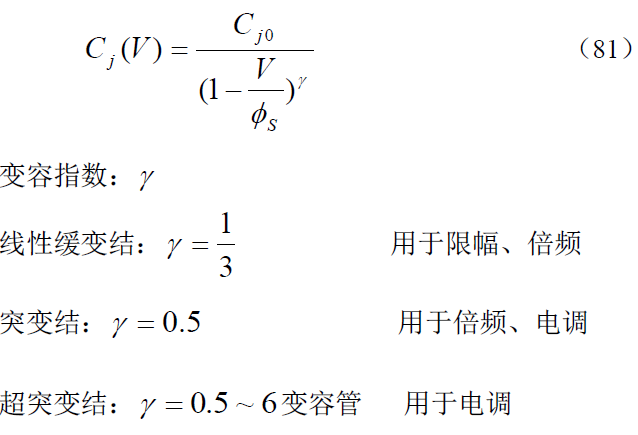

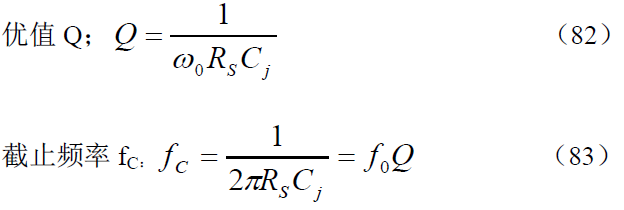

变容二极管的结电容随外加偏压而变:

4.2.2 变容管倍频原理

稳态正弦波加到变容管上,产生的波形将发生畸变,生产高次谐波,谐波含量多少、幅度大小与二极管电容的非线性程度及激励电平有关。

变容管倍频器有两种基本电路:并联型(又称电流激励型)和串联型(又称电压激励型)。

并联型电路有利于变容管散热,常用于大功率倍频器;串联型电路在较高次倍频时有较高的效率,适合于微带结构安装。

图23a 并联型倍频器

图23b 串联型倍频器

4.2.3 变容管倍频器设计特点

(1) 变容管倍频器需要输入调谐和输出调谐;

(2) 在倍频次数大于1 时,需要加空闲回路,因而是窄带的;

(3) 为了得到较高的效率,必须使输入、输出和空闲回路仅仅通过非线性电抗实现耦合,并使输入电路和输出电路在相应的输入频率和输出频率与变容管的动态阻抗共轭匹配;

(4) 在变容管中,只应有输入频率、输出频率和空闲频率的电流流通。

4.2.4 设计步骤

(1) 根据输入、输出频率和功率要求选择变容管:γ ,Cmin,fC,,VB;

(2) 查变容管倍频器设计表格(伯克哈德表);

(3) 计算倍频器的参数:Smax,Rs,η ,Pout,Rin,Rout,C0i 等;

(4)进行输入、输出电路设计。

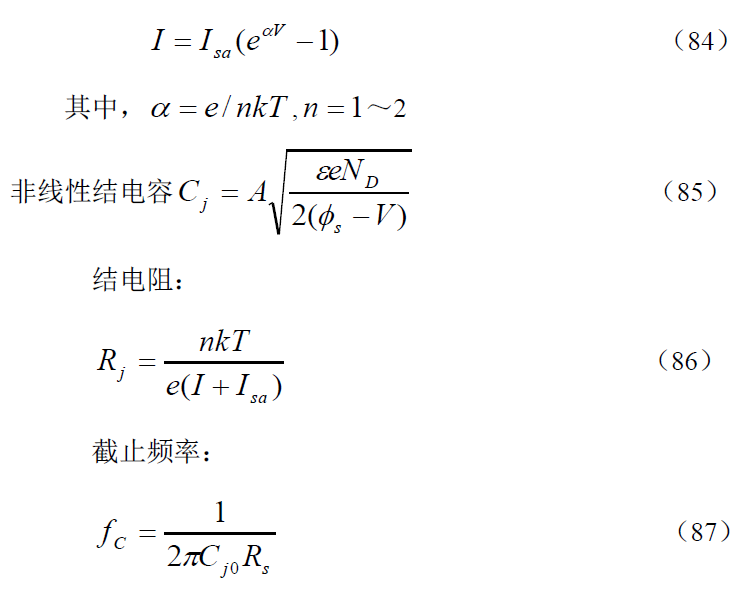

在第一章介绍了肖特基二极管的非线性电阻和非线性电容特性:

非线性电阻特性:

利用肖特基二极管的非线性电阻特性实现倍频,是使输入信号波形发生畸变,从中提取谐波分量。肖特基二极管截止频率很高(达吉赫兹),变阻倍频器常用在极高频段,不过,变频损耗高,理论上为N²。

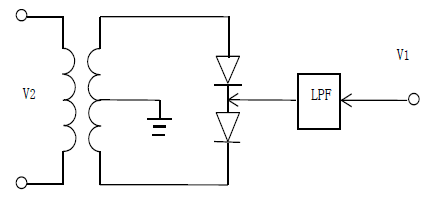

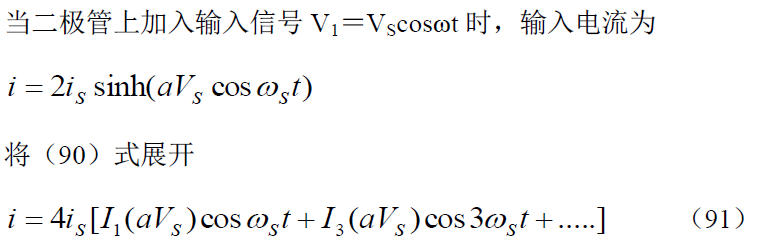

倍频器可采用单个或多个非线性器件,单器件由于承受功率有限,电路不能提供足够的输出功率和较大的动态范围;另一方面,单器件电路不能抑制不需要的谐波。采用多器件能克服这些缺点。采用双管的平衡结构偶次倍频器可抑制奇次谐波,等效电路如图24。

图24 平衡式倍频器等效电路

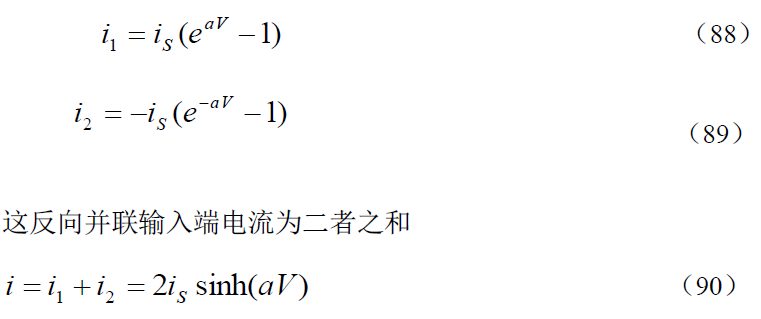

两个二极管相对于输入回路反向并联,相对于输出回路为同相串联设信号电压为V1,肖特基二极管的I/V 特性如(88)式。其中iS是反向饱和电流。两个二极管的电流分别为

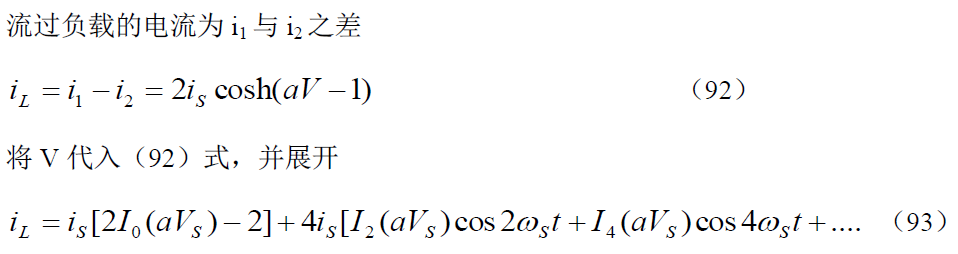

(91)式表明,输入回路中只有输入信号的基波和奇次谐波,不含直流和偶次谐波。流过负载的电流为i1与i2之差

(93)式表明,流过负载上的电流仅含激励频率的偶次谐波。该电路适用于偶次倍频,其输入基波与输出谐波相互隔离,因而输入和输出回路可分别进行匹配,容易实现宽带性能。

(1) 可用频率高,特别适用于毫米波倍频;

(2) 激励信号小;

(3) 容易实现宽带倍频;

(4) 适用于低次倍频;

(5) 杂波小,频谱纯,稳定性好。

阶跃恢复二极管简称阶跃管(SRD),是一种PN 结二极管,其主要特点是,加上正向电压时,和普通二极管一样,正向导通;当外加电压由正向变为反向后,阶跃管并不立即截止,而是有很大的反向电流流通,至到某一时刻,才以很快的速度转换到截止,于是形成了“阶跃”,阶跃波形包含丰富的高次谐波。由于在半周产生电流跳变,在外电路中形成很窄的脉冲,构成阶跃管脉冲产生器;用适当的外电路提取谐波,就构成倍频器。

阶跃恢复二极管的主要参数:

(1) 阶跃时间Tt

定义为阶跃管的反向电流IR从0.8IR降至0.2IR所需的时间。Tt越小,高次谐波越丰富,倍频效率越高,它和基频应保持如下的关系:Tt≤1/f0

(2) 少数载流子寿命τ

少数载流子寿命τ 是注入停止后,少数载流子的平均存在时间,定义为少数载流子浓度减少到初始值的1/e 所经历的时间。它决定了阶跃管的最低输入频率的极限。为使阶跃管正常工作,输入频率PIN应满足:τ≥fIN

4.4.2 阶跃管倍频器

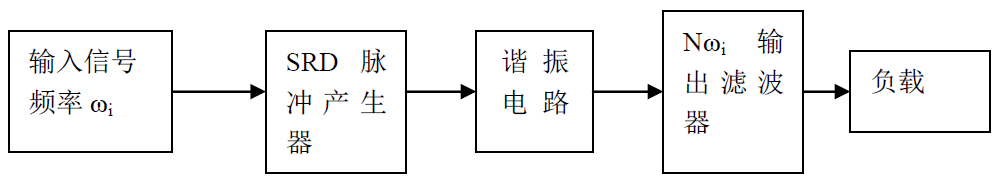

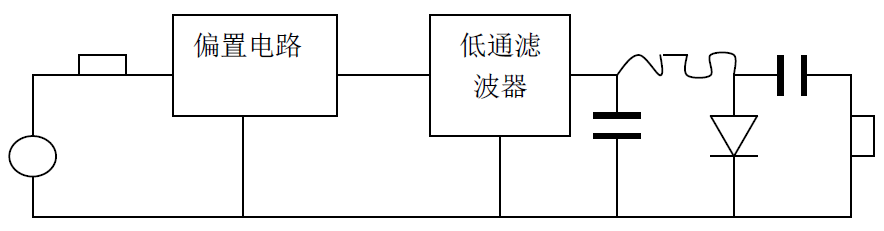

特点:倍频次数高,效率高,杂波多和温度稳定性差。阶跃管倍频器组成框图如图25,其中脉冲发生器组成框图如图26 所示。

图25 阶跃管倍频器的组成

图26 阶跃管倍频器的脉冲发生器

4.5.1 反向并联PIN 二极管对的输出电流频谱

两只参数相同的PIN 二极管反向并联,形成二极管对。设外加电压:

可见,输出电流中不含输入信号的偶次分量,偶次分量在二极管环路中形成环流。

4.5.2 反向并联PIN 二极管对的输出频谱

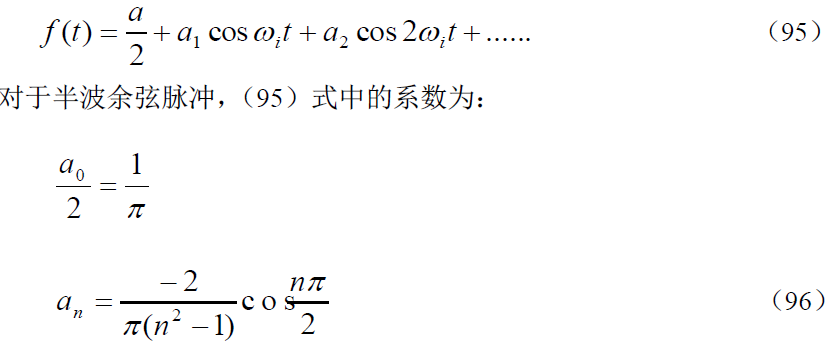

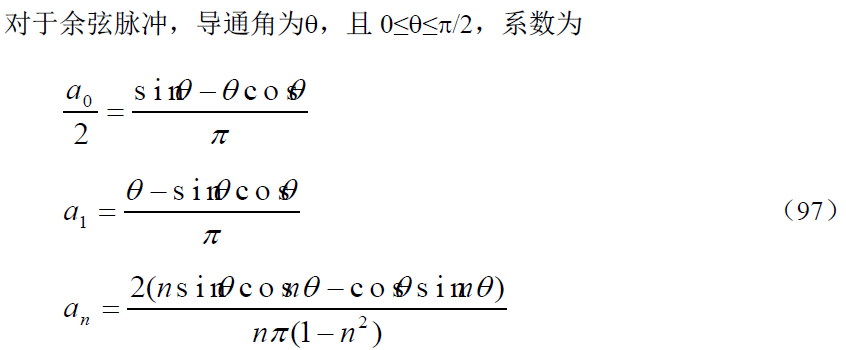

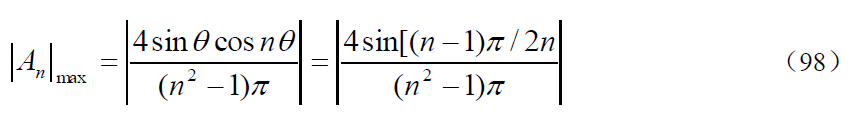

周期性偶函数可展开成如下付氏级数:

反向并联PIN 二极管对的输出波形可看成半波余弦脉冲减去余弦脉冲。可得到最大倍频效率:

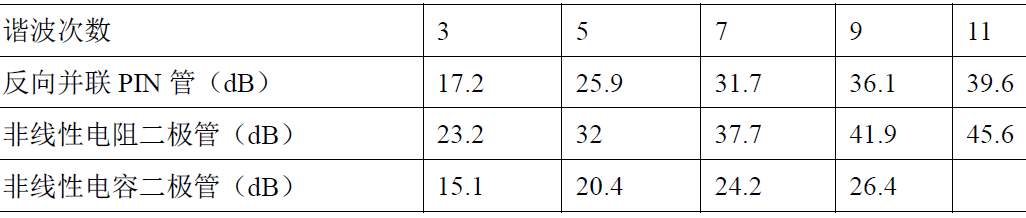

表1 理想二极管的最小倍频损耗

由表1 可见,理想开关二极管的倍频效率在变容管和变阻管之间。由于作为倍频应用时,微波信号的幅度不能使PIN 管完全导通或截止,而是处于半导通半截止状态,因而,高次谐波分量比(98)式计算的值大,PIN 管更适合于高次倍频。

(1) 与混频二极管倍频相比,效率高,次数高;

(2) 与变容管,效率低,但价廉,次数高,稳定性好,输入功率低;

(3) 与阶跃管相比,倍频次数低,但结构简单,输入功率低,杂散小,稳定度高。

图27 反并联PIN 对管奇次倍频器组成框图

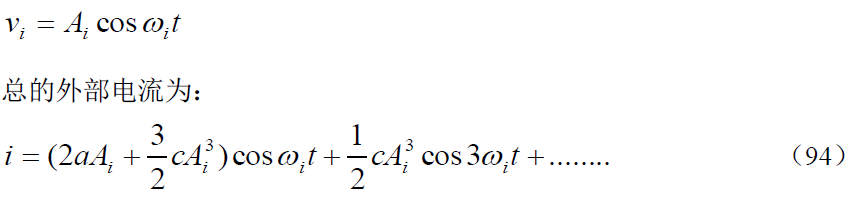

FET 倍频器是通过对输入信号进行整流来产生谐波,在有效的FET 倍频器中,有两种偏置方式:

(1)直流栅偏压为零,使FET 工作在饱和状态;

(2)直流栅偏压Vgg等于或小于夹断电压VP:此时,输入信号在正半周期部分导通,漏极的导通为脉冲型的,脉冲形状近似为半个余弦。在这个过程中,可以把漏电流波形按半个余弦脉冲序列处理。脉冲的占空比随Vgg变化,如果Vgg=Vp,脉冲的占空比为50%,但是,如果Vgg

图28示出FET倍频器电路,其中的FET是理想的,图中除谐振电路的激励频率外,其它频率上FET的栅极是短路的;除输出频率外,在其它所有谐波和基波上漏极是处于短路状态的。

在场效应晶体管中,产生谐波的非线性作用主要有以下几种:

(1) 栅-源和栅漏的非线性电容Cgs和Cgd;

(2) 漏极电流Ids被限幅引起的非线性;

(3) Vgs-Ids非线性变换特性;

(4) 输出电导的非线性。

上述任何一种非线性均可用于实现倍频。但理论分析和实践证明,对于单栅场效应晶体管,利用漏极电流Ids的限幅作用可以实现高的倍频增益。

图28理想的FET倍频器(漏和栅的寄生电容吸收在调谐回路中)

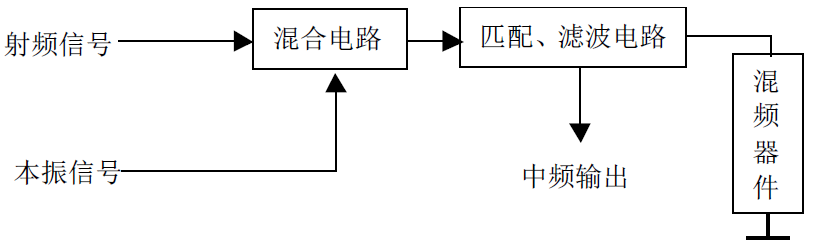

混频器是实现两个频率(或其谐波)和差运算的部件。雷达、通信、遥感和毫米波测试等系统中,广泛使用混频器实现外差式毫米波信号接收、毫米波频率合成、调制解调等功能。

混频器采用非线性器件完成频率变换,根据所采用的器件可以分为二极管混频器和三端器件混频器。其中最早使用,到目前仍处于主导地位的是二极管混频器,具有结构简单、噪声低、频带宽等优点,其工作频段已扩展到吉赫兹(THz)以上。

二极管混频器的缺点是具有变频损耗,并且在高电平应用时动态范围不够。通常,三端器件混频器与二极管混频器相比在噪声系数上没有优势。栅馈晶体管有源混频器所需本振功率小,并具有变频增益,具有较高的3阶交点(IP3)。晶体管作为可变电阻实现混频,在保持低的1/f噪声的同时,具有与二极管混频器相当的变频损耗,其IP3比一般二极管混频器高出20dB,显示出优越的高电平应用潜力。

5.1 混频器的主要技术指标

1)变频损耗和变频增益

混频器变频损耗指标Lc 定义为输入射频信号资用功率Prf 与输出中频资用功率Pif 之比:Lc=Prf/Pif

2)噪声系数

混频噪声系数NF,定义为输入信噪比SNRi 和输出信噪比SNRo 的比值:

在混频器用于外差式接收机时,根据接收信号是单边带(SSB)信号和双边带(DSB)信号,其噪声系数不同,分别称为单边带噪声系数NFSSB 和双边带噪声系数NFDSB。造成这一差别的根本原因是混频器可以将两个边带的射频信号变换到中频输出,如图29 所示。

单边带噪声系数和双边带噪声系数的关系:

其中tx是混频器噪声温度比,在毫米波频段,混频器噪声温度比约为1.2~1.5。因此,单边带噪声系数高于变频损耗约1~2dB,而比双边带噪声系数高3dB。

3)动态范围

动态范围是混频器能正常工作的输入信号功率范围。混频器动态范围的下限决定于混频器的等效输入噪声功率,动态范围上限决定于混频器的饱和状态对应的输入功率。

4)交调系数

在输入信号包括两个以上的频率分量时,混频器输出信号中将产生交调分量。如果考虑两个频率分量的情况,则影响最大是3阶交调分量,因为在处于中频附近或中频通带内的交调产物中,3 阶交调的阶次最低,幅度最大。

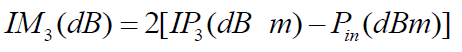

3 阶交调系数Mi定义为:

Mi=PIM3/Pif

式中,PIM3和Pif分别是三阶交调信号功率和中频信号功率。3阶交调系数可由功率回退法根据3阶交点电平计算得到:

5)端口隔离度

混频器隔离度指标中比较重要的是本振-信号端口隔离度、信号-中频端口隔离度、本振-中频端口隔离度和信号-本振隔离度。

6)镜频抑制度

镜频抑制度表征混频对镜频信号抑制程度,定义为在所用信号频率和镜频上分别输入同样功率的信号时,所产生的中频信号幅度比,通常用分贝表示。

7)驻波比

混频器的驻波系数与本振功率和直流偏置情况有密切关系,这是因为本振功率和直流偏置条件的变化导致了混频二极管阻抗的变化。

8)中频阻抗

9)本振功率

混频器的许多特性指标与本振功率紧密相关。二极管混频器存在对应于最小变频损耗的最佳本振电平。

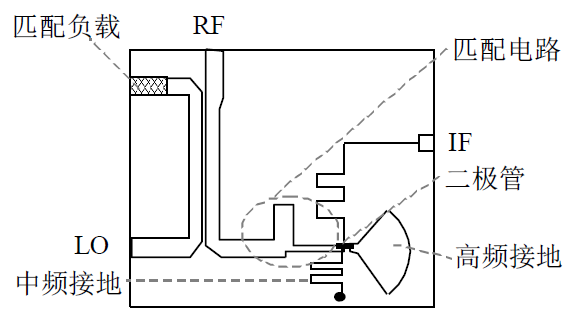

图30 是单端混频器电路原理示意图。混合电路可采用定向耦合器实现,或采用频分双工电路实现。

图30 单端混频器电路原理示意图

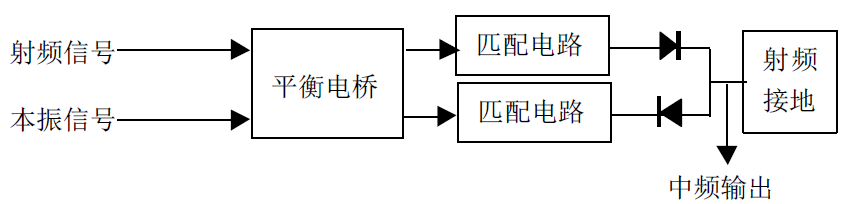

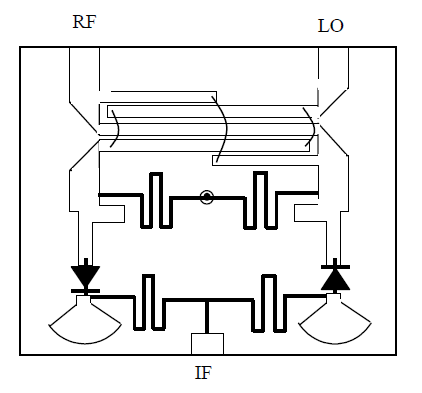

5.2.2 平衡混频器(SBM)

采用平衡电桥实现本振信号耦合,易于实现宽带特性,提高了RF-LO 端口隔离度,可抑制本振调幅噪声,并能抑制本振偶次交调分量,从而改善频谱纯度,减小变频损耗。平衡混频器电路原理图如图32 所示。

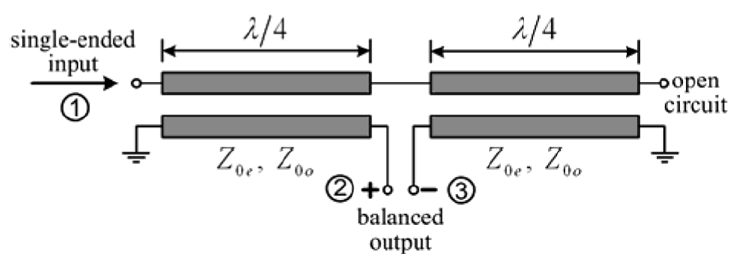

微带集成平衡混频器采用的平衡电桥有以下形式:支线耦合器、混合环电路、Lange 耦合器和马尔尚(Marchand)巴伦。用这些平衡电桥的混频器如图33 所示。

图31 微带单端混频器电路示意图

图 32 平衡混频器电路原理示意图

图 33 平衡混频器电路实例

5.2.3 谐波混频器

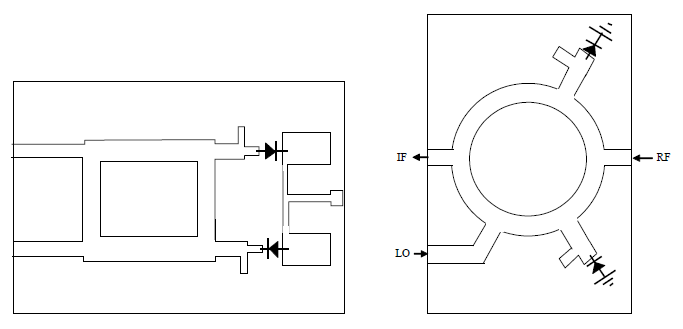

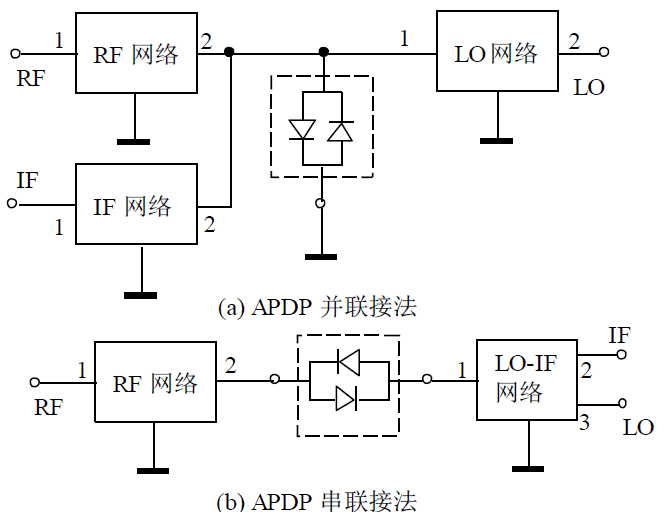

在毫米波频段,要产生高质量和足够功率的本振信号比较困难,成本也比较高。如果本振信号能用其分谐波频率信号代替,势必大大简化本振电路,这就是谐波混频器。在测试仪器中广泛使用谐波混频器,分谐波次数从2 次直到20 次。目前应用较多的谐波混频器可以分为两种,一种采用单只二极管单端混频器形式,可以实现奇次和偶次谐波混频;另一种是采用反并联二极管对(APDP)的偶次谐波混频器。

(1)采用单个二极管的单端谐波混频器

这种谐波混频器电路简单,所需本振功率较小,采用肖特基二极管可实现30 次以下的各次谐波混频。但高次谐波混频损耗大,并且由于采用单端混频电路形式,不能抑制本振噪声,一般用于测试仪器中。

(2)反并联二极管对偶次谐波混频器

采用APDP 的偶次谐波混频器(EHM)已经用于毫米波外差式接收机中。它具有以下优点:

1) 本振频率降为相应基波混频本振频率的1/2 或1/4,采用微波本振源代替毫米波本振源,简化了本振源电路,降低了接收机电路复杂度和成本。

2) 由于APDP 易于达到很高的特性配对,EHM 能很好的抑制偶阶交调寄生分量,这一特性用于上变频器能获得极低的“虚本振”泄漏。

3) EHM 还能大大减小进入中频的本振信号噪声功率。

图34 反并联二极管对(APDP)谐波混频器一般电路形式

频率合成技术是将一个或多个高稳定、高精确度的标准频率经过一定变换,产生同样高稳定度和精确度的大量离散频率的技术。

(1)频率:工作频率、频率步进、频率转换时间、频率稳定度、频率精度;

(2)相位噪声;

(3)输出功率和功率波动;

(4)其他:控制码等。

(1)直接频率合成:采用倍频、混频、滤波等技术。

(2)间接合成法:利用锁相环(PLL)技术,用压控振荡器的输出信号与基准振荡器的信号比较产生的误差信号去调整压控振荡器频率,使之具有与基准振荡器信号相同的稳定度。

(3)直接数字合成(DDS)。

(4)PLL+DDS。

直接式频率合成器原理简单,易于实现。直接模拟式频率合成器是由一个高稳定、高纯度的晶体参考频率源,通过倍频器、分频器、混频器,对频率进行加、减、乘、除运算,得到各种所需频率。

直接合成法的优点是频率转换时间短,并能产生任意小的频率增量。但用这种方法合成的频率范围将受到限制。更重要的是,直接模拟式频率合成器不能实现单片集成,而且输出端的谐波、噪声及寄生频率难以抑制。因此,直接模拟式频率合成器已逐渐被锁相式频率合成器、直接数字式频率合成器取代。

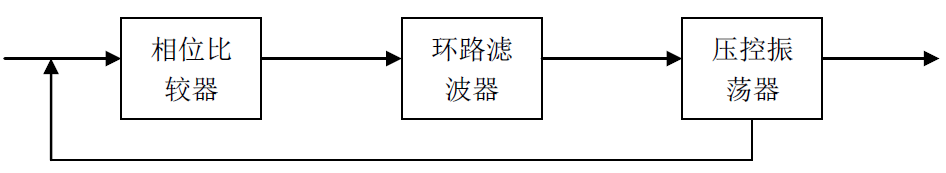

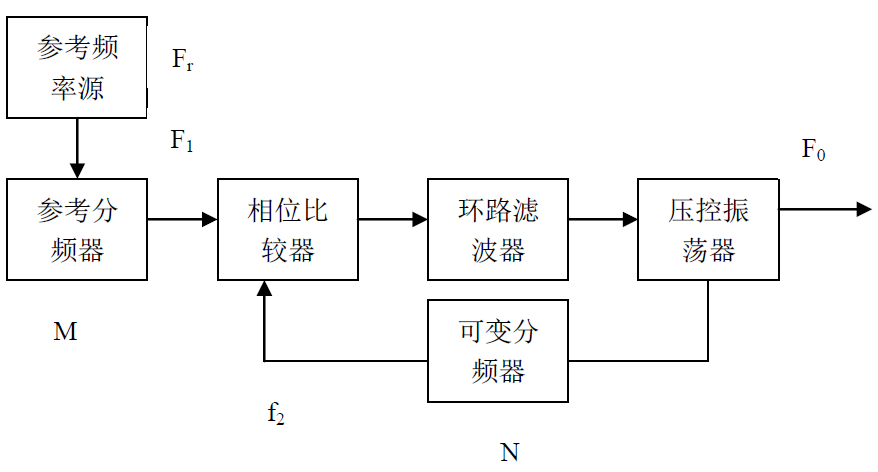

锁相式频率合成器原理如图35所示,锁相式频率合成器是由参考频率源、参考分频器、相位比较器、环路滤波器、压控振荡器、可变分频器构成。

图35 锁相环原理简图

图36 锁相源频率合成器原理简图

由于单环PLL 频率合成器难于同时满足合成器在频带宽度、频率分辨率和频率转换时间等多方面的性能要求,因此,现代通信与电子设备中采用多环PLL 频率合成器、吞除脉冲式锁相环频率合成器或锁相环分数频率合成器。

在多环频率合成器中,使用多个锁相环路。如在三环锁相频率合成器中,高位环提供频率间隔较大的较高频率输出,低位环提供频率间隔较小的较低频率输出,加法环将前两部分加起来,从而获得既有较高的工作频率,频率分辨率也很高,又能快速转换频率的合成信号输出。

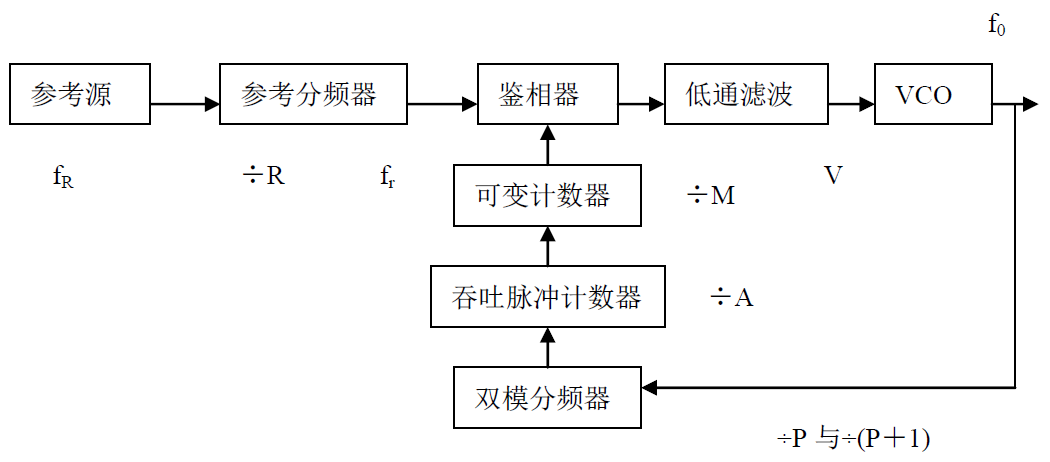

在实际应用中,特别是在微波频段,为获得较大范围的频率点数和较小的步进频率,多采用吞除脉冲式锁相环频率合成器,如图37 所示。其实现方法为,在M 分频器与压控振荡器之间插入高速双模前置分频器(÷P 与÷(P+1))和吞除脉冲计数器A,最终得到总计数分频比:

N= A(P+1)+P(M-A) =PM+ A

输出频率为f0 (PM+A)fr

可见,频率范围扩展了P 倍,而频率间隔仍然保持为较小的fr。

图 37 吞吐脉冲式锁相环频率合成器

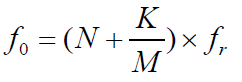

锁相式分数频率合成器的输出信号频率不必是参考信号频率的整数倍,可以是参考信号频率的小数倍。如果参考频率用fr 表示,输出频率用fo 表示,那么输出信号和参考信号的关系可以表示为:

其中,K 和M 为整数,0≤K<M,而M 决定了小数频率合成器的精度。小数频率合成器输出信号的最小频率间隔由参考信号频率和小数频率合成器的分辨位数决定。

由此可见,小数频率合成器在支持较高频率的参考信号的同时可以获得很高的输出频率精度。

小数频率合成器有多种实现方式,其中Δ-Σ小数频率合成器是最成功的实现方式。

图38 DDS 频率合成器原理框图

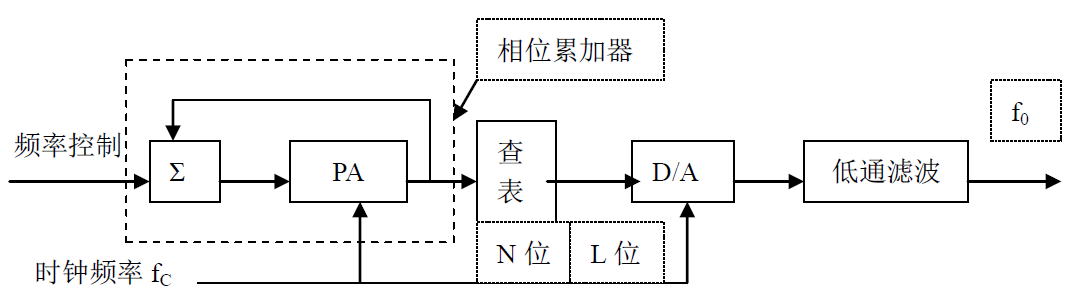

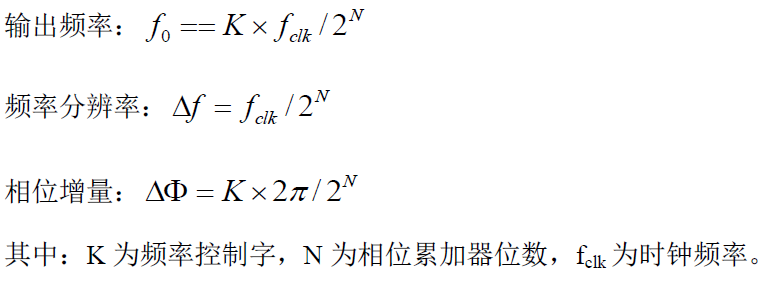

直接数字频率合成(DDS)技术是20 世纪80 年代末,随着数字集成电路和微电子技术的发展出现的一种新的数字频率合成技术,它从相位量化的概念出发进行频率合成。DDS 技术与传统的频率合成技术相比,具有频率分辨率高、相位噪声小、稳定度高、易于调整及控制灵活等优点。

如图38 所示,电路由相位累加器、正弦查询表、D/A 转换器和低通滤波器等部分组成。DDS 的工作原理实质上是以数控的方式产生频率、相位可控制的正弦波。相位累加器由N 位全加器和N 位累加寄存器级联而成,对代表频率的二进制码进行累加运算。幅度/相位转换电路实质上是一个波形寄存器,以供查表使用,读出的数据送入D/A 转换器和低通滤波器。

工作过程为:每来一个时钟脉冲fclk,N 位加法器将频率控制数据与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的输入端,以使加法器在下一时钟的作用下继续与频率控制数据相加;另一方面输出M 位作为取样地址值送入幅度/相位转换电路,幅度/相位转换电路根据这个地址输出相应的波形数据。最后经D/A 转换器和低通滤波器将波形数据转换成所需要的模拟波形。相位累加器在基准时钟的作用下,进行线性相位累加,当相位累加器加满时就会产生一次溢出,这样就完成了一个周期,该周期就是DDS信号的频率周期。其主要关系式为:

DDS 频率合成器的优点:

(1)输出频率相对带宽较宽

输出频率带宽为50%fs(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的抑制,实际的输出频率带宽仍能达到40%fs。

(2)频率转换时间短

DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在DDS的频率控制字改变之后,需经过一个时钟周期之后按照新 的相位增量累加,才能实现频率的转换。因此,频率时间等于频率控制字的传输,也就是一个时钟周期的时间。时钟频率越高,转换时间越短。DDS的频率转换时间可达纳秒数量级,比使用其它的频率合成方法都要短数个数量级。

(3)频率分辨率极高

若时钟fs的频率不变,DDS的频率分辨率就是则相位累加器的位数N决定。只要增加相位累加器的位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,小于1mHz甚至更小。

(4)相位变化连续

改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。

(5)输出波形的灵活性

只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实现调频、调相和调幅功能,产生FSK、PSK、ASK和 MSK等信号。另外,只要在DDS的波形存储器存放不同波形数据,就可以实现各种波形输出,如三角波、锯齿波和矩形波甚至是任意的波形。当DDS的波形存储器分别存放正弦和余弦函数表时,即可得到正交的两路输出。

(6)其他优点

由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价比极高。

DDS也有局限性,主要表现在:

(1)输出频带范围有限

由于DDS内部DAC和波形存储器(ROM)的工作速度限制,使得DDS输出的最高频有限。目前市场上采用CMOS、TTL、ECL工艺制作的DDS芯片,工作频率一般在几十MHz至400MHz左右。采用GaAs工艺的DDS芯片工作频率可达2GHz左右。

(2)输出杂散大

由于DDS采用全数字结构,不可避免地引入了杂散。其来源主要有三个:相位累加器相位舍位误差造成的杂散;幅度量化误差(由存储器有限字长引起)造成的杂散和DAC非理想特性造成的杂散。

尽管DDS技术有很多优点,但它也并不十分完美。其主要不足是合成信号的频率较低、频谱不纯。

PLL技术具有高频率、宽带、频谱质量好等优点,但其频率转换速度低。DDS技术则具有高速频率转换能力、高度的频率和相位分辨能力,但目前尚不能做到宽带,频谱纯度也不如PLL。混合式频率合成技术利用这两种技术各自的优点,将两者结合起来,其基本思想是利用DDS的高分辨率来解决PLL中频率分辨率和频率转换时间的矛盾。通常有DDS激励PLL和DDS附加PLL两种基本方案。 在DDS激励PLL方案中,使DDS在某个频率附近产生精细的频率步进,并且DDS的输出作为PL L的标准输入信号,同时将PLL设计成倍频环,将DDS产生的信号倍频到所需的频率范围内。 该方案通过采用高的鉴相频率(DDS的输出频率)来提高PLL的转换速度,并利用DDS的高分辨率来保证小频率间隔。 DDS附加PLL方案是在环路中插入混频器,使DDS和PLL的输出相加,其输出频率为:fo=Nfr+fDDS。

为了使PLL具有很小的频率转换时间,PLL可采用高鉴相频率fr,而DDS小的频率间隔则可保证输出频率fo的精细变化。fo的上限频率取决于Nfr,频率分辨率取决于DDS。

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!