来源 | TI官网

智库 | 云脑智库(CloudBrain-TT)

云圈 | 进“云脑智库微信群”,请加微信:15881101905,备注您的研究方向

声明 | 本号聚焦相关知识分享,内容观点不代表本号立场,可追溯内容均注明来源,若存在版权等问题,请联系(15881101905,微信同号)删除,谢谢。

LVDS (Low Voltage Differential Signaling)是一种小振幅差分信号技术,它使用非常低的幅度信号 (250mV~450mv)通过一对平行的 PCB 走线或平衡电缆传输数据。

在两条平行的差分信号线上流经的电流及电压振幅相反,噪声信号同时耦合到两条线上,而接受端只关心两信号的差值,于是噪声被抵消。由于两条信号线周围的电磁场也相互抵消,故差分信号传输比单线信号传输电磁辐射小得多。

此外,该传输标准采用电流模式驱动输出,不会产生振铃和信号切换所带来的尖峰信号,具有良好的EMI特性。

由于LVDS 差分信号技术降低了对噪声的关注,所以可以采用较低的信号电压幅度。这个特性非常重要,它使提高数据传输率和降低功耗成为可能。低驱动振幅意味着数据可更快地反转。

由于驱动器是恒流源模式,功耗几乎不会随频率而变化,而且单路的功耗非常低。

因此,采用这种技术后,只要保证一对平行传输线的长度足够一致,并在接受端提供良好的匹配端接阻抗技术,以减小反射信号的产生,就可以提供非常高的数据传输率。

目前,不用经过复杂和特殊的处理,提供 840MHZ 的数据传输速率已经非常容易。

LVDS 驱动和接收

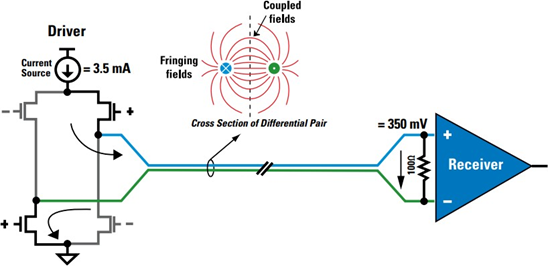

上图为LVDS 的工作原理示意图,其驱动器由个恒流源(通常为 3.5mA)驱动一对差分信号线组成。在接收端有一个高的直流输入阻抗(几乎不会消耗电流),所以几乎全部的驱动电流将流经 100欧的终端电阻在接收器输入端产生约 350mV的电压。

当驱动状态反转时,流经电阻的电流方向改变,于是在接收端产生一个有效的〞0〞或〞1〞逻辑状态。LVDS 技术特点包括:

1.高速传输能力,LVDS 的传输能力最高可达 2Gbps;

2.低电压、低功耗,LVDS 采用 CMOS 工艺实现,静态功耗较低;

3.低噪声辐射;

4.采用差分传输模式有较强的抗干扰能力;

LVDS 比传统的单端信号拓扑结构(如并行 LVTTL/LVCNOS) 有许多优点,主要优点包括 EMI(电磁干扰)减少,更快的数据速率更远的扩展传输距离和成本及便利性。

对于第 2 代和第 3 代 LVDS SerDes(串行器/解串器),另一个好处是通过 RBS(随机化,DC 平衡,加扰)编码提高系统可靠性和降低 EMI。静态的显示图像可以包括许多相同的颜色位,这可能产生 DC漂移并影响信号质量以及创造 EMI 峰值。RBS编码使数据随机化并加扰比特位的位置,移除静态模式并确保转换正确,然后通过平衡 DC来允许 AC耦合并提供隔离。这种编码的最终结果是抖动更小和通过更多的传输频谱扩展以降低 EMI。

数据速率,距离和成本/便利性

由于并行接口的数据速率非常有限,故数据速率是 LVDS 优于 LVTTL / LVCMOS的另一个好处。如前面所述,当许多输出并行传输时,每个信号传播越快,它产生的 EMI就越多。此外,信号间延时差也限制了信号可以传播的距离,在更快的数据速率下会变得更糟。而使用 LVDS,数据速率可以更高,距离也可以延长至超过 10米。由于长度匹配的考虑减少以及更多的使用空间, PCB 的设计也容易很多。

在设计过程中,请考虑以下几点:

• EMI

LVDS 信号滤波设计主要针对如时钟信号、总线信号做滤波设计,时钟信号在发送端增加 RC 滤波设计,减小时 钟对外的辐射干扰;针对差分信号,其滤波设计需在端口增加共模电感进行滤波抑制共模噪声。

LVDS 信号抗干扰设计分为固定路径干扰和环境干扰。

• 固定路径的干扰

干扰路径一般为电源或者信号线,故 LVDS 电路设计只需要在接口增加防护设计,接口增加磁珠吸收后对地增加电容,使干扰以最快的路径泄放掉。

• 环境干扰

这种干扰是由环境中外部源的电磁辐射引起的,通常使用诸如添加铁氧体磁珠和电容的保护措施来减少这种干扰的影响。

• 为了减少单端信号和 LVDS信号之间的串扰,应该遵循:

1.在同一 PCB 层上,单端信号距离 LVDS 信号至少 12 mm;

2.差分线之间的距离不应超过信号线宽度的两倍, 电路板的厚度应大于信号线之间的距离;

3.两个相邻差分对之间的距离应大于或者等于 2 倍独立信号线之间距离。

• 阻抗匹配

LVDS 信号设计阻抗匹配时,应遵循:

1.PCB至少为 4层板,LVDS信号和 TTL/CMOS信号需用电源层或地层进行隔离; LVDS的驱动器和接收器尽可能靠近连接器放置;

2.靠近驱动器或接收器 Vcc管脚处放置一个 4.7μF或 10μF 电容,且要考虑信号的工作频率和电容最佳工作频率的匹配性;

3.靠近一个驱动器或接收器 Vcc管脚处放置至少一个 0.1μF和一个 0.001μF电容;

4.电源和地线尽量地宽以降低电源回流阻抗。

来源于TI官网

- The End -

版权声明:欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为云脑智库。本公众号目前所载内容为本公众号原创、网络转载或根据非密公开性信息资料编辑整理,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系删除。我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。本公众号拥有对此声明的最终解释权。

投稿/招聘/推广/合作/入群/赞助 请加微信:15881101905,备注关键词

“阅读是一种习惯,分享是一种美德,我们是一群专业、有态度的知识传播者.”

↓↓↓ 戳“阅读原文”,加入“知识星球”,发现更多精彩内容.

分享💬 点赞👍 在看❤️@以“三连”行动支持优质内容!