常常听说哪里哪里需要50欧姆,100欧姆的阻抗控制,有的同学很认真,拿来万用表一阵量,感觉好像各种线缆测量值都不大达标,一通抱怨。也有不那么认真的同学,觉得阻抗匹配什么的就是那么回事儿,我的板子跑个七八百M不也杠杠得,没出啥问题吗。

嗯,没出问题挺好的。我们今天还是聊一聊什么是阻抗,和阻抗如何匹配的问题。

我们知道最基本的元器件有三种:电阻,电感和电容。

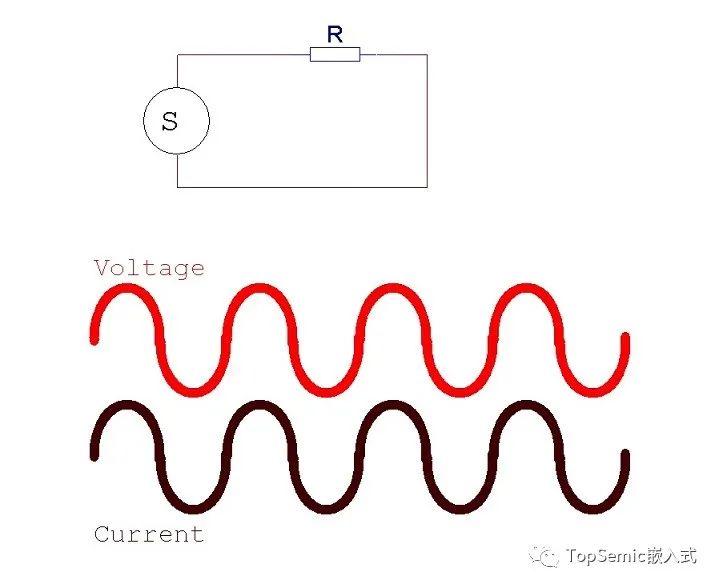

我们最熟悉的是电阻,初中物理就开始讲了。对纯电阻来说,流过它的电流,随着施加在它两端的电压大小而变化。I=U/R

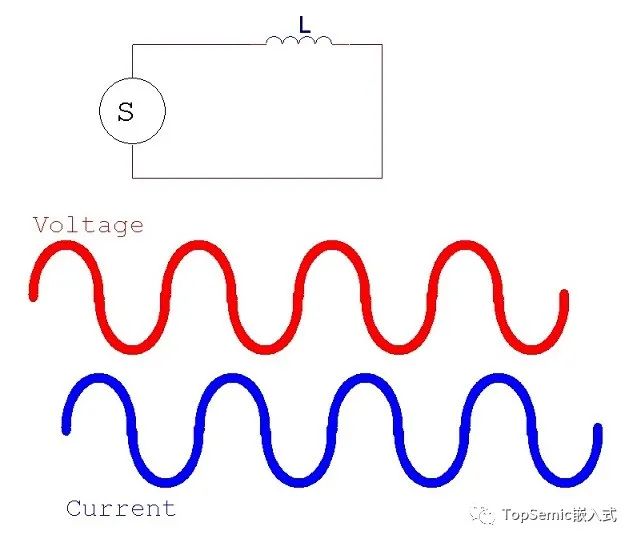

对于电感来说,流经它的电流不能突变,它的电流会比电压落后90°。为了表达这种相位上的超前或之后,它的阻抗引入了虚数。感抗XL = jωL,j表达了电流会落后电压90°,角频率ω= 2πf。感抗随着频率的升高而变大。

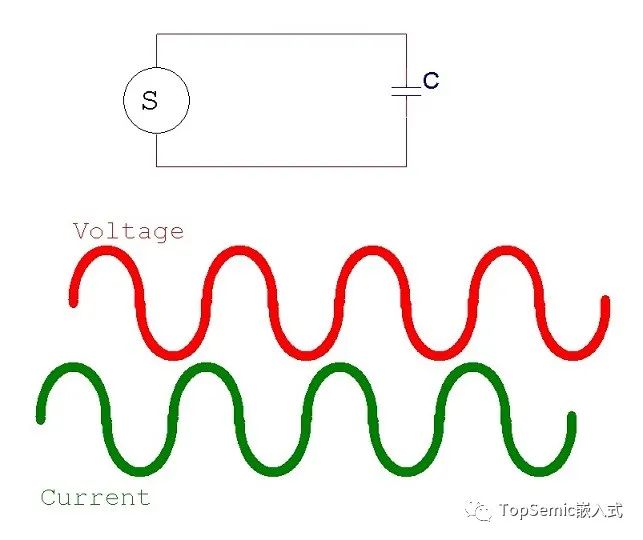

对于电容,电极板两端的电压不能突变,它的电流会比电压超前90°。容抗XC = 1/jωC,它随着频率的升高而变小。

如果电路中有这三种元件,那么总的阻抗Z不是一个固定的值,而是和信号频率有关系。如果感抗和容抗正好相等,整体上呈现纯电阻。如果感抗大于容抗,整体上则呈现感性,反之呈现容性。

对于这三种元件,你会发现,学的越多,理解起来就越复杂。如果我们看一下一些大牛们推导公式的过程,不由会产生,吾生也有涯,而知也无涯的感慨。

根据我们要达到的不同目的,阻抗匹配也可以有不同的理解。比如说一个直流或低频信号源,通过导线连至负载,如果我们的目的是让负载得到最大功率,在这种情况下,导线的电阻可以忽略,可以推导出,当负载的电阻和信号源内阻相等时,负载得到最大功率。

随着信号频率的升高,信号源内阻和负载的感抗和容抗开始无法忽略,此时如果想要在负载得到最大功率,需要内阻和负载的电阻相等,电抗大小相等且方向相反。即共轭匹配。

以上都是信号源频率比较低的情况,或者说信号波长远大于导线的情况。当频率继续升高,波长小到跟导线长度达到一个数量级,甚至波长小于导线长度,此时传输导线的阻抗就不能被忽略了。当然在这么高的频率,我们的目的一般不会是让负载得到最大功率,而是把信号源的波形,完美地传送到负载。高速数字电路设计中,我们通常说的是这种阻抗匹配,它的目的是防止信号反射,保持信号的完整性。

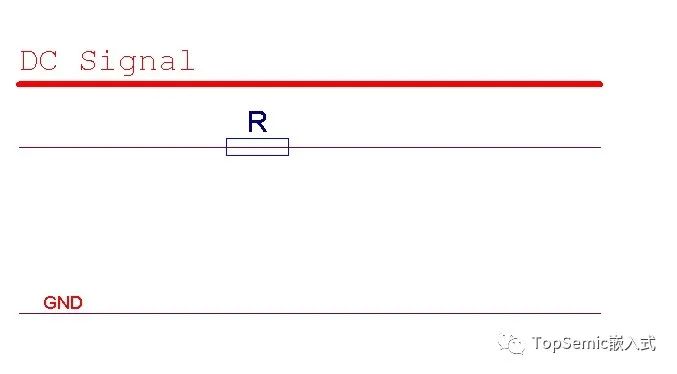

对于直流或低频信号,我们可以认为导线是非常小的纯电阻,所以导线上电压,可以认为处处相等,电流也处处相等。

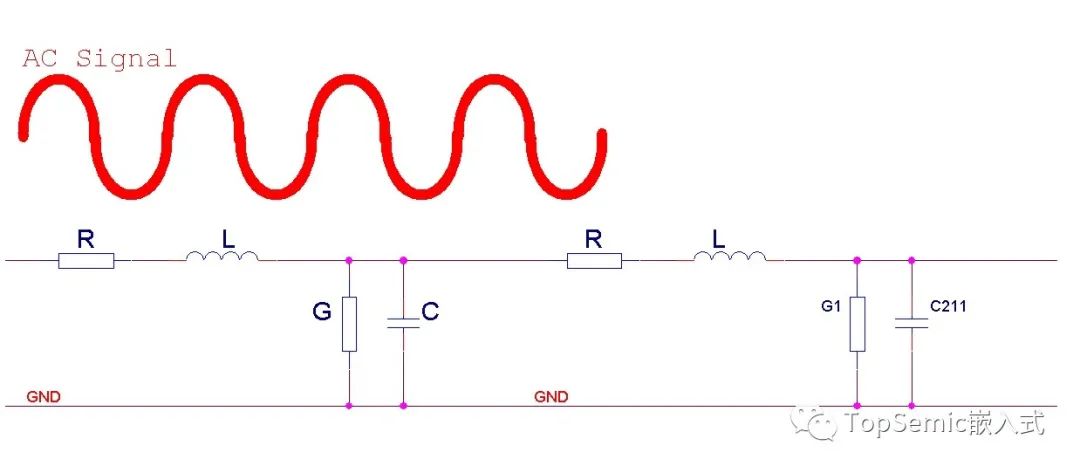

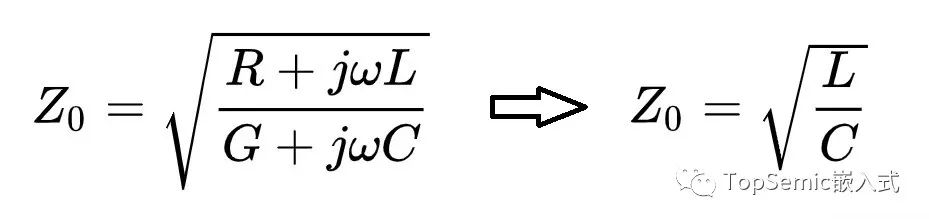

对于高频信号,同样的一段导线,不能再被看作纯电阻,而是如上图存在寄生电感,与地线存在寄生电容,跨导。在这种情况下,信号沿导线传播时受到的阻力,和导线的长度就没关系了,只跟单位长度导线的电阻,跨导,寄生电感电容,和信号频率有关。频率越高,感抗和容抗越起到主导作用,忽略掉R和G,导线的特征阻抗变为右边的形式,它只跟导线的寄生电感和电容相关。

下面我们来看看在实际电路板中如何做阻抗控制。

先熟悉一个概念:介电常数,因为它会影响特征阻抗。

介电常数(Dielectric Constant),这个数值可以表示一种材料贮存电荷能力的大小。

我们知道电容的大小,与电容两个极板间填充的物质有关。通常拿真空作为一个基准,其它物质与它作比较得出一个相对数值。假设一个电容在真空中的大小是C0,把物质X填入电容的两个极板之间后,电容变为Cx,那么这种物质的介电常数就是E=Cx/C0。

常见物质介电常数:

真空 1

空气 1.000585

玻璃片 1.2 -- 2.2

乙醇 2.5

冰 3.2

石英 4.3

FR4 4 -- 4.7

水 81.5

Er越高,高频信号越容易通过,即高频的损耗越大。为减小高频损耗,可以选用一些Er值低的PCB板,当然成本会高一些。

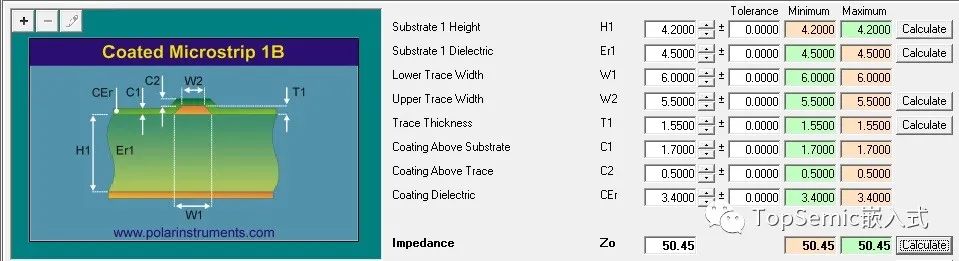

现在我们看一下实际例子,用工具软件计算走线的阻抗值。阻抗计算比较常用的是Polar si9000,它是一款收费软件。

好的阻抗控制,需要紧邻布线层有一个完整的参考平面,可以是GND层,也可以是POWER层。当然也可以两面都有参考面。下面是4种比较典型的布线方式:

Coated Microstrip 带阻焊的微带线

这是PCB的横截面,上面是布线层,下面是参考面。我们看到计算阻抗需要填入一些参数:

Substrate 1 Height H1 导线到参考面的距离

Substrate 1 Dielectric Er1 基板介电常数

Lower Trace Width W1 走线下端宽度

Upper Trace Width W2 走线上端宽度

Trace Thickness T1 走线铜厚度

Coating Above Substrate C1 基板绿油厚度

Coating Above Trace C2 走线覆盖绿油厚度

Coating Dielectric CEr 绿油介电常数

Impedance Z0 即计算出的阻抗

Edge-Coupled Coated Microstrip 带阻焊的差分微带线

多了两条走线之间的距离S1,绿油C3。

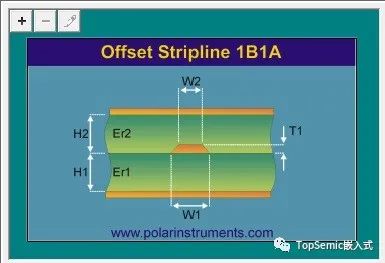

Offset Stripline 带状线

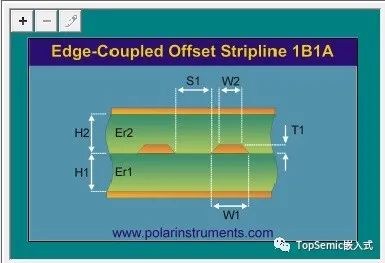

Edge-Coupled Offset Stripline 差分带状线

高速数字电路中,保证阻抗的连续性很重要,因为在阻抗不连续的地方一定会发生信号反射。所以走线宽度一直要保持一致,尽量不要过孔。差分对线间距要保持不变,如果用过孔一定要成对出现,而且在参考平面也要打过孔。

一般来说,单端用50欧,差分用100欧。

1000M/100M以太网,HDMI,SATA 差分100欧姆。

对DDR3 存储器来说,时钟线和控制线(CE#, WE#, OE#, and WAIT#)是必须要做阻抗匹配的,地址线和数据线对阻抗匹配要求稍低一些。

USB3.0/2.0 差分90欧姆。

对于RF射频天线上的模拟信号,需要做共轭匹配,常用阻抗是50欧姆。

推荐阅读

添加微信回复“进群”

拉你进技术交流群!

国产芯|汽车电子|物联网|新能源|电源|工业|嵌入式…..

在公众号内回复您想搜索的任意内容,如问题关键字、技术名词、bug代码等,就能轻松获得与之相关的专业技术内容反馈。快去试试吧!

如果您想经常看到我们的文章,可以进入我们的主页,点击屏幕右上角「三个小点」,点击「设为星标」。

欢迎扫码关注