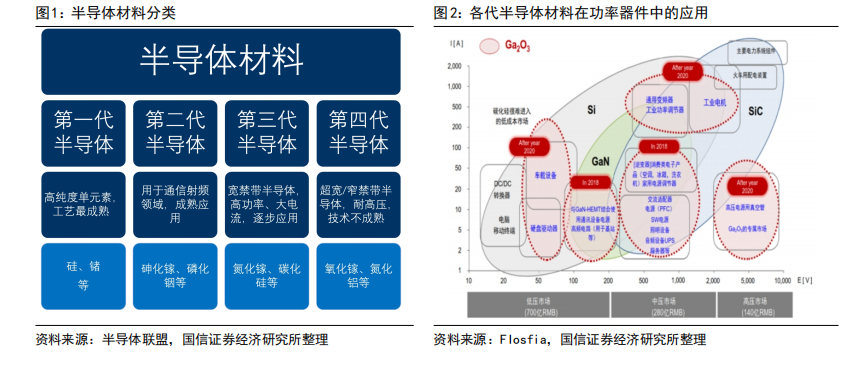

本文参考自“国信证券:半导体系列报告”。半导体材料是一类具有半导体性能(导电能力介于导体与绝缘体之间)、可用来 制作半导体器件和集成电路的电子材料,是半导体工业的基础。半导体材料的研 究始于 19 世纪,至今已发展至第四代半导体材料,各个代际半导体材料之间互相补充。

下载链接:

国信证券:半导体系列报告

第一代半导体:以硅(Si)、锗(Ge)等为代表,是由单一元素构成的元素 半导体材料。硅半导体材料及其集成电路的发展导致了微型计算机的出现和 整个信息产业的飞跃。

第二代半导体:以砷化镓(GaAs)、磷化铟(InP)等为代表,也包括三元化 合物半导体,如 GaAsAl、GaAsP,还包括一些固溶体半导体、非静态半导体 等。随着以光通信为基础的信息高速公路的崛起和社会信息化的发展,第二 代半导体材料显示出其优越性,砷化镓和磷化铟半导体激光器成为光通信系 统中的关键器件,同时砷化镓高速器件也开拓了光纤及移动通信的新产业。

第三代半导体:以氮化镓(GaN)、碳化硅(SiC)、氧化锌(ZnO)为代表的 宽禁带半导体材料。具备高击穿电场、高热导率、高电子饱和速率及抗强辐 射能力等优异性能,更适合于制作高温、高频、抗辐射及大功率电子器件, 在半导体照明、新一代移动通信、能源互联网、高速轨道交通、新能源汽车、 消费类电子等领域有广阔的应用前景。

硅材料制造全球绝大部分的半导体产品,也是占比最大的半导体制造材料。在 1950 年代初期,锗是主要的半导体材料。但锗半导体器件的耐高温和抗辐射性能 较差,到 1960 年代逐渐被硅材料取代。由于硅器件的漏电流要低得多,且二氧化 硅是一种高质量的绝缘体,很容易作为硅器件的一部分进行整合,至今半导体器 件和集成电路仍然主要用硅材料制成,硅产品构成了全球绝大部分半导体产品。

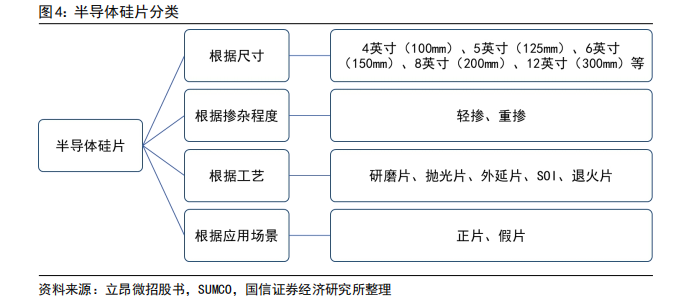

半导体硅晶圆(Semiconductor Silicon Wafer)是制造硅半导体产品的基础,可 根据不同参数进行分类。

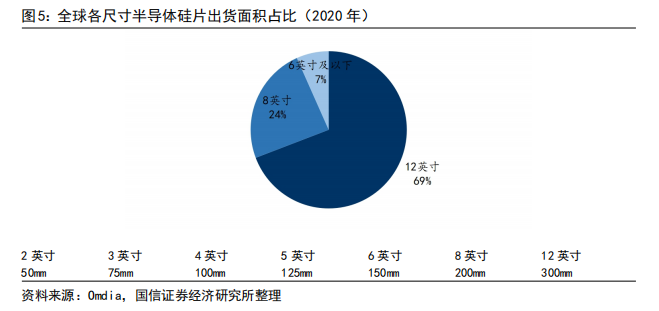

根据尺寸(直径)不同,半导体硅片可分为 2英寸(50mm)、3英寸(75mm)、4英寸(100mm)、5英寸(125mm)、6英寸(150mm)、8英寸(200mm)、12英寸 (300mm),在摩尔定律影响下,半导体硅片正在不断向大尺寸的方向发展,目前 8 英寸和 12 英寸是主流产品,合计出货面积占比超过90%。

根据掺杂程度不同,半导体硅片可分为轻掺和重掺。重掺硅片的掺杂元素掺入量 大,电阻率低,一般用于功率器件等产品;轻掺硅片掺杂浓度低,一般用于集成电 路领域,技术难度和产品质量要求更高。由于集成电路在全球半导体市场中占比 超过 80%,全球对轻掺硅片需求更大。

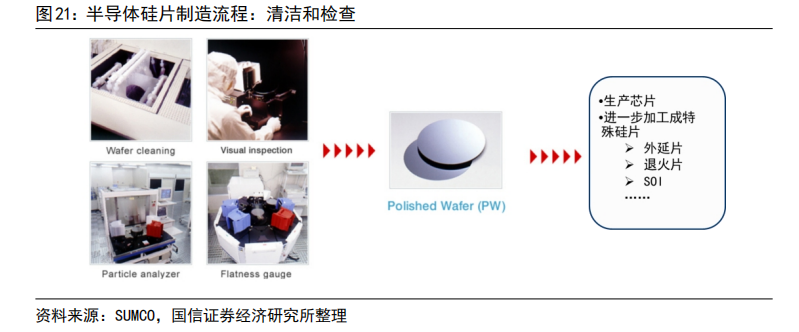

根据工艺,半导体硅片可分为研磨片、抛光片及基于抛光片制造的特殊硅片外延 片、SOI 等。研磨片可用于制造分立器件;轻掺抛光片可用于制造大规模集成电 路或作为外延片的衬底材料,重掺抛光片一般用作外延片的衬底材料。相比研磨 片,抛光片具有更优的表面平整度和洁净度。

在抛光片的基础上,可以制造出退火片、外延片、SOI 硅片和结隔离硅片等。退 火片在氢气或氩气环境下对抛光片进行高温热处理,以去除晶圆表面附近的氧气, 可以提高表面晶体的完整性。外延片是在抛光片表面形成一层气相生长的单晶硅, 可 满 足 需 要 晶 体 完 整 性 或 不 同 电 阻 率 的 多 层 结 构 的 需 求 。SOI 硅 片 (Silicon-On-Insulator)是在两个抛光片之间插入高电绝缘氧化膜层,可以实 现器件的高集成度、低功耗、高速和高可靠性,在活性层表面也可以形成砷或砷 的扩散层。结隔离硅片是根据客户的设计,利用曝光、离子注入和热扩散技术在 晶圆表面预形成 IC 嵌入层,然后再在上面生长一层外延层。

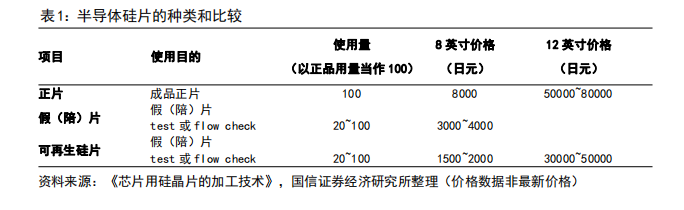

根据应用场景不同,半导体硅片可分为正片、假(陪)片。正片(Prime Wafer) 用于半导体产品的制造,假片(Dummy Wafer)用来暖机、填充空缺、测试生产设 备的工艺状态或某一工艺的质量状况。假片一般由晶棒两侧品质较差部分切割而 来,由于用量巨大,在符合条件的情况下部分产品会回收再利用,回收重复利用 的硅片称为可再生硅片(Reclaimed Wafer)。据观研网数据,65nm 制程的晶圆 代工厂每 10 片正片需要加 6 片假片,28nm 及以下制程每 10 片正片则需要加 15-20 片假片。

半导体硅片制造流程复杂,主要包括拉单晶和硅片的切磨抛外延等工艺。半导体 硅片的生产流程复杂,涉及工序较多。研磨片工序包括拉单晶、截断、滚圆、切 片、倒角、研磨等,抛光片是在研磨片的基础上经边缘抛光、表面抛光等工序制 造而来;抛光片经外延工艺制造出硅外延片,经退火热处理制造出硅退火片,经 特殊工艺制造出绝缘体上硅 SOI。硅片制造过程中需要经过多次清洗,在销售给 客户之前还需要经过检验和包装。

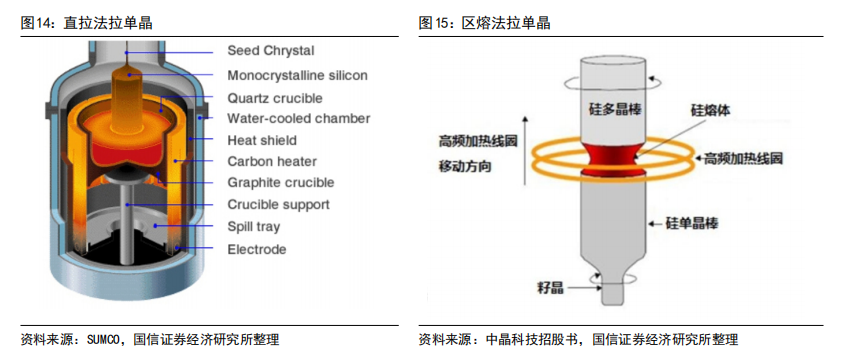

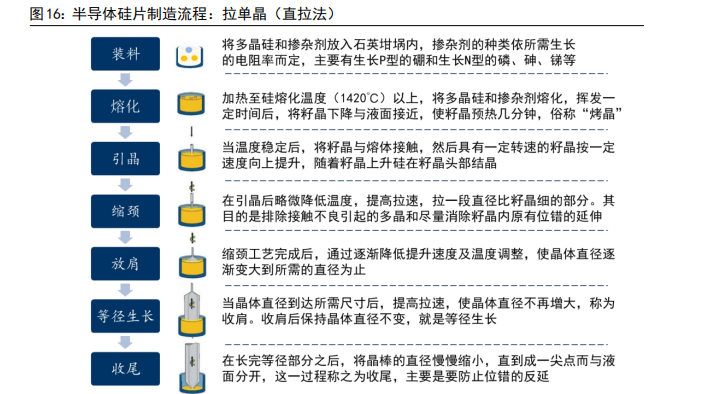

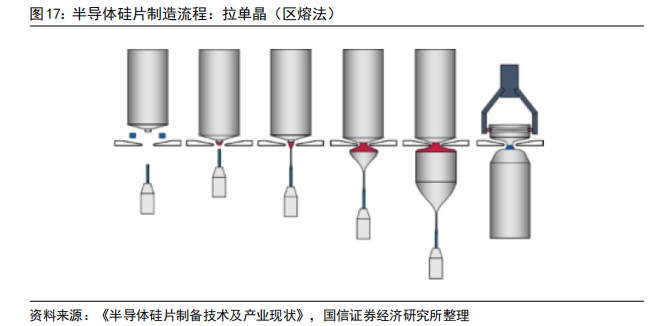

步骤一:拉单晶。电子级高纯度多晶硅通过单晶生长工艺可拉制成单晶硅棒,常 用方法有直拉法(Czochralsk,CZ 法)和区熔法(Float-Zone,FZ 法)两种。FZ 法纯度高,氧含量低,电阻率较高,能耐高压,但工艺难度大,大尺寸硅片制备 困难且成本高,因此主要以 8 英寸及以下尺寸为主,主要用于中高端功率器件。CZ 法氧含量高,更容易生产出大尺寸单晶硅棒,工艺也已成熟,成本较低,因此 目前半导体行业主要采用 CZ 法拉制单晶硅棒。拉单晶技术直接决定了位错、COP (crystal originated pit,晶体原生凹坑)、旋涡等晶体原生缺陷的密度及电 阻率、电阻率梯度、氧、碳含量等晶体技术指标的好坏,是半导体硅片生产工序 中最为核心的技术。

装料:将多晶硅和掺杂剂放入单晶炉内的石英坩埚内,掺杂剂的种类依所需 生长的电阻率而定,主要有生长 P 型的硼和生长 N 型的磷、砷、锑等。

熔化:装料结束后,加热至硅熔化温度(1420℃)以上,将多晶硅和掺杂剂熔化,挥发一定时间后,将籽晶下降与液面接近,使籽晶预热几分钟,俗称 “烤晶”,以除去表面挥发性杂质同时可减少热冲击。

引晶:当温度稳定后,将籽晶与熔体接触,然后具有一定转速的籽晶按一定 速度向上提升,随着籽晶上升硅在籽晶头部结晶,称为“引晶”或“下种”。

缩颈:在引晶后略微降低温度,提高拉速,拉一段直径比籽晶细的部分。其 目的是排除接触不良引起的多晶和尽量消除籽晶内原有位错的延伸。颈一般 要长于 20mm。

放肩:缩颈工艺完成后,通过逐渐降低提升速度及温度调整,使晶体直径逐 渐变大到所需的直径为止。在放肩时可判别晶体是否是单晶,否则要将其熔 掉重新引晶。

等径生长:当晶体直径到达所需尺寸后,提高拉速,使晶体直径不再增大, 称为收肩。收肩后保持晶体直径不变,就是等径生长。此时要严格控制温度 和拉速不变。单晶硅片取自于等径部分。

收尾:在长完等径部分之后,如果立刻将晶棒与液面分开,那么效应力将使 得晶棒出现位错与滑移线。于是为了避免此问题的发生,必须将晶棒的直径 慢慢缩小,直到成一尖点而与液面分开。这一过程称之为收尾阶段。长完的 晶棒被升至上炉室冷却一段时间后取出,即完成一次生长周期。

步骤二:切片。单晶硅棒磨成相同直径,然后根据客户要求的电阻率,用内径锯 或线锯将晶棒切成约 1mm 厚的薄片,形成晶圆。根据目前的工艺、技术水平,为 了降低硅材料的损耗、提高生产效率和表面质量,一般采用线切割方法进行切片。

步骤三:倒角。硅片倒角加工的目的是消除硅片边缘表面经切割加工所产生的棱 角、裂缝、毛刺、崩边或其他的缺陷以及各种边缘表面污染,从而降低硅片边缘 表面的粗糙度,增加硅片边缘表面的机械强度、减少颗粒的表面沾污。

步骤四:研磨。在研磨机上用磨料将切片抛光到所需的厚度,同时提高表面平整 度。研磨的目的是为了去除在切片工序中,硅片表面因切割产生的深度约 20~25um 的表面机械应力损伤层和表面的各种金属离子等杂质污染,并使硅片具有一定的 平坦表面。

步骤五:蚀刻和抛光。通过化学蚀刻去除前面步骤对晶圆表面造成的机械损伤, 然后采用硅溶胶机械化学抛光法使晶圆表面更加平整和光洁。

步骤六:清洁和检查。清洁后,对产品进行严格的质量检查,合格后销售给客户。也可进一步用来制作 SOI、外延片等特殊硅片。

下载链接:

国信证券:半导体系列报告

AI框架发展白皮书(2022年)

2022中国AI芯片行业研究报告

40张图表解析中国“芯”势力

光刻胶研究框架2.0:行业深度报告

半导体研究框架:详解八大芯片材料(2022)

半导体2022年策略:国产化4.0+电动化 2.0

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

电子书<服务器基础知识全解(终极版)>更新完毕。

获取方式:点击“阅读原文”即可查看182页 PPT可编辑版本和PDF阅读版本详情。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。